半导体晶圆结构及其形成方法.pdf

篷璐****爱吗

亲,该文档总共45页,到这已经超出免费预览范围,如果喜欢就直接下载吧~

相关资料

半导体晶圆结构及其形成方法.pdf

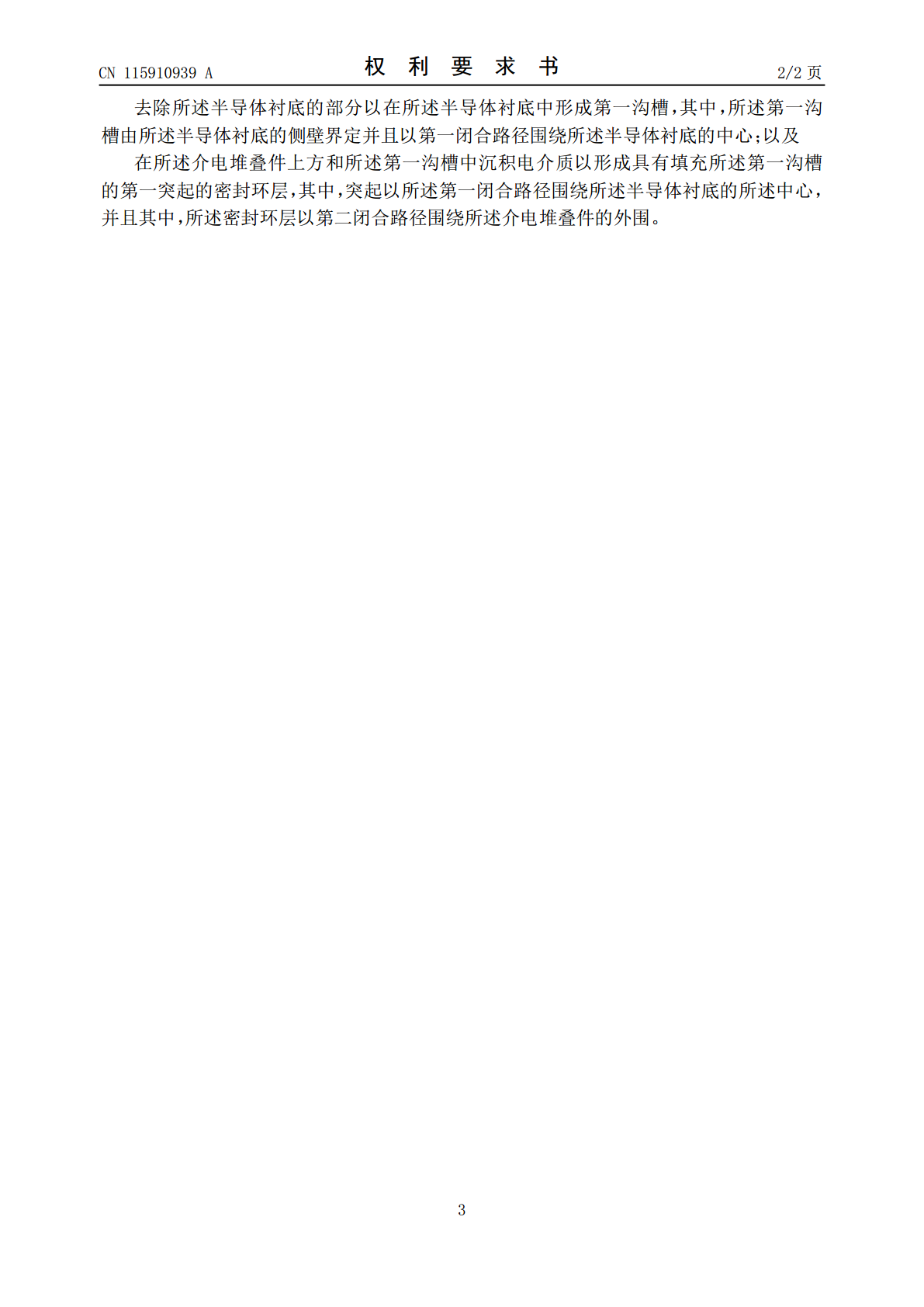

本发明涉及包括半导体衬底以及沿半导体衬底设置的多个半导体器件的半导体晶圆结构。包括多个介电层的介电堆叠件布置在半导体衬底上方。导电互连结构位于介电堆叠件内。密封环层位于介电堆叠件上方并且沿介电堆叠件的第一侧壁横向围绕介电堆叠件。密封环层包括延伸至半导体衬底中的第一沟槽中的第一突起。本申请的实施例还涉及半导体晶圆结构及其形成方法。

晶圆接合结构及其形成方法.pdf

本发明实施例提供一种晶圆接合结构及其形成方法。晶圆接合结构的形成方法包括形成第一晶圆以及将第二晶圆接合到第一晶圆的接合介电层及接合垫。形成第一晶圆包括以下工艺。提供半导体结构,半导体结构的边缘具有第一塌边区域。形成附加介电层,以填补第一塌边区域。在半导体结构及附加介电层上形成具有开口的接合介电层。形成导电层于接合介电层上并填入开口中,其中在附加介电层上方的导电层具有凸起。进行移除工艺,以移除位于接合介电层上的导电层,余留在开口中的导电层形成接合垫,其中移除工艺包括平坦化工艺,且凸起被平坦化工艺移除。

SOI结构的半导体硅晶圆及其制备方法.pdf

本发明提供了一种SOI结构的半导体硅晶圆及其制备方法,属于半导体制造领域,具体包括步骤一,将半导体硅晶圆置于第一垂直炉管进行长时间热处理;步骤二,将长时间热处理后的所述半导体硅晶圆放入第二垂直炉管中,进行氧化减薄处理;步骤三,对氧化减薄后的所述半导体硅晶圆进行快速热退火处理,其中,在长时间热处理中,先将所述半导体硅晶圆置于纯氩气氛中进行保护,而后在1?n%氩气+n%氢气的混合气氛升温至目标温度再进行退火阶段,退火阶段,气氛为1?n%氩气+n%氢气的混合气氛或者纯氩气,n为不大于10的数值。通过本申请的处理

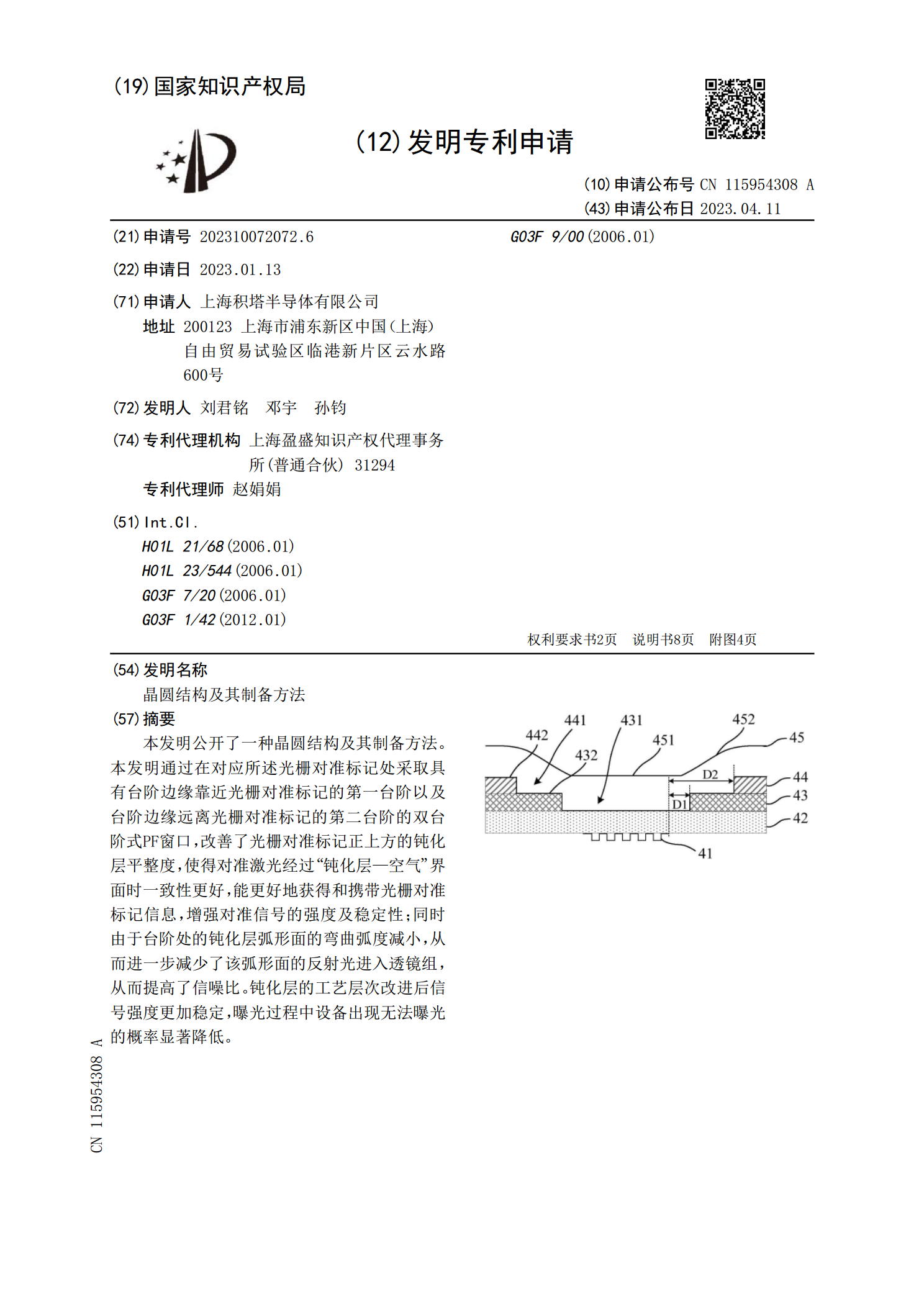

晶圆结构及其制备方法.pdf

本发明公开了一种晶圆结构及其制备方法。本发明通过在对应所述光栅对准标记处采取具有台阶边缘靠近光栅对准标记的第一台阶以及台阶边缘远离光栅对准标记的第二台阶的双台阶式PF窗口,改善了光栅对准标记正上方的钝化层平整度,使得对准激光经过“钝化层—空气”界面时一致性更好,能更好地获得和携带光栅对准标记信息,增强对准信号的强度及稳定性;同时由于台阶处的钝化层弧形面的弯曲弧度减小,从而进一步减少了该弧形面的反射光进入透镜组,从而提高了信噪比。钝化层的工艺层次改进后信号强度更加稳定,曝光过程中设备出现无法曝光的概率显著降

半导体结构及其形成方法、堆叠结构及其形成方法.pdf

本公开实施例提供一种半导体结构及其形成方法、堆叠结构及其形成方法,其中,所述半导体结构的形成方法包括:提供初始基底;所述初始基底至少包括初始后道工序层、位于所述初始后道工序层上且具有第一凹槽的初始布线层;沿所述第一凹槽刻蚀所述初始基底,形成布线层和通孔;在所述通孔中填充导电材料,形成与所述布线层连通的导电柱。