半导体器件及其制作方法.pdf

宏硕****mo

亲,该文档总共19页,到这已经超出免费预览范围,如果喜欢就直接下载吧~

相关资料

半导体器件及其制作方法.pdf

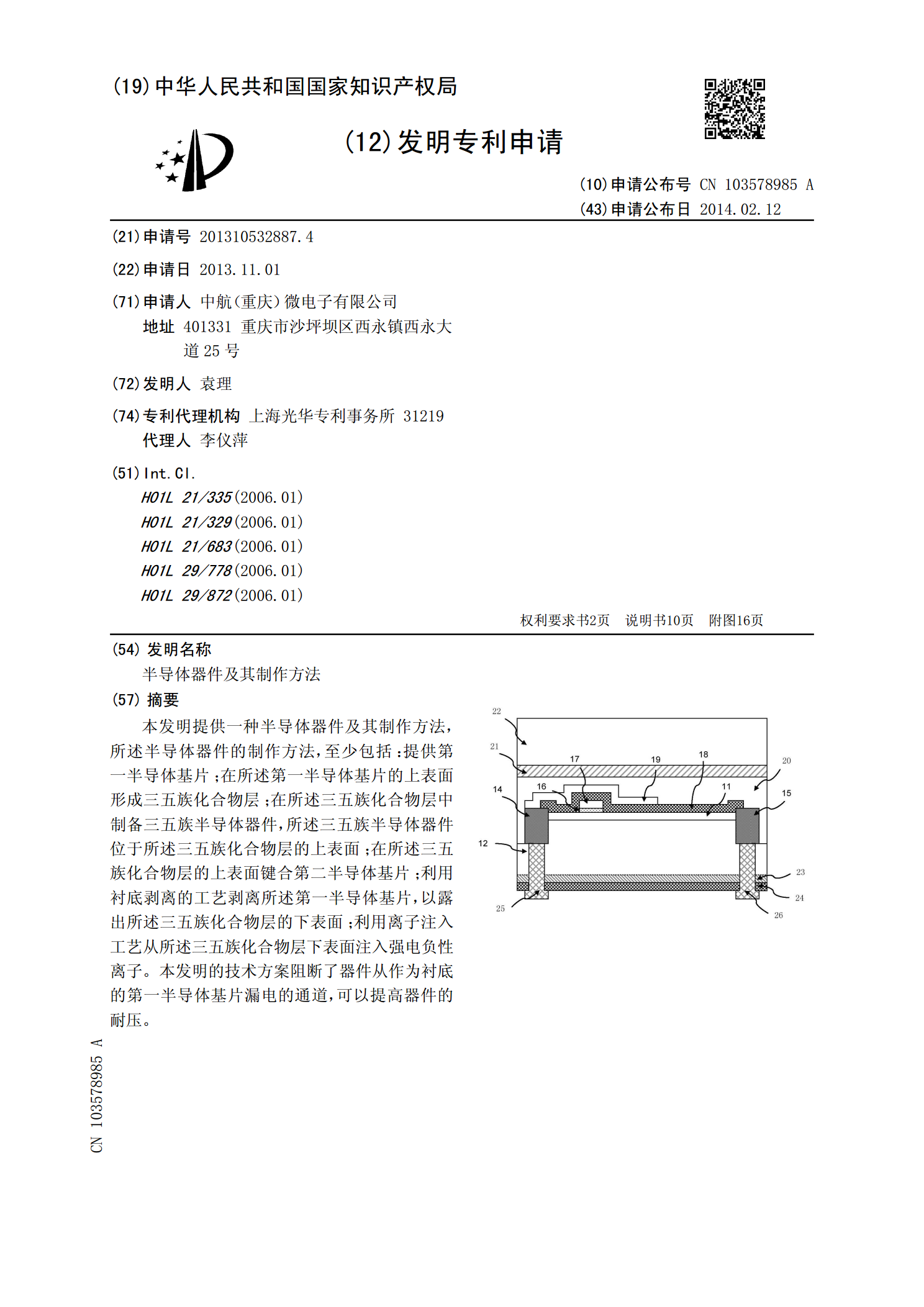

本发明提供一种半导体器件及其制作方法,所述半导体器件的制作方法,至少包括:提供第一半导体基片;在所述第一半导体基片的上表面形成三五族化合物层;在所述三五族化合物层中制备三五族半导体器件,所述三五族半导体器件位于所述三五族化合物层的上表面;在所述三五族化合物层的上表面键合第二半导体基片;利用衬底剥离的工艺剥离所述第一半导体基片,以露出所述三五族化合物层的下表面;利用离子注入工艺从所述三五族化合物层下表面注入强电负性离子。本发明的技术方案阻断了器件从作为衬底的第一半导体基片漏电的通道,可以提高器件的耐压。

半导体器件及其制作方法.pdf

本发明提供了一种半导体器件及其制作方法,所述方法包括:提供一衬底,所述衬底上形成有顶层金属层;在所述顶层金属层上形成钝化层,所述钝化层包含依次层叠的第一氧化物层、氮化物层与第二氧化物层。本发明通过将钝化层设置为氧化物、氮化物与氧化物三层层叠的结构来减小所述钝化层的应力,从而提高所述钝化层抵抗外界应力的能力,以避免所述顶层金属层变厚时在所述钝化层中产生裂纹,从而提高产品的可靠性。

半导体器件及其制作方法.pdf

本发明涉及一种半导体器件的制作方法,包括以下步骤:提供半导体结构,半导体结构包括由第一材料层和第二材料层交替堆叠的堆叠结构,堆叠结构包括平台区和与平台区相邻的台阶区,平台区和台阶区的顶部为第二材料层;形成覆盖平台区上表面和台阶区表面的第三材料层;形成填充台阶区且覆盖平台区的第四材料层;去除平台区上的第三材料层和第四材料层,且保留位于平台区上靠近台阶区的边缘的第三材料层和第四材料层;进行第一次平坦化,第一次平坦化去除凸起的第四材料层,且停留在平台区上表面的第二材料层和第三材料层。该制作方法增大了接触孔的连接

半导体器件及其制作方法.pdf

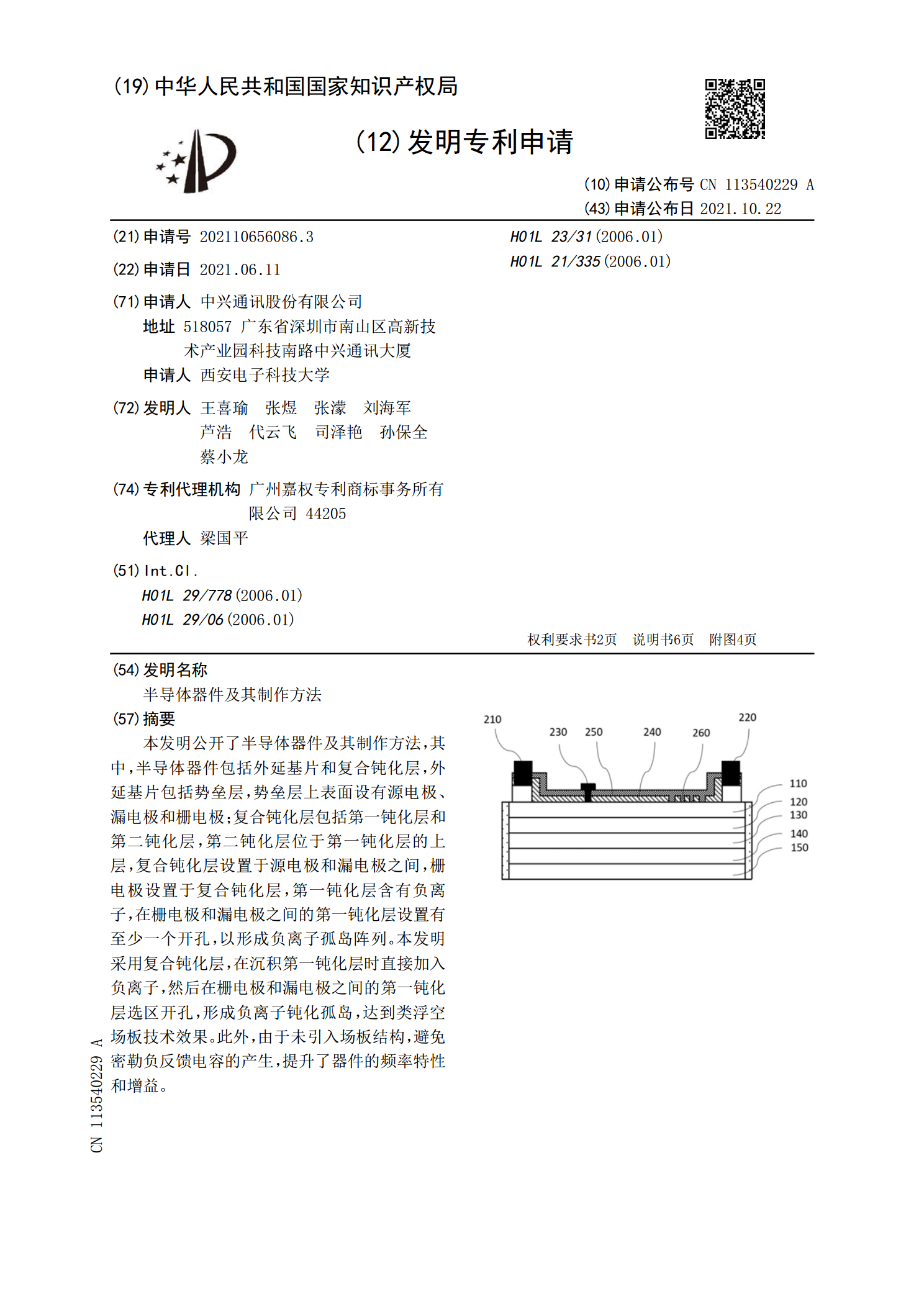

本发明公开了半导体器件及其制作方法,其中,半导体器件包括外延基片和复合钝化层,外延基片包括势垒层,势垒层上表面设有源电极、漏电极和栅电极;复合钝化层包括第一钝化层和第二钝化层,第二钝化层位于第一钝化层的上层,复合钝化层设置于源电极和漏电极之间,栅电极设置于复合钝化层,第一钝化层含有负离子,在栅电极和漏电极之间的第一钝化层设置有至少一个开孔,以形成负离子孤岛阵列。本发明采用复合钝化层,在沉积第一钝化层时直接加入负离子,然后在栅电极和漏电极之间的第一钝化层选区开孔,形成负离子钝化孤岛,达到类浮空场板技术效果。

半导体器件及其制作方法.pdf

本公开实施例公开了一种半导体器件的制作方法,包括以下步骤:提供半导体结构,半导体结构包括由第一材料层和第二材料层交替堆叠的堆叠结构,堆叠结构包括平台区和与平台区相邻的台阶区,平台区和台阶区的顶部为第二材料层;形成覆盖平台区上表面和台阶区表面的第三材料层;形成填充台阶区且覆盖平台区的第四材料层;去除平台区上的第三材料层和第四材料层,且保留位于平台区上靠近台阶区的边缘的第三材料层和第四材料层;进行第一次平坦化,第一次平坦化去除凸起的第四材料层,且停留在平台区上表面的第二材料层和第三材料层。该制作方法增大了接触