半导体集成电路器件.pdf

是你****优呀

亲,该文档总共19页,到这已经超出免费预览范围,如果喜欢就直接下载吧~

相关资料

半导体集成电路器件.pdf

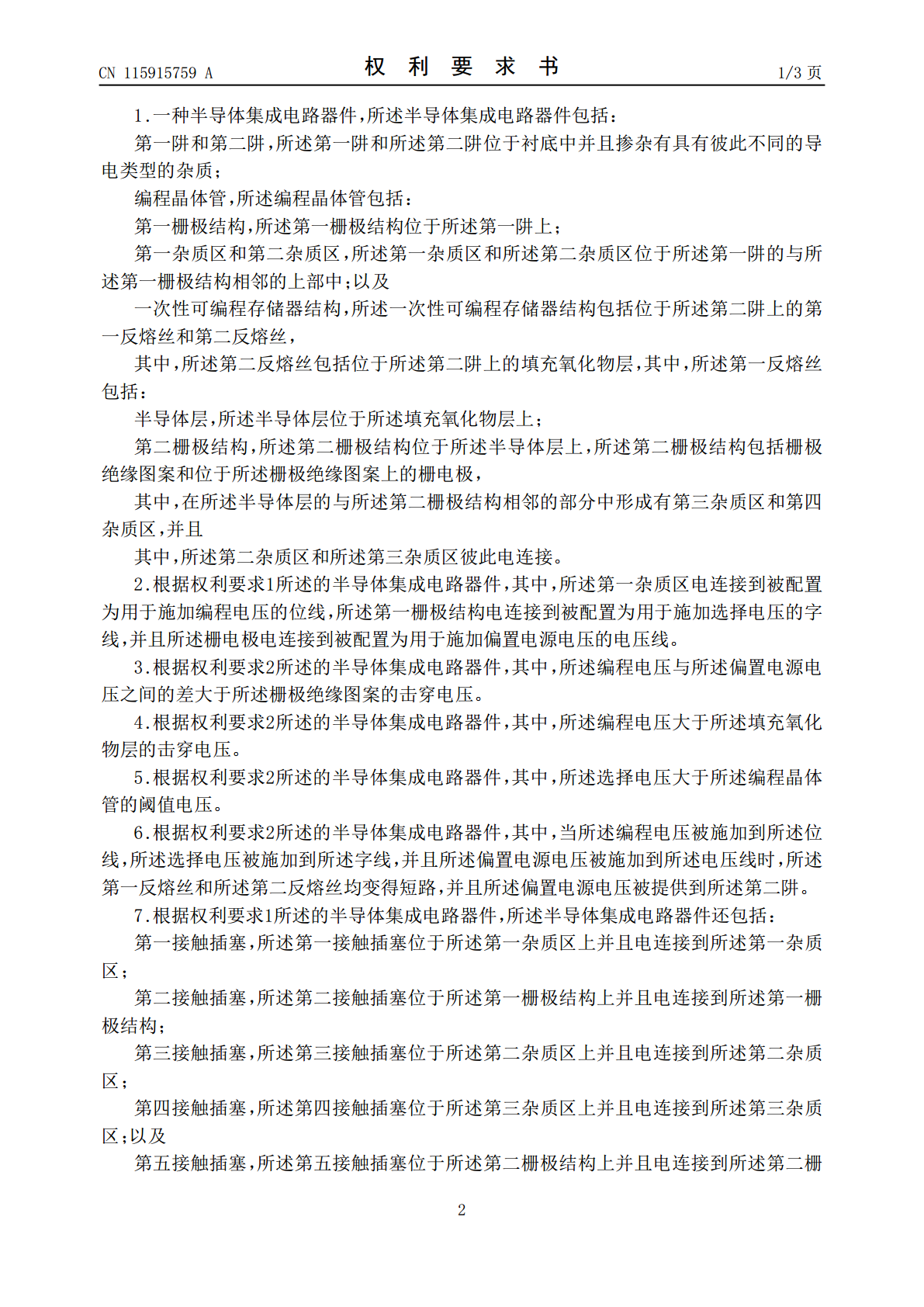

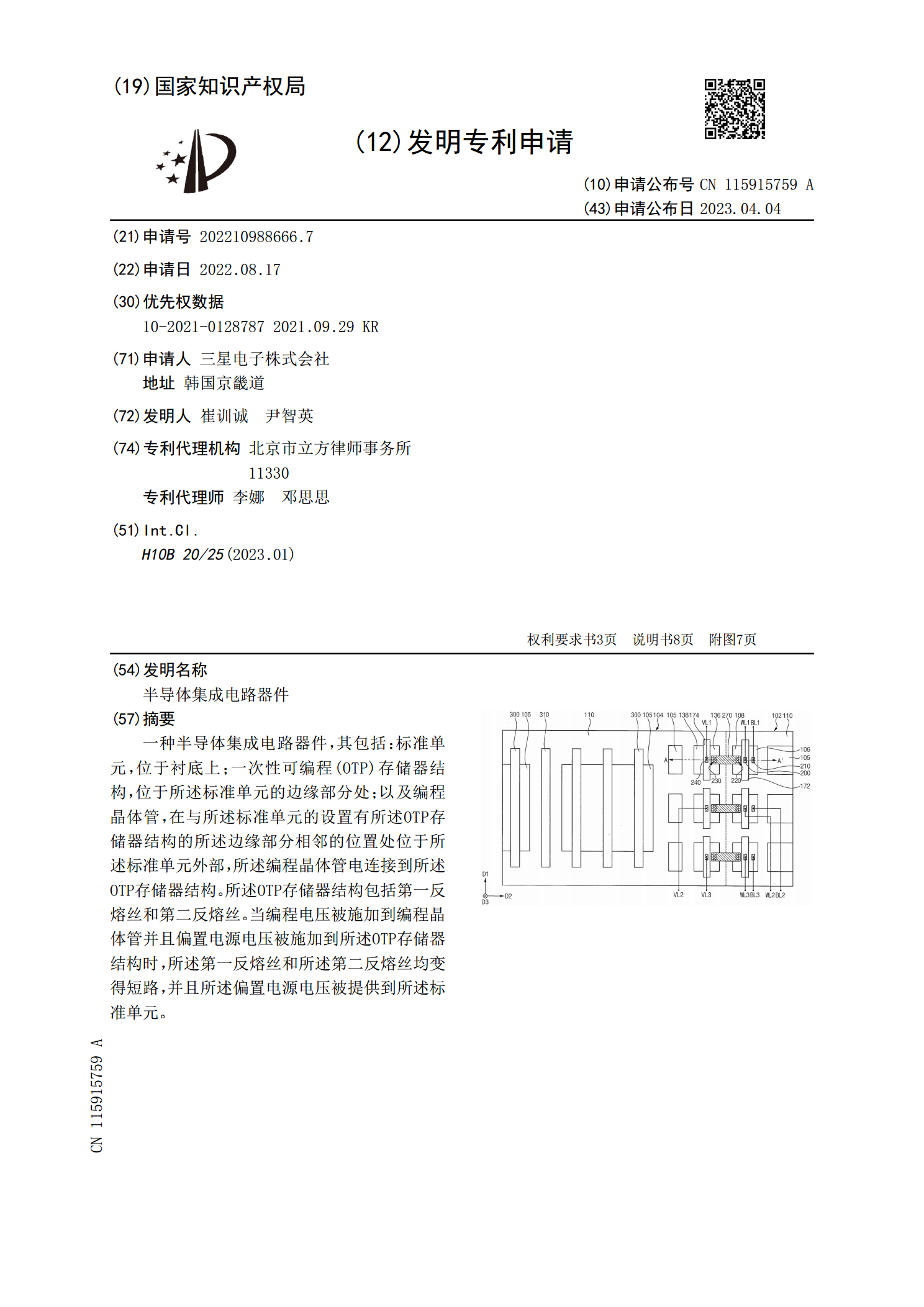

一种半导体集成电路器件,其包括:标准单元,位于衬底上;一次性可编程(OTP)存储器结构,位于所述标准单元的边缘部分处;以及编程晶体管,在与所述标准单元的设置有所述OTP存储器结构的所述边缘部分相邻的位置处位于所述标准单元外部,所述编程晶体管电连接到所述OTP存储器结构。所述OTP存储器结构包括第一反熔丝和第二反熔丝。当编程电压被施加到编程晶体管并且偏置电源电压被施加到所述OTP存储器结构时,所述第一反熔丝和所述第二反熔丝均变得短路,并且所述偏置电源电压被提供到所述标准单元。

集成电路半导体器件.pdf

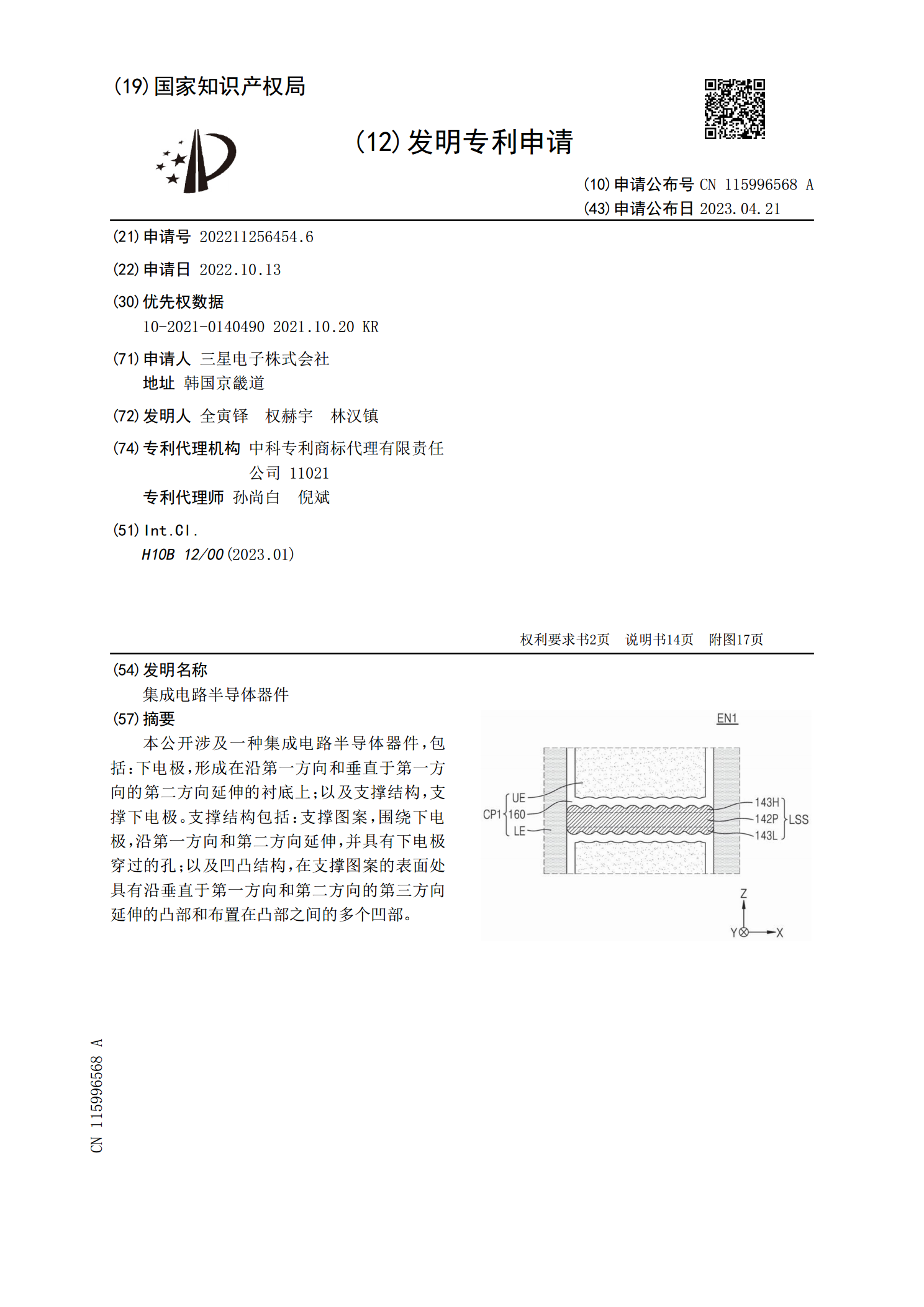

本公开涉及一种集成电路半导体器件,包括:下电极,形成在沿第一方向和垂直于第一方向的第二方向延伸的衬底上;以及支撑结构,支撑下电极。支撑结构包括:支撑图案,围绕下电极,沿第一方向和第二方向延伸,并具有下电极穿过的孔;以及凹凸结构,在支撑图案的表面处具有沿垂直于第一方向和第二方向的第三方向延伸的凸部和布置在凸部之间的多个凹部。

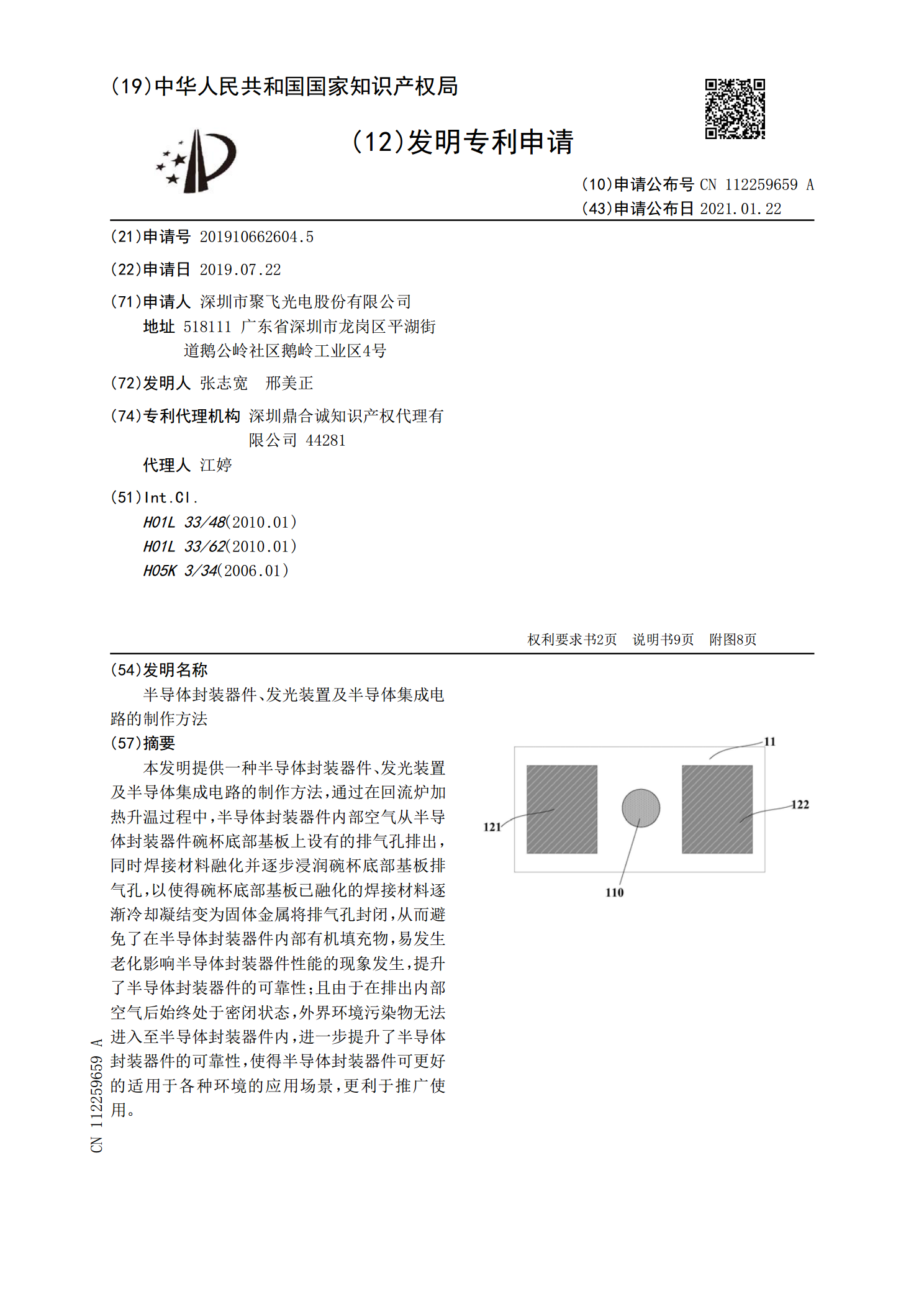

半导体封装器件、发光装置及半导体集成电路的制作方法.pdf

本发明提供一种半导体封装器件、发光装置及半导体集成电路的制作方法,通过在回流炉加热升温过程中,半导体封装器件内部空气从半导体封装器件碗杯底部基板上设有的排气孔排出,同时焊接材料融化并逐步浸润碗杯底部基板排气孔,以使得碗杯底部基板已融化的焊接材料逐渐冷却凝结变为固体金属将排气孔封闭,从而避免了在半导体封装器件内部有机填充物,易发生老化影响半导体封装器件性能的现象发生,提升了半导体封装器件的可靠性;且由于在排出内部空气后始终处于密闭状态,外界环境污染物无法进入至半导体封装器件内,进一步提升了半导体封装器件的可

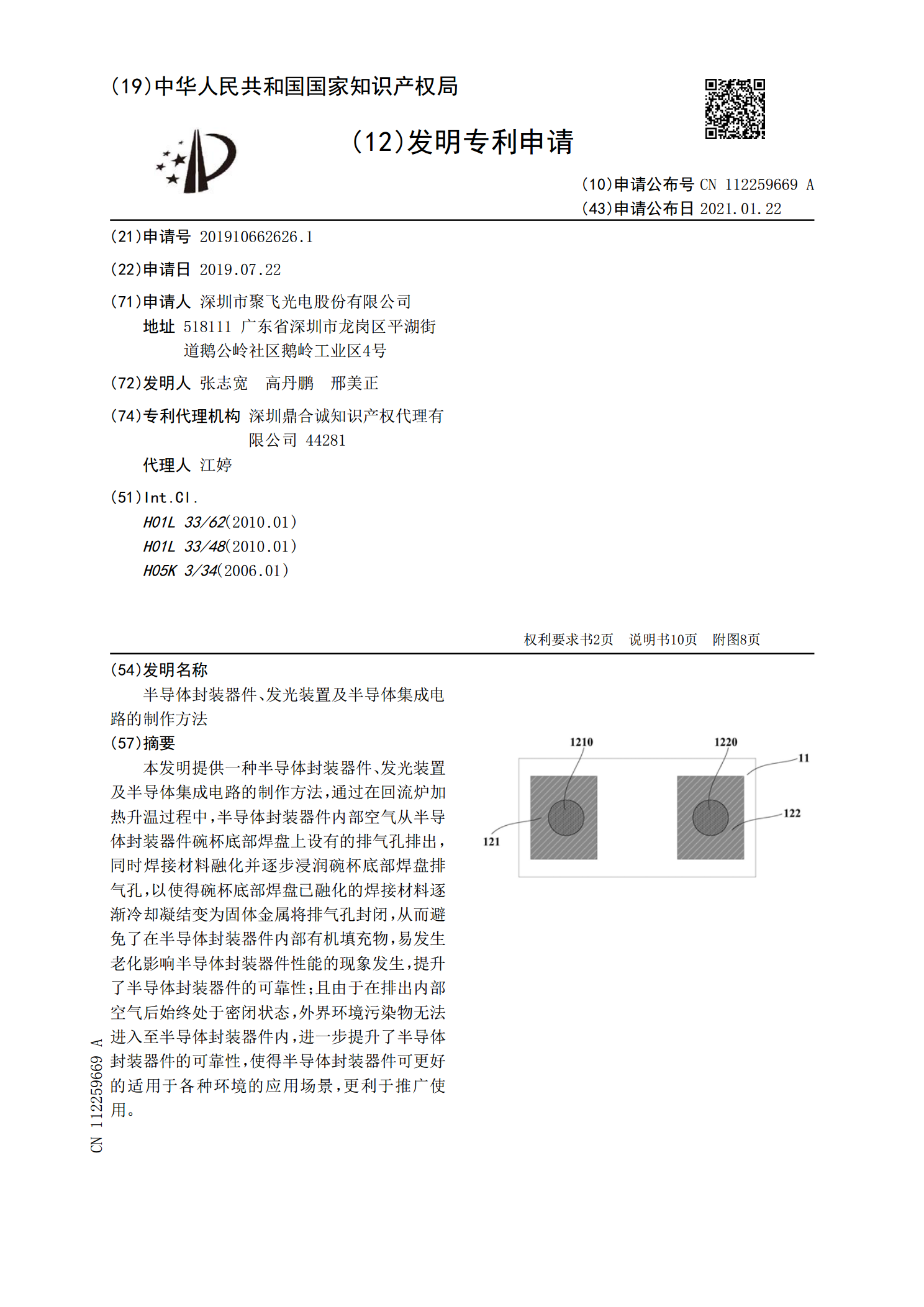

半导体封装器件、发光装置及半导体集成电路的制作方法.pdf

本发明提供一种半导体封装器件、发光装置及半导体集成电路的制作方法,通过在回流炉加热升温过程中,半导体封装器件内部空气从半导体封装器件碗杯底部焊盘上设有的排气孔排出,同时焊接材料融化并逐步浸润碗杯底部焊盘排气孔,以使得碗杯底部焊盘已融化的焊接材料逐渐冷却凝结变为固体金属将排气孔封闭,从而避免了在半导体封装器件内部有机填充物,易发生老化影响半导体封装器件性能的现象发生,提升了半导体封装器件的可靠性;且由于在排出内部空气后始终处于密闭状态,外界环境污染物无法进入至半导体封装器件内,进一步提升了半导体封装器件的可

半导体器件物理 Chapter4 集成电路制造工艺.ppt

第四章集成电路制造工艺芯片制造过程图形转换:将设计在掩膜版(类似于照相底片)上的图形转移到衬底上。掺杂:根据设计的需要将各种杂质掺杂在需要的位置上形成晶体管、接触等。制膜:制作各种材料的薄膜。硅片准备光刻(Lithography)光刻工艺流程光刻三要素:光刻胶、掩膜版和光刻机–光刻胶又叫光致抗蚀剂它是由光敏化合物、基体树脂和有机溶剂等混合而成的胶状液体。–光刻胶受到特定波长光线的作用后导致其化学结构发生变化使光刻胶在某种特定溶液中的溶解特性改变。正胶(曝光后可溶):分辨率高在超大规模集