碳化硅半导体器件.pdf

一吃****成益

亲,该文档总共26页,到这已经超出免费预览范围,如果喜欢就直接下载吧~

相关资料

碳化硅半导体器件.pdf

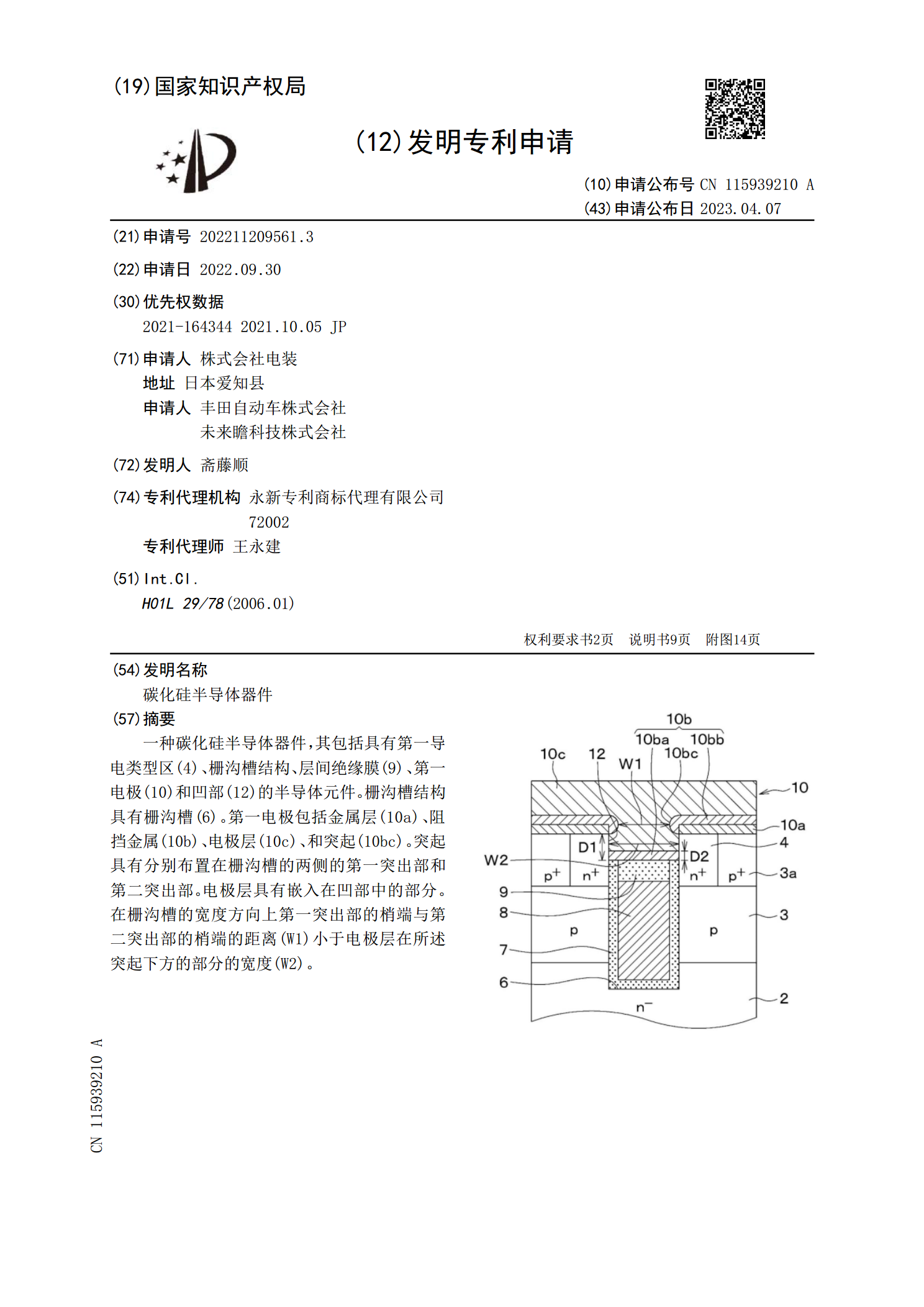

一种碳化硅半导体器件,其包括具有第一导电类型区(4)、栅沟槽结构、层间绝缘膜(9)、第一电极(10)和凹部(12)的半导体元件。栅沟槽结构具有栅沟槽(6)。第一电极包括金属层(10a)、阻挡金属(10b)、电极层(10c)、和突起(10bc)。突起具有分别布置在栅沟槽的两侧的第一突出部和第二突出部。电极层具有嵌入在凹部中的部分。在栅沟槽的宽度方向上第一突出部的梢端与第二突出部的梢端的距离(W1)小于电极层在所述突起下方的部分的宽度(W2)。

碳化硅半导体器件及制备方法.pdf

(19)中华人民共和国国家知识产权局(12)发明专利说明书(10)申请公布号CN113972261A(43)申请公布日2022.01.25(21)申请号CN202111182922.5(22)申请日2021.10.11(71)申请人松山湖材料实验室地址523000广东省东莞市松山湖大学创新城A1栋(72)发明人陈昭铭殷鸿杰罗惠馨夏经华张安平(74)专利代理机构44224广州华进联合专利商标代理有限公司代理人潘宏洲(51)Int.CIH01L29/06(20060101)H01L29/10(20060101

碳化硅功率半导体器件结构.pdf

本发明提供一种碳化硅功率半导体器件结构,包括:第一导电类型衬底、第一导电类型漂移区、第二导电类型体区、第一导电类型源区、第二导电类型基区、结型场效应晶体管区、第二导电类型屏蔽区、栅极结构、绝缘层及源极金属层。本发明通过将源极接触窗口设置为至少有一条边线不超出第二导电类型体区与该边线对应的边缘,从而缩小源极接触窗口的面积,使源极金属层只在局部与第一导电类型源区接触。本发明可以有效将碳化硅功率半导体器件结构的总面积进一步缩小,增大沟道长度和结型场效应晶体管区面积与器件结构的总面积的比值,即增大了沟道密度和结型

碳化硅器件及其制备方法和半导体器件.pdf

(19)中华人民共和国国家知识产权局(12)发明专利说明书(10)申请公布号CN113130647A(43)申请公布日2021.07.16(21)申请号CN201911398699.0(22)申请日2019.12.30(71)申请人比亚迪半导体股份有限公司地址518119广东省深圳市大鹏新区葵涌街道延安路1号(72)发明人朱辉肖秀光(74)专利代理机构44325深圳众鼎专利商标代理事务所(普通合伙)代理人张美君(51)Int.CIH01L29/78(20060101)H01L29/06(20060101)

用于制造碳化硅半导体器件的方法.pdf

包含Si的气体、包含C的气体和包含Cl的气体被引入反应燃烧炉(步骤S5)。接着,在步骤S5引入的包含原始材料气体、添加剂气体、掺杂气体和运载气体的气体气氛中,通过CVD方法在4H-SiC衬底的表面上生长SiC外延膜(步骤S6:第一步骤)。在此场合中,包含Cl的气体相对于含Si的气体的引入量被逐渐减少(第二步骤)。在生长开始时气体气氛的合成物中,包含Cl的气体中Cl原子的数目大至包含Si的气体中Si原子的数目的三倍。在第二步骤中,气体气氛中包含氯的气体中氯原子的数目相对于包含硅的气体中硅原子的数目以0.5%