一种结势垒肖特基二极管及其制备方法.pdf

一吃****书竹

在线预览结束,喜欢就下载吧,查找使用更方便

相关资料

一种结势垒肖特基二极管及其制备方法.pdf

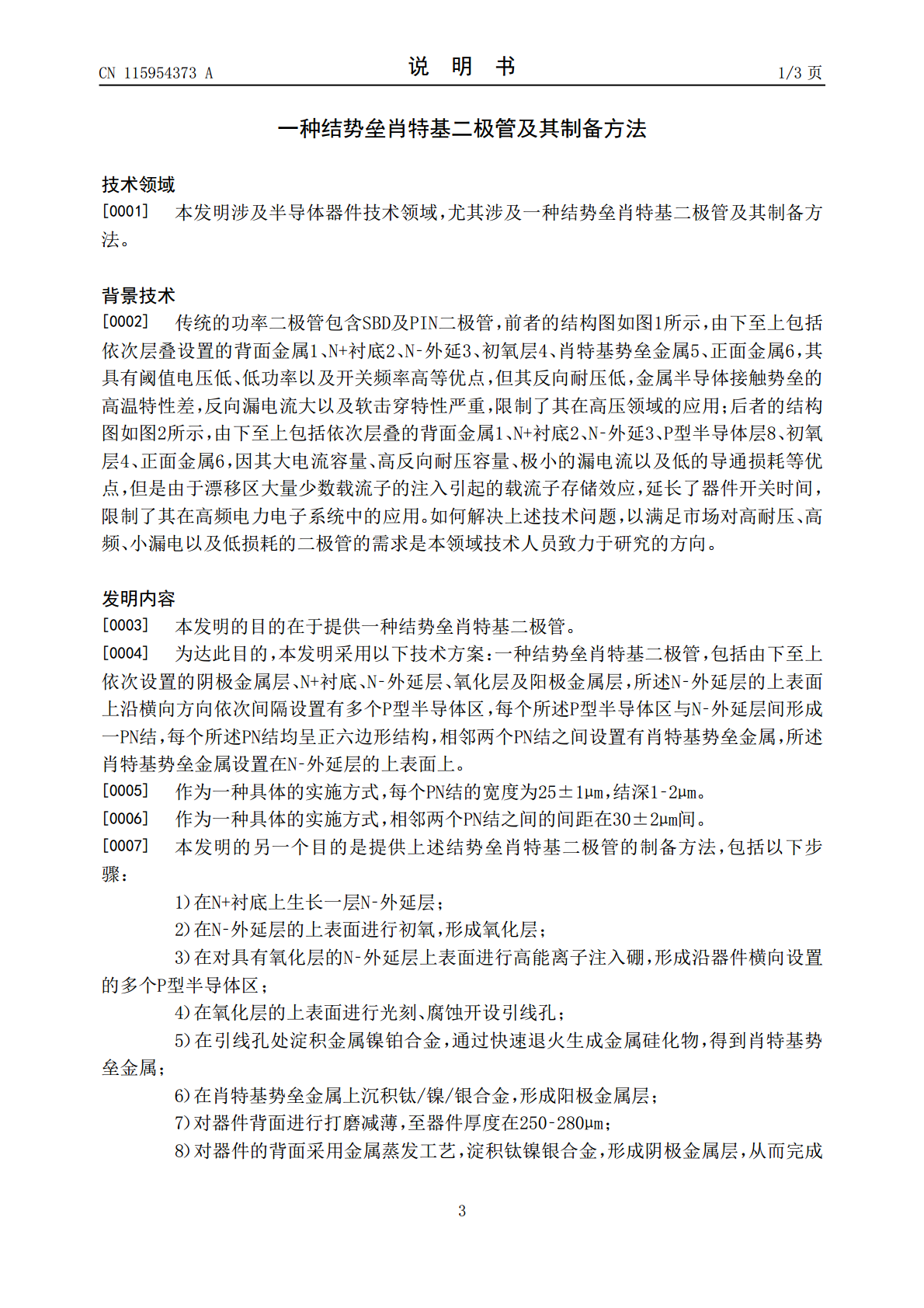

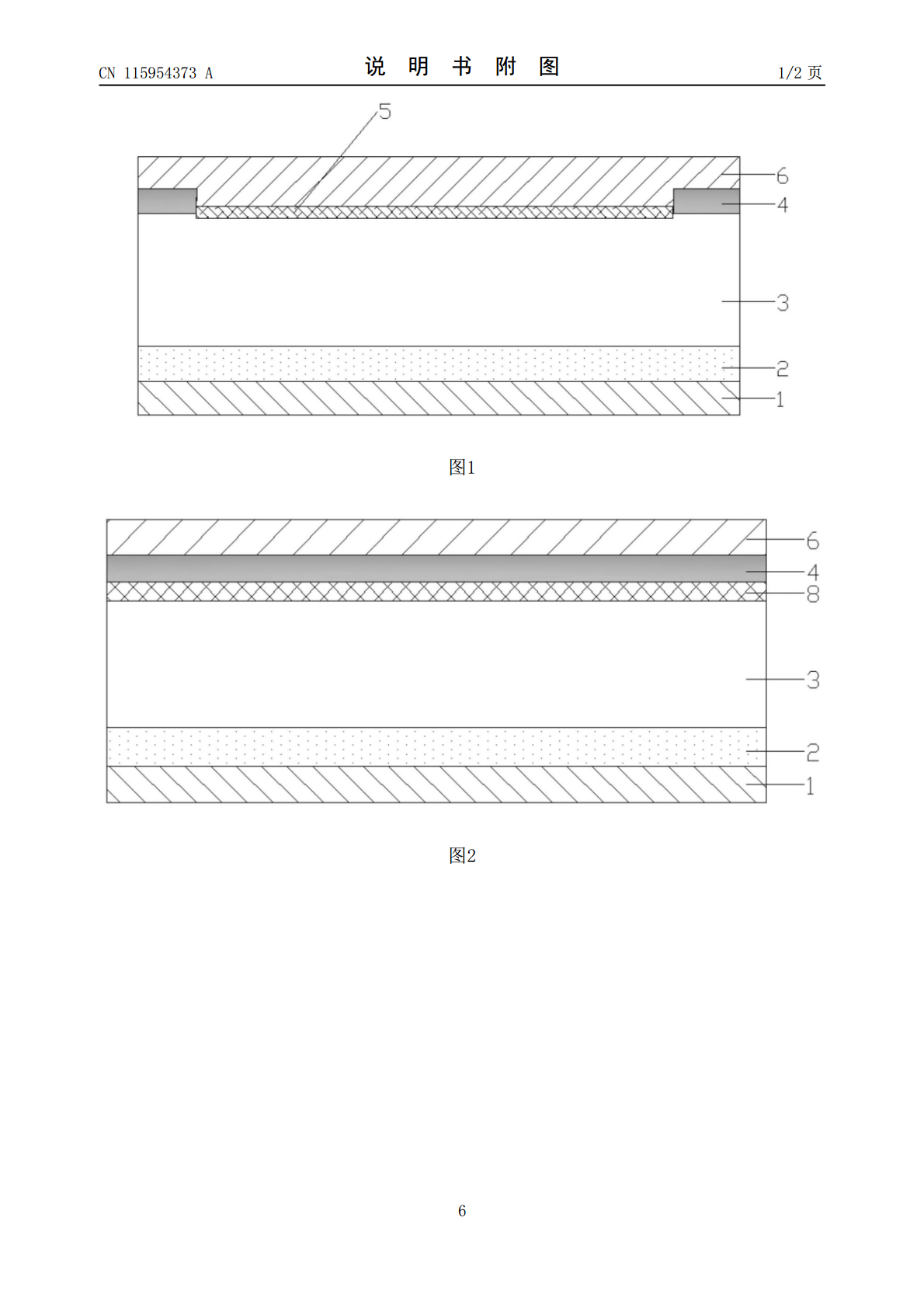

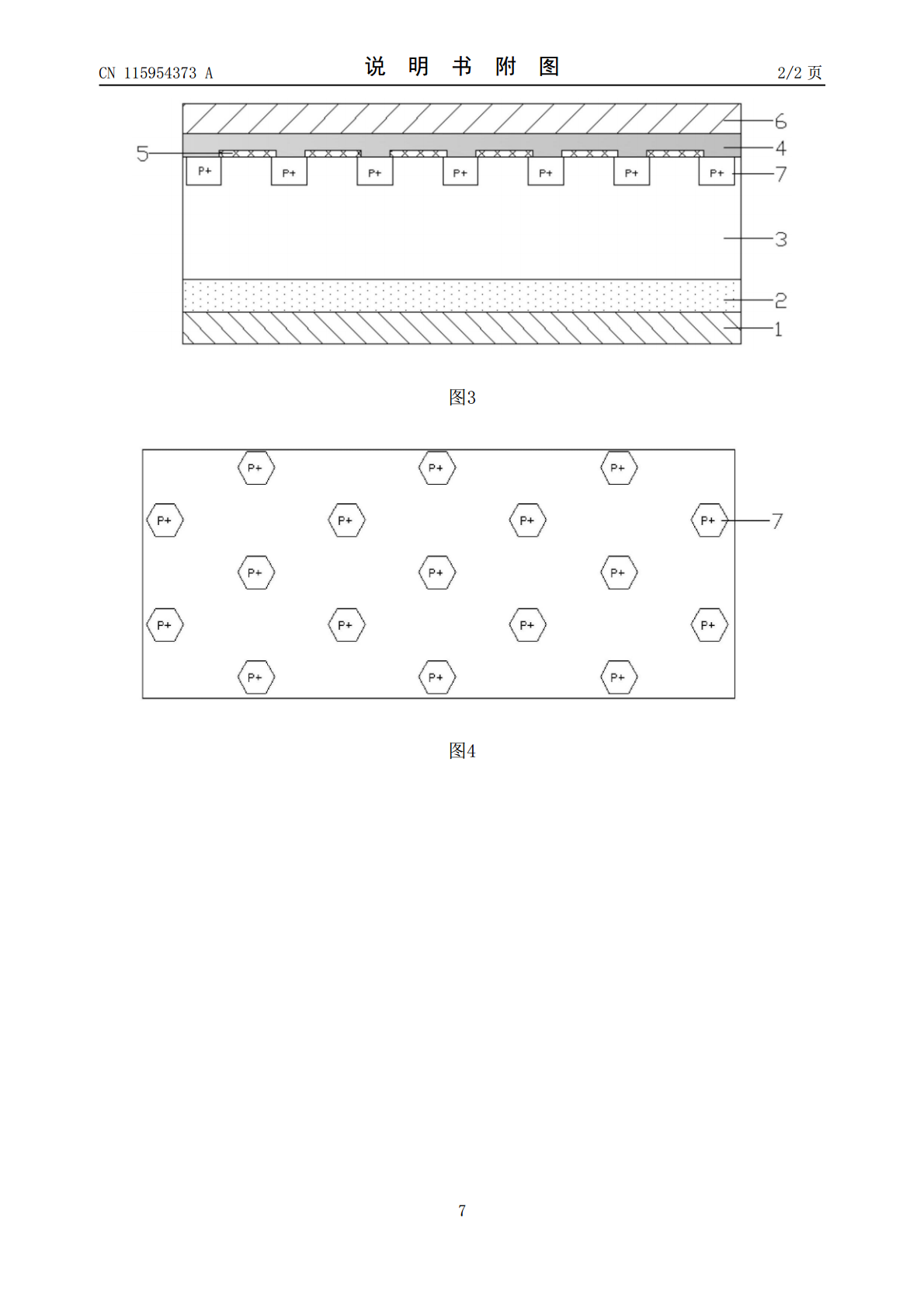

本发明公开了一种结势垒肖特基二极管及其制备方法,该肖特基二极管包括由下至上依次设置的阴极金属层、N+衬底、N‑外延层、氧化层及阳极金属层,所述N‑外延层的上表面上沿横向方向依次间隔设置有多个P型半导体区,每个所述P型半导体区与N‑外延层间形成一PN结,每个所述PN结均呈正六边形结构,相邻两个PN结之间设置有肖特基势垒金属,所述肖特基势垒金属设置在N‑外延层的上表面上。本发明的肖特基二极管具有高耐压、高频、漏电小、损耗低等特点。

肖特基势垒二极管及其制造方法.pdf

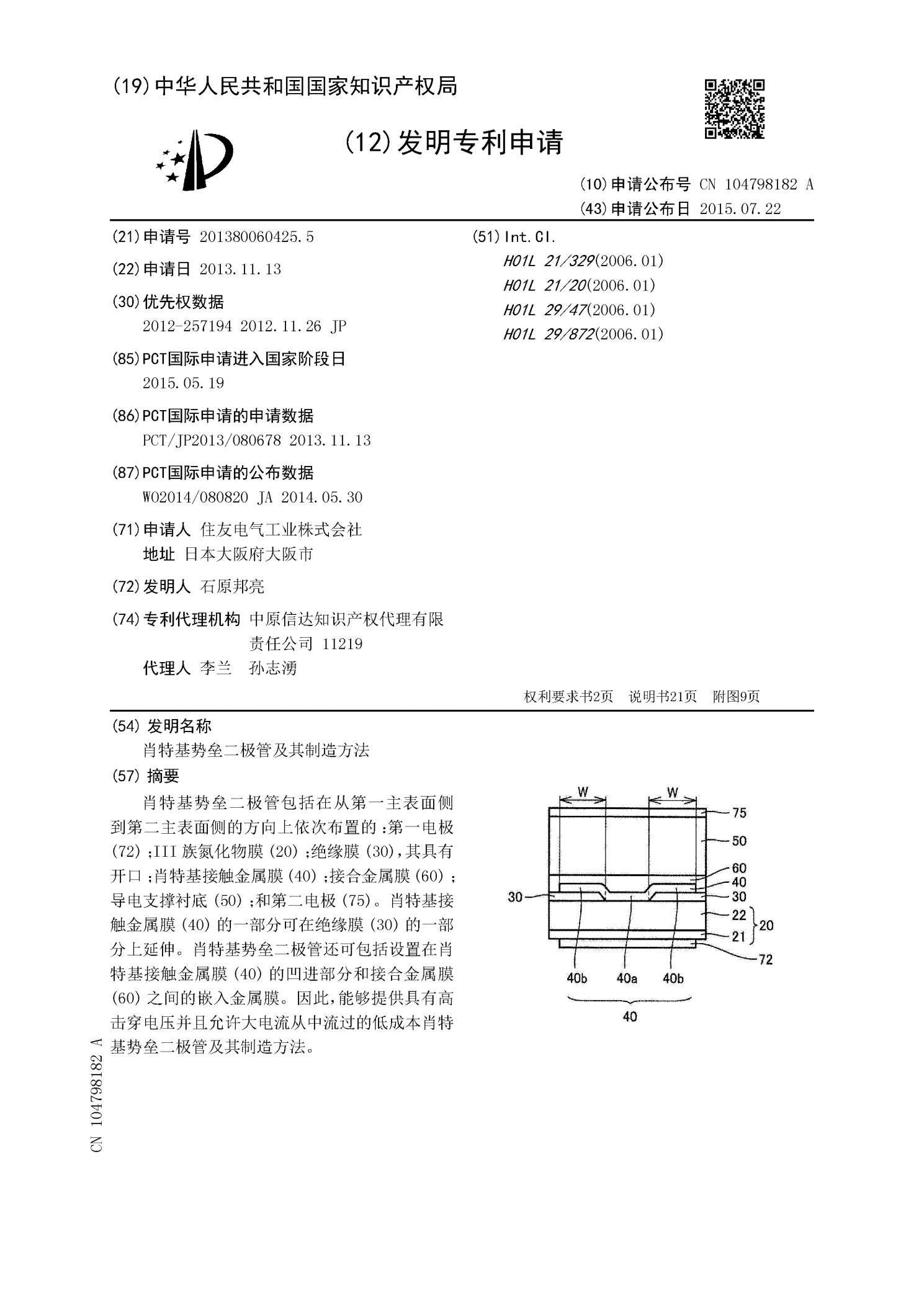

肖特基势垒二极管包括在从第一主表面侧到第二主表面侧的方向上依次布置的:第一电极(72);III族氮化物膜(20);绝缘膜(30),其具有开口;肖特基接触金属膜(40);接合金属膜(60);导电支撑衬底(50);和第二电极(75)。肖特基接触金属膜(40)的一部分可在绝缘膜(30)的一部分上延伸。肖特基势垒二极管还可包括设置在肖特基接触金属膜(40)的凹进部分和接合金属膜(60)之间的嵌入金属膜。因此,能够提供具有高击穿电压并且允许大电流从中流过的低成本肖特基势垒二极管及其制造方法。

肖特基势垒二极管及其制造方法.pdf

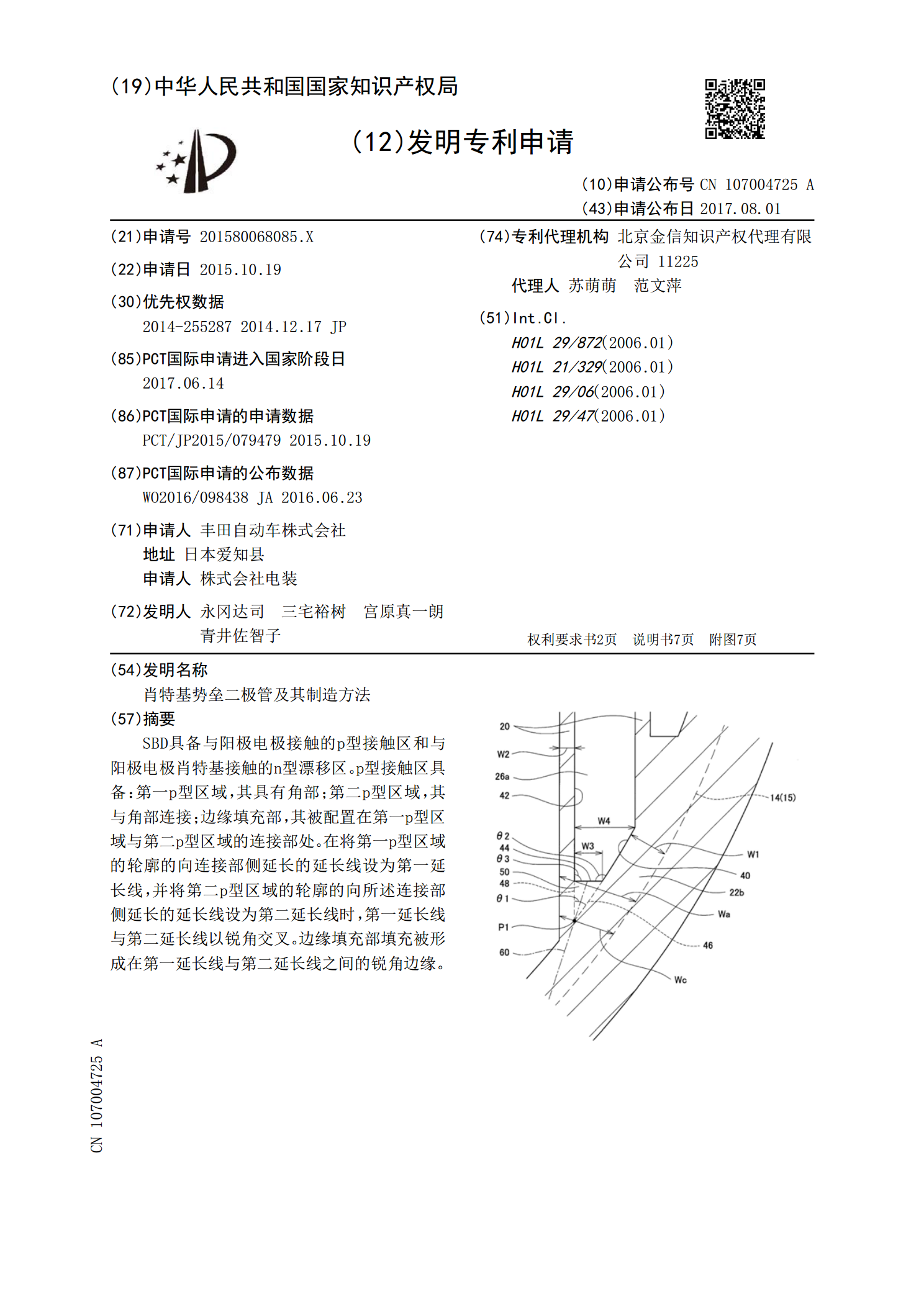

SBD具备与阳极电极接触的p型接触区和与阳极电极肖特基接触的n型漂移区。p型接触区具备:第一p型区域,其具有角部;第二p型区域,其与角部连接;边缘填充部,其被配置在第一p型区域与第二p型区域的连接部处。在将第一p型区域的轮廓的向连接部侧延长的延长线设为第一延长线,并将第二p型区域的轮廓的向所述连接部侧延长的延长线设为第二延长线时,第一延长线与第二延长线以锐角交叉。边缘填充部填充被形成在第一延长线与第二延长线之间的锐角边缘。

一种准垂直结构GaN肖特基势垒二极管及其制备方法.pdf

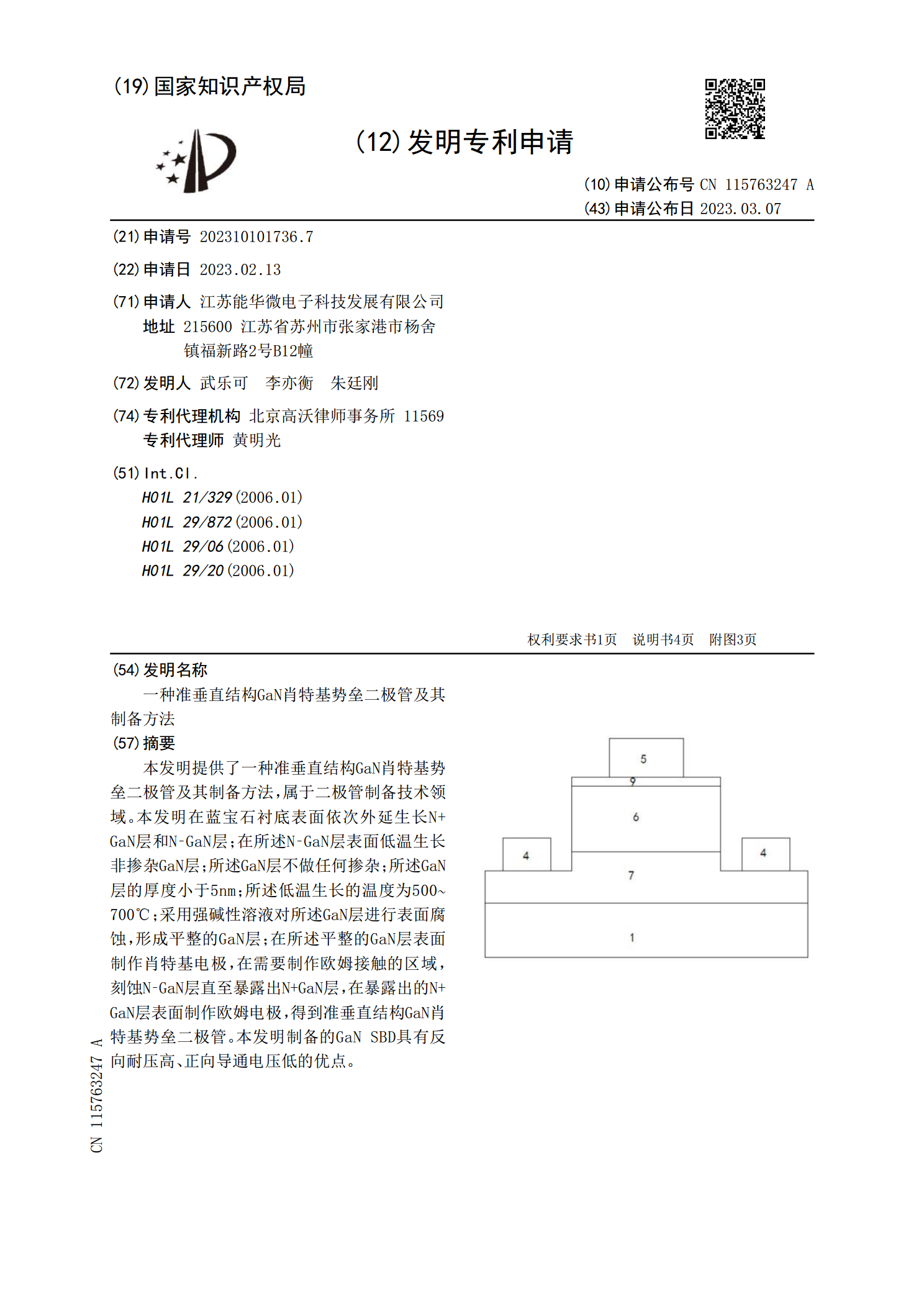

本发明提供了一种准垂直结构GaN肖特基势垒二极管及其制备方法,属于二极管制备技术领域。本发明在蓝宝石衬底表面依次外延生长N+GaN层和N‑GaN层;在所述N‑GaN层表面低温生长非掺杂GaN层;所述GaN层不做任何掺杂;所述GaN层的厚度小于5nm;所述低温生长的温度为500~700℃;采用强碱性溶液对所述GaN层进行表面腐蚀,形成平整的GaN层;在所述平整的GaN层表面制作肖特基电极,在需要制作欧姆接触的区域,刻蚀N‑GaN层直至暴露出N+GaN层,在暴露出的N+GaN层表面制作欧姆电极,得到准垂直结构

一种氮化镓肖特基势垒二极管及其制造方法.pdf

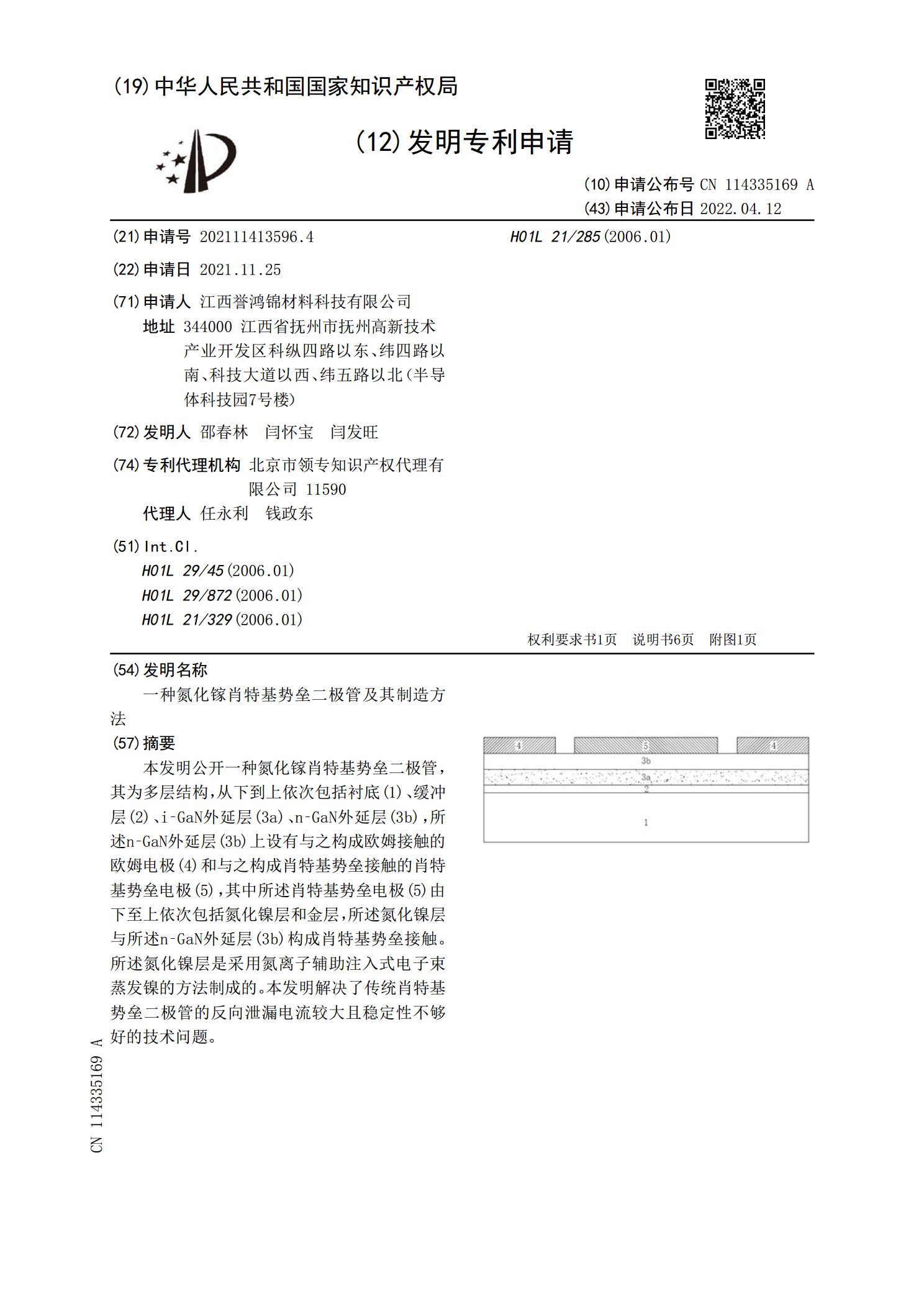

本发明公开一种氮化镓肖特基势垒二极管,其为多层结构,从下到上依次包括衬底(1)、缓冲层(2)、i?GaN外延层(3a)、n?GaN外延层(3b),所述n?GaN外延层(3b)上设有与之构成欧姆接触的欧姆电极(4)和与之构成肖特基势垒接触的肖特基势垒电极(5),其中所述肖特基势垒电极(5)由下至上依次包括氮化镍层和金层,所述氮化镍层与所述n?GaN外延层(3b)构成肖特基势垒接触。所述氮化镍层是采用氮离子辅助注入式电子束蒸发镍的方法制成的。本发明解决了传统肖特基势垒二极管的反向泄漏电流较大且稳定性不够好的技