高电压静电器件.pdf

是你****元呀

亲,该文档总共14页,到这已经超出免费预览范围,如果喜欢就直接下载吧~

相关资料

高电压静电器件.pdf

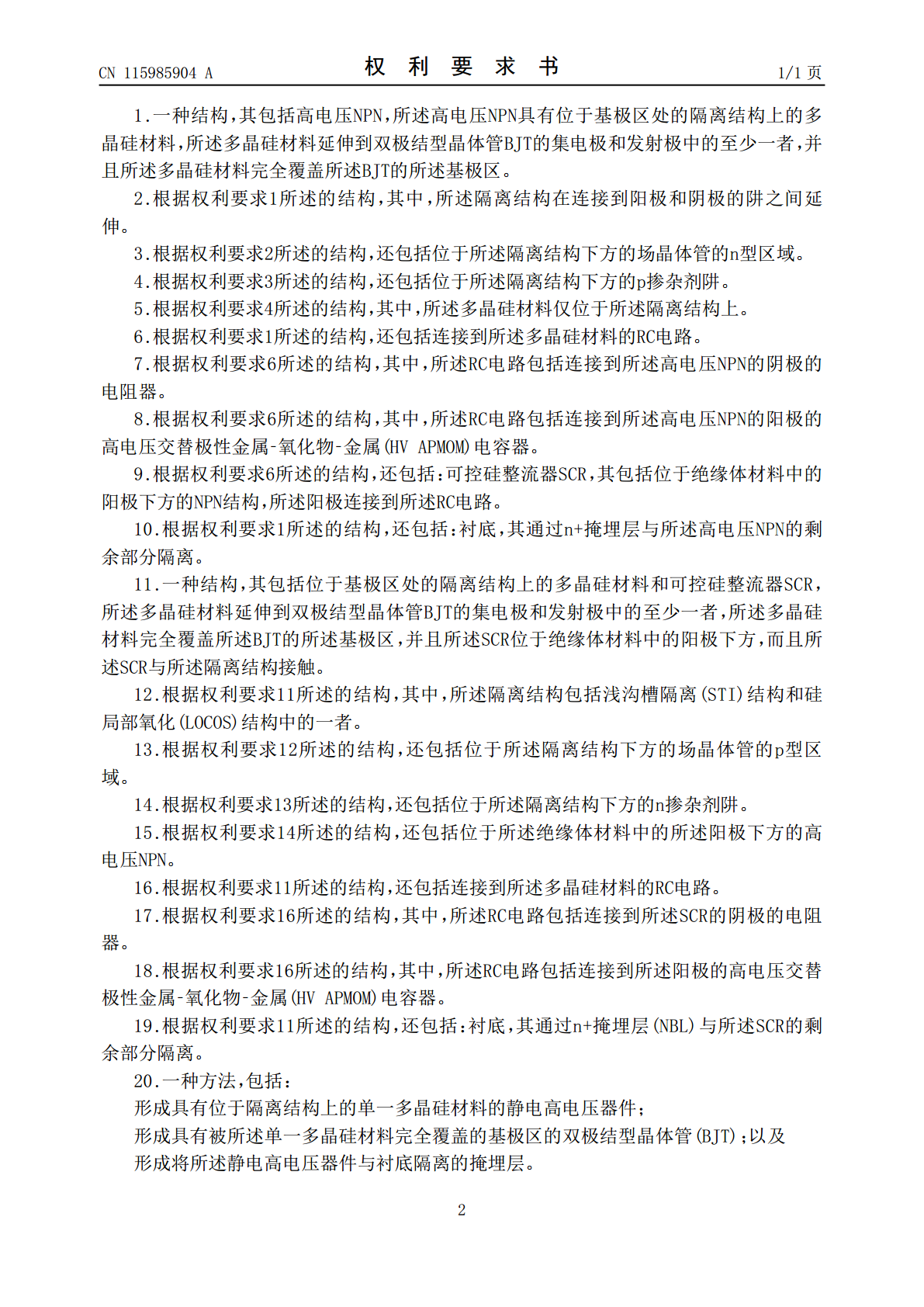

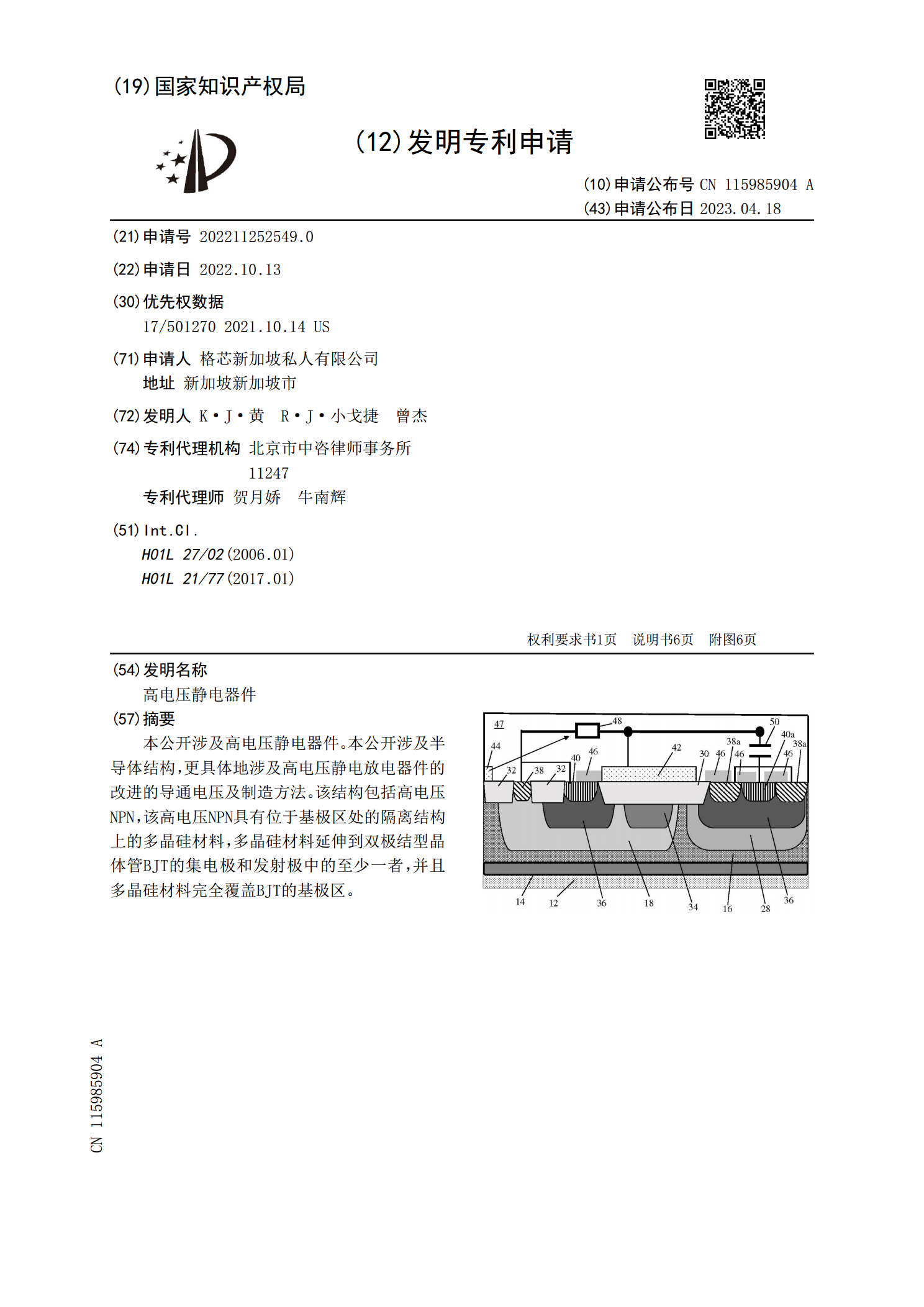

本公开涉及高电压静电器件。本公开涉及半导体结构,更具体地涉及高电压静电放电器件的改进的导通电压及制造方法。该结构包括高电压NPN,该高电压NPN具有位于基极区处的隔离结构上的多晶硅材料,多晶硅材料延伸到双极结型晶体管BJT的集电极和发射极中的至少一者,并且多晶硅材料完全覆盖BJT的基极区。

高电压静电放电器件.pdf

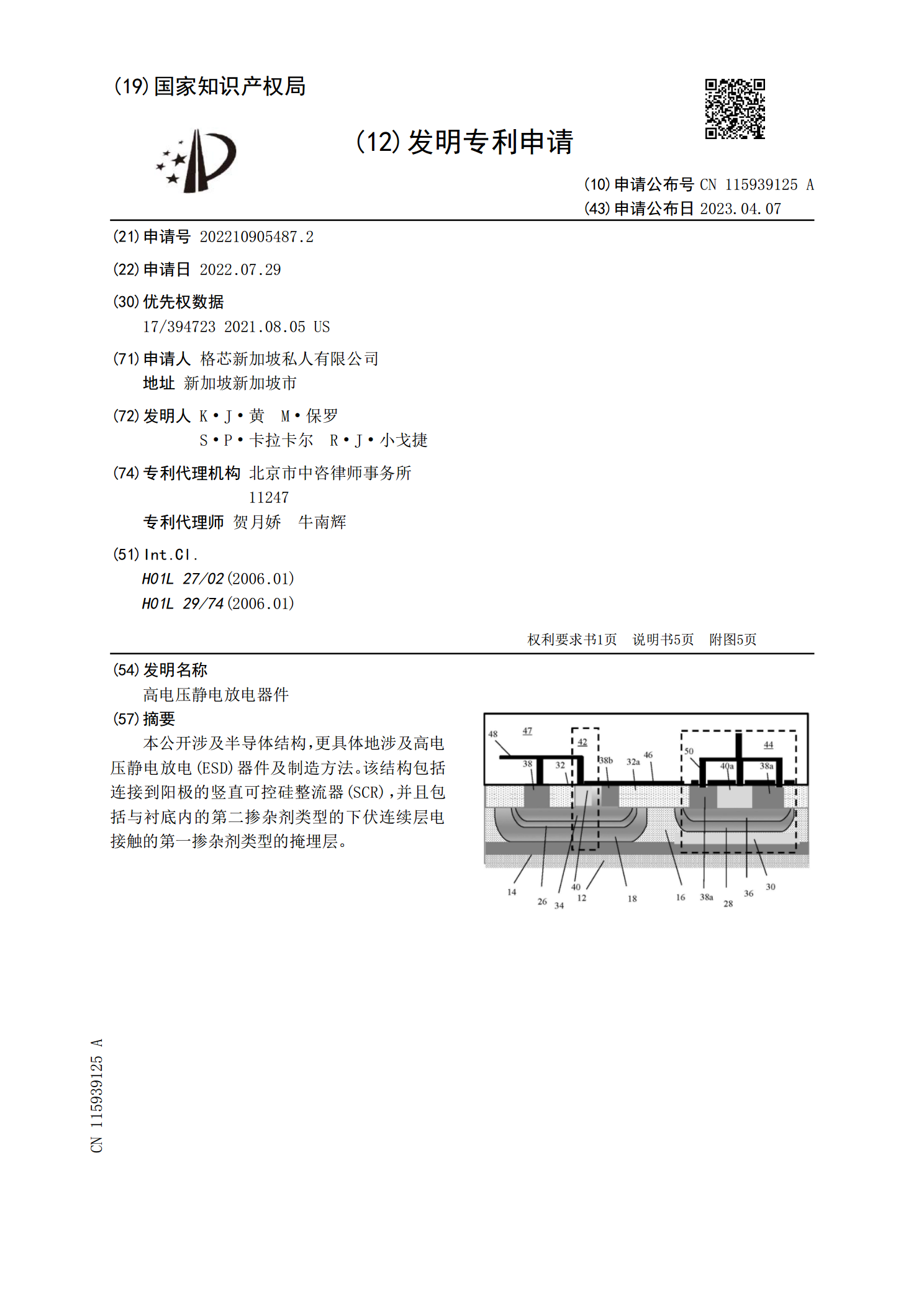

本公开涉及半导体结构,更具体地涉及高电压静电放电(ESD)器件及制造方法。该结构包括连接到阳极的竖直可控硅整流器(SCR),并且包括与衬底内的第二掺杂剂类型的下伏连续层电接触的第一掺杂剂类型的掩埋层。

低触发电压高维持电压单向可控硅静电防护器件及方法.pdf

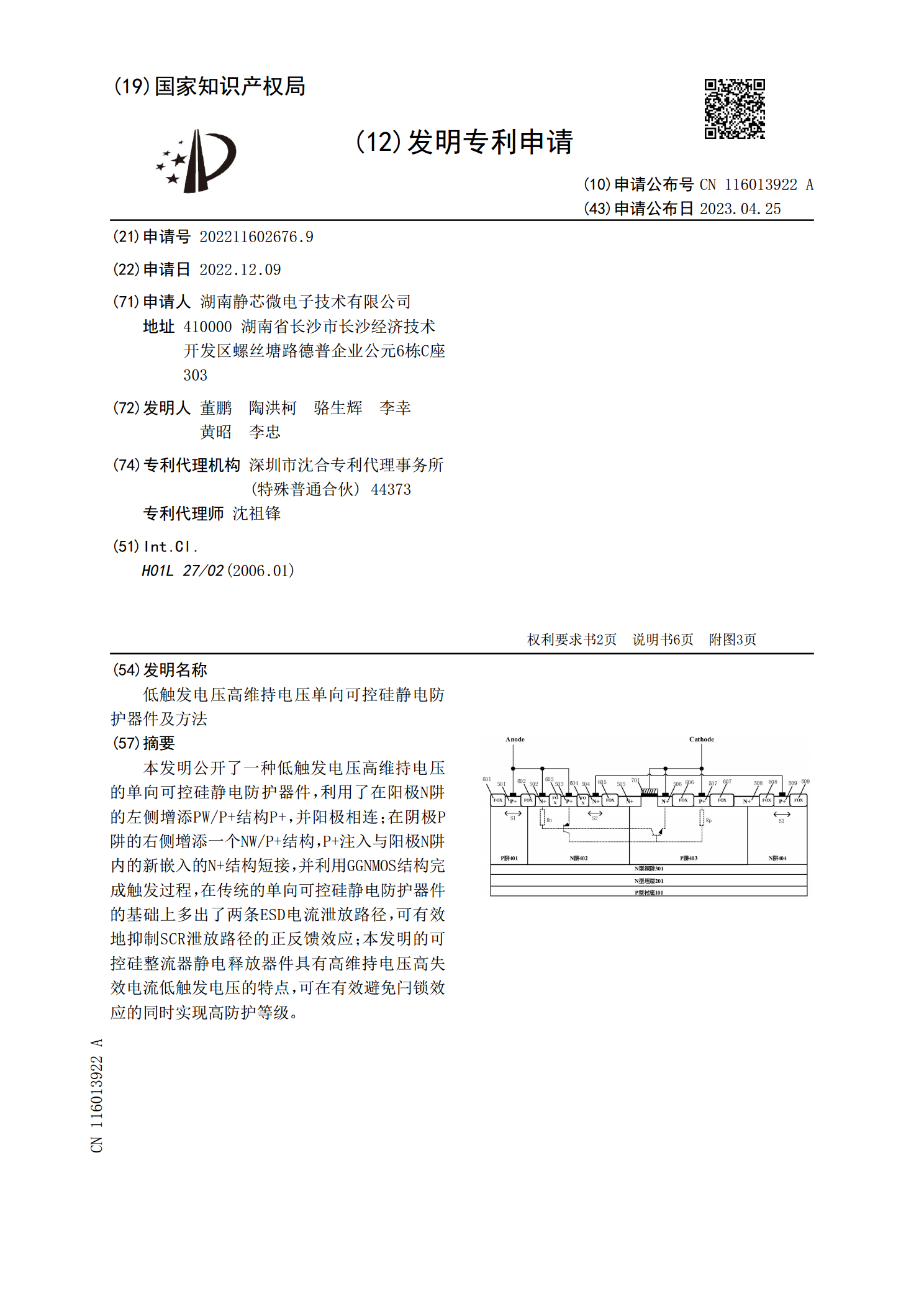

本发明公开了一种低触发电压高维持电压的单向可控硅静电防护器件,利用了在阳极N阱的左侧增添PW/P+结构P+,并阳极相连;在阴极P阱的右侧增添一个NW/P+结构,P+注入与阳极N阱内的新嵌入的N+结构短接,并利用GGNMOS结构完成触发过程,在传统的单向可控硅静电防护器件的基础上多出了两条ESD电流泄放路径,可有效地抑制SCR泄放路径的正反馈效应;本发明的可控硅整流器静电释放器件具有高维持电压高失效电流低触发电压的特点,可在有效避免闩锁效应的同时实现高防护等级。

基于CMOS工艺的高维持电压SCR静电防护器件设计的任务书.docx

基于CMOS工艺的高维持电压SCR静电防护器件设计的任务书任务书一、任务背景随着集成电路的不断发展和应用,集成电路所承担的功能越来越多,同时也面临着更多的电磁干扰和静电损伤的威胁。其中,静电放电(ElectrostaticDischarge,简称ESD)在现代集成电路技术中是一个难以忽视的问题,它能够直接损伤或间接导致芯片损坏,从而影响产品的可靠性和性能。因此,在集成电路设计和制造过程中,静电防护问题也逐渐变得越来越重要。为了解决这个问题,静电防护器件应运而生。其中,高维持电压SCR静电防护器件是一种常见

高电压Ⅲ族氮化物半导体器件.pdf

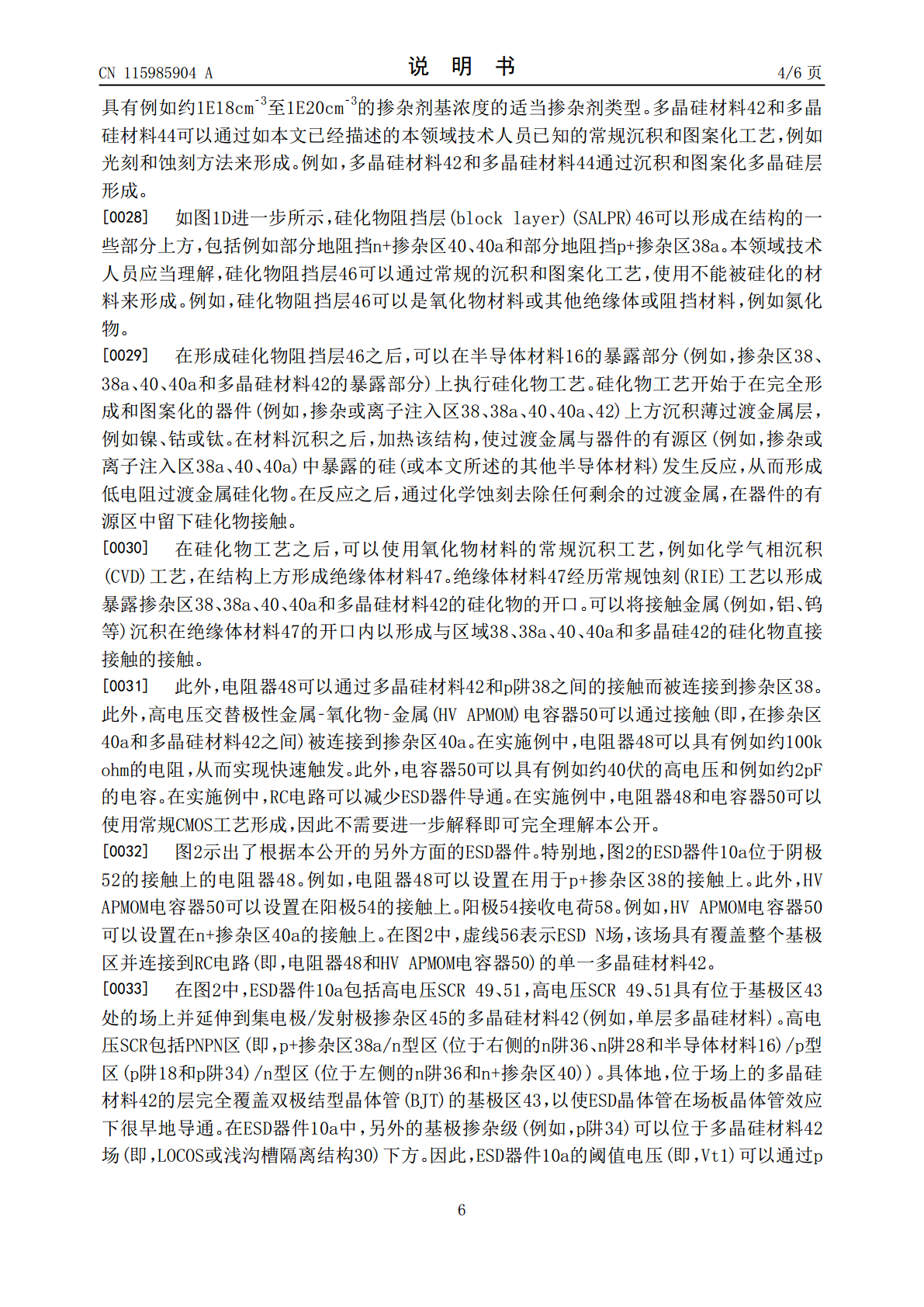

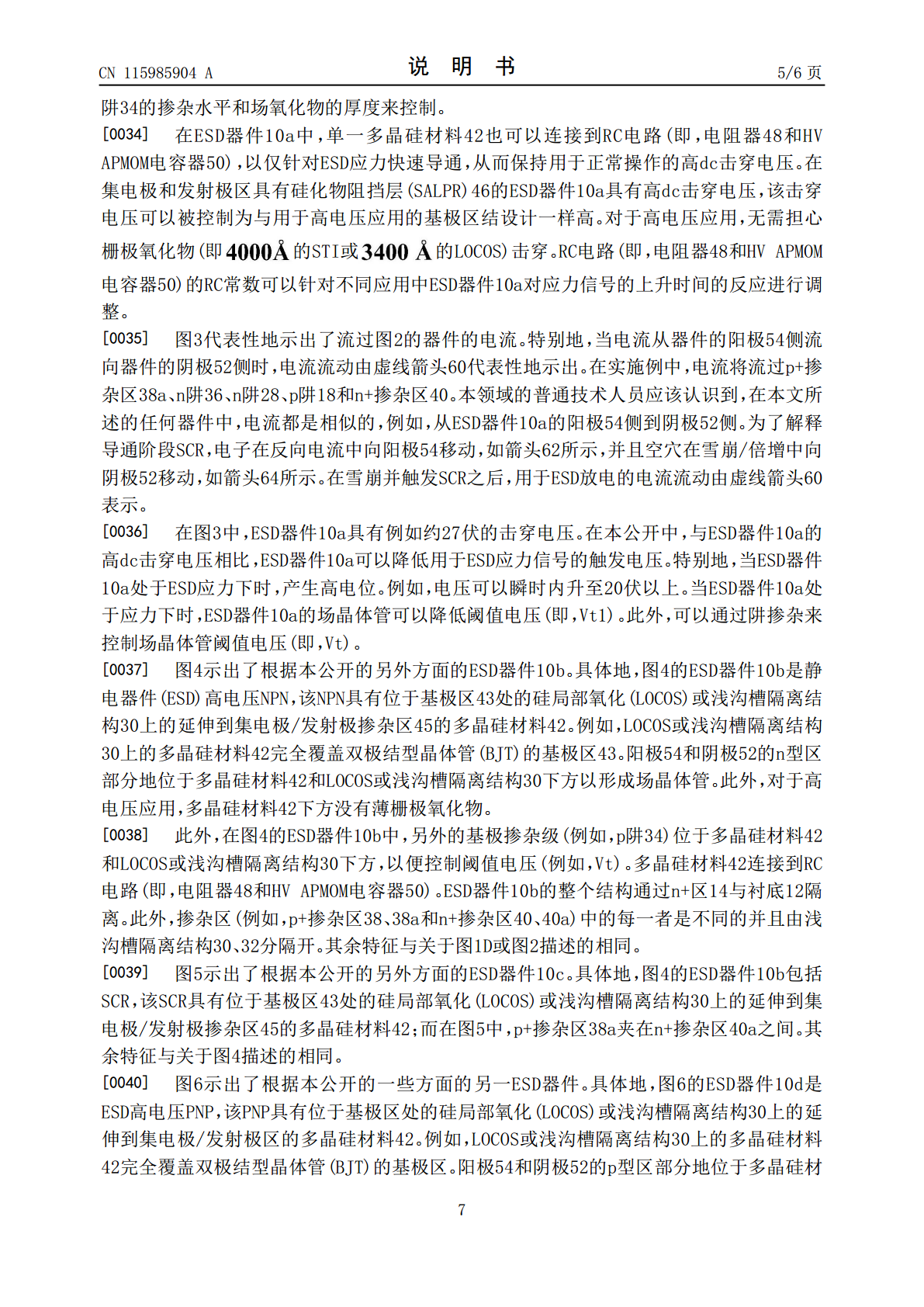

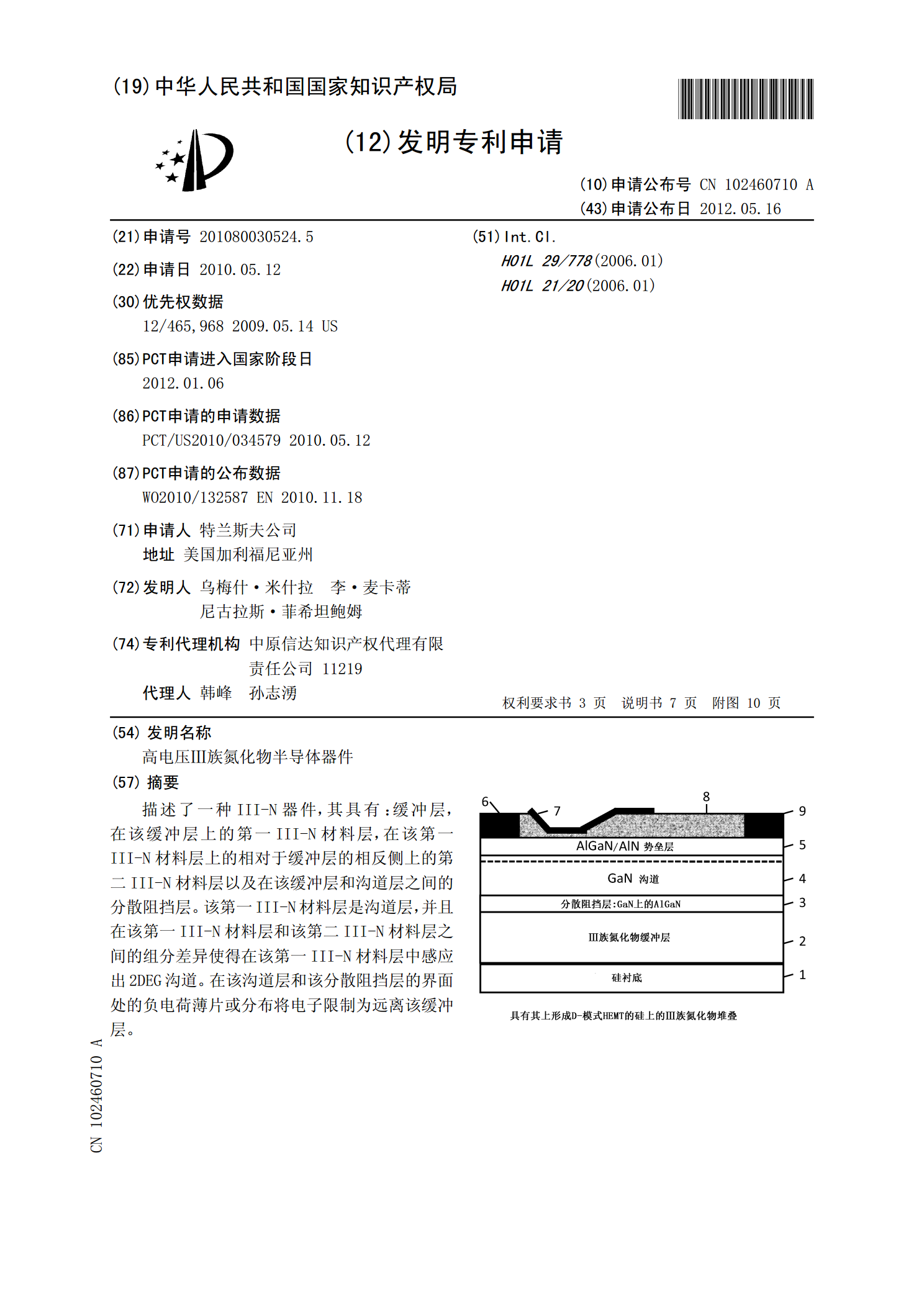

描述了一种III-N器件,其具有:缓冲层,在该缓冲层上的第一III-N材料层,在该第一III-N材料层上的相对于缓冲层的相反侧上的第二III-N材料层以及在该缓冲层和沟道层之间的分散阻挡层。该第一III-N材料层是沟道层,并且在该第一III-N材料层和该第二III-N材料层之间的组分差异使得在该第一III-N材料层中感应出2DEG沟道。在该沟道层和该分散阻挡层的界面处的负电荷薄片或分布将电子限制为远离该缓冲层。