一种闪存阵列及闪存芯片.pdf

是翠****ng

亲,该文档总共20页,到这已经超出免费预览范围,如果喜欢就直接下载吧~

相关资料

一种闪存阵列及闪存芯片.pdf

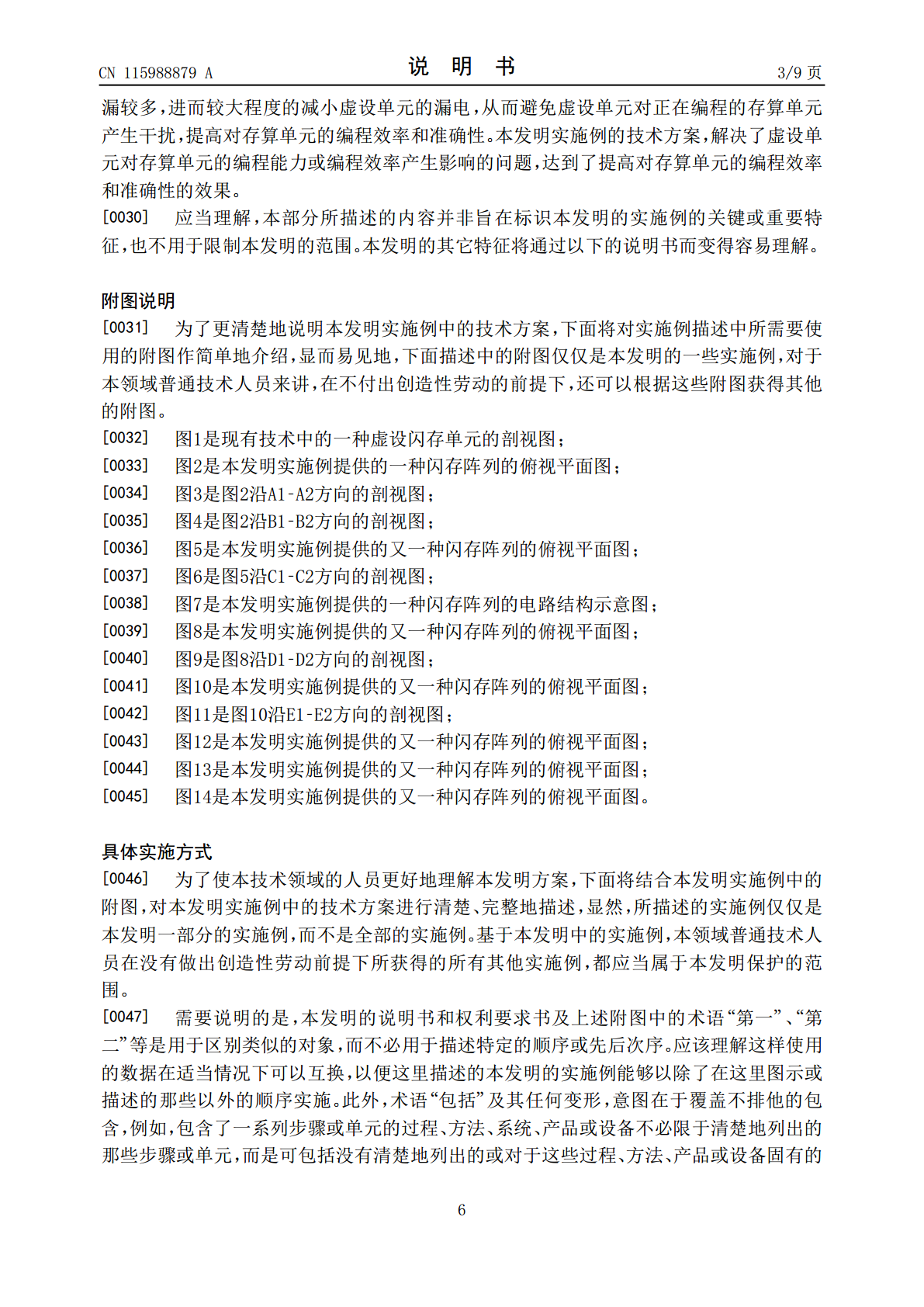

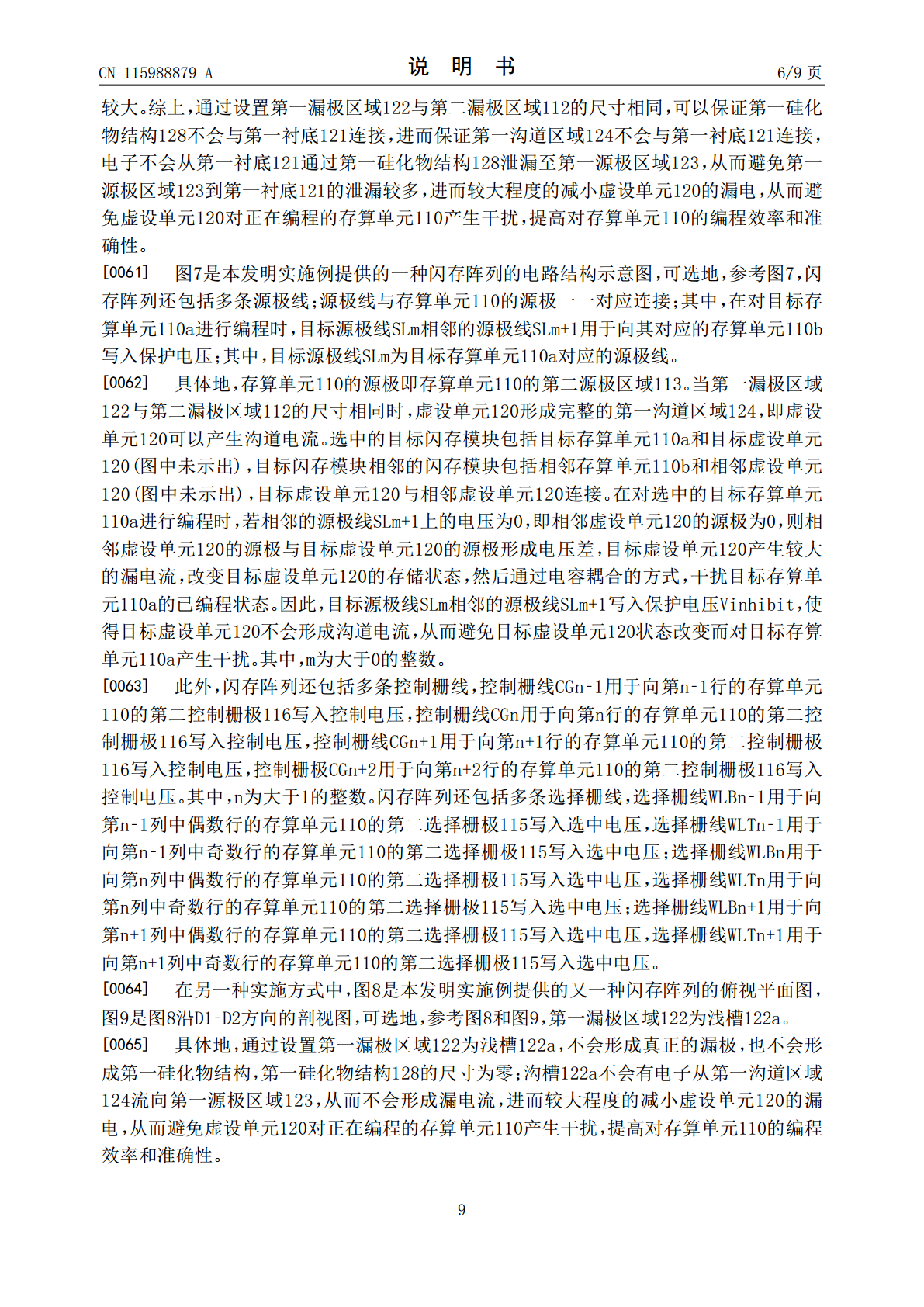

本发明公开了一种闪存阵列及闪存芯片。闪存阵列包括阵列排布的多个闪存模块;闪存模块包括一个存算单元和至少一个虚设单元;存算单元与虚设单元相间排布;虚设单元包括第一衬底、位于第一衬底内的第一漏极区域、第一源极区域和第一沟道区域、及位于第一衬底上的第一选择栅极、第一控制栅极和第一浮置栅极;其中,第一控制栅极与第一浮置栅极位于第一选择栅极的第一侧;第一漏极区域在第一衬底的正投影位于第一选择栅极在第一衬底的正投影的第二侧;虚设单元还包括第一硅化物结构,第一硅化物结构位于第一漏极区域远离第一衬底的表面,且第一硅化物结

闪存阵列的写入方法.pdf

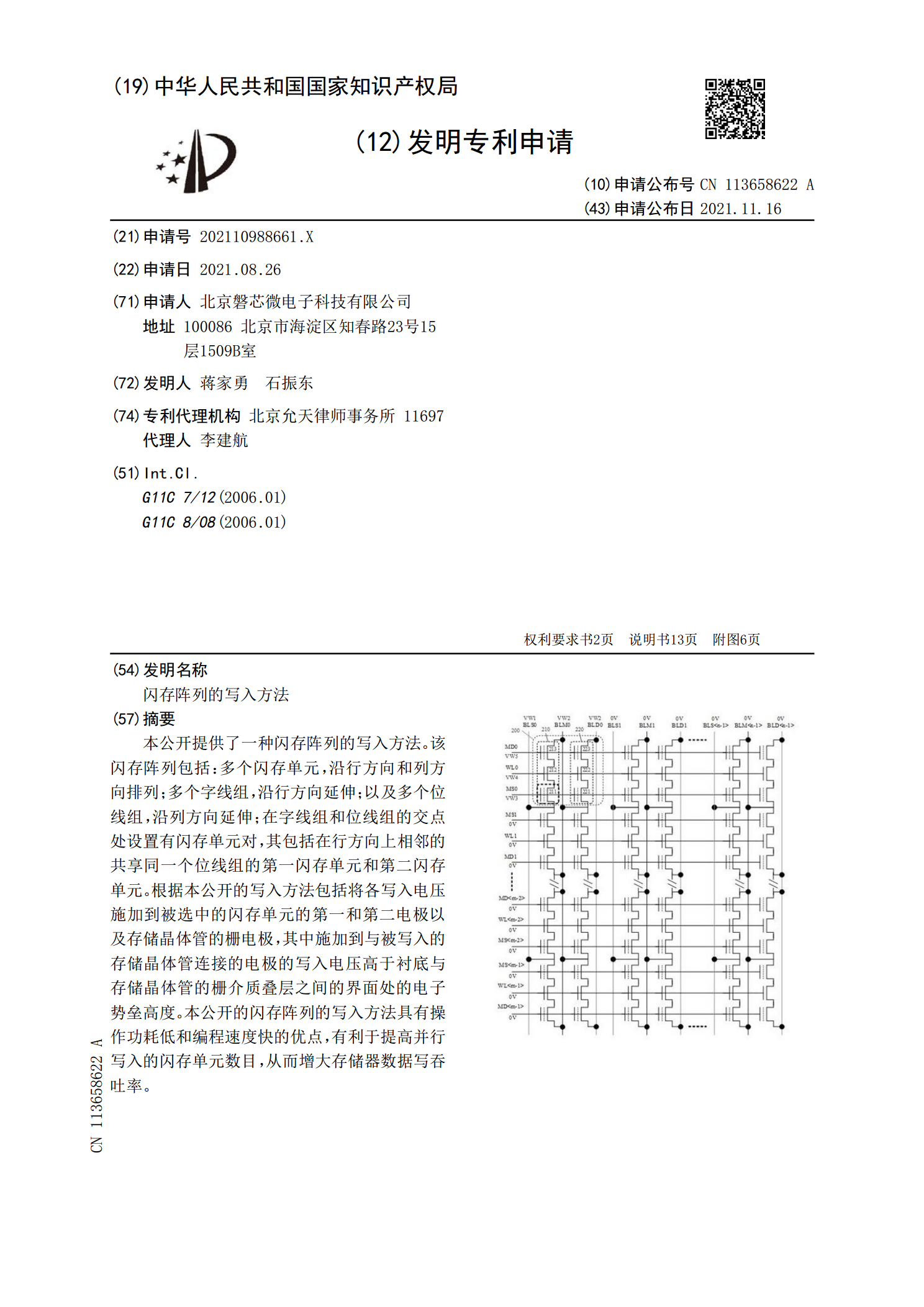

本公开提供了一种闪存阵列的写入方法。该闪存阵列包括:多个闪存单元,沿行方向和列方向排列;多个字线组,沿行方向延伸;以及多个位线组,沿列方向延伸;在字线组和位线组的交点处设置有闪存单元对,其包括在行方向上相邻的共享同一个位线组的第一闪存单元和第二闪存单元。根据本公开的写入方法包括将各写入电压施加到被选中的闪存单元的第一和第二电极以及存储晶体管的栅电极,其中施加到与被写入的存储晶体管连接的电极的写入电压高于衬底与存储晶体管的栅介质叠层之间的界面处的电子势垒高度。本公开的闪存阵列的写入方法具有操作功耗低和编程速

全闪存阵列在医院的应用.docx

全闪存阵列在医院的应用本文档来自社区交流活动,更多相关内容请点击长按二维码关注公众号

闪存阵列竞争分析ppt课件.pptx

©Copyright2014EMCCorporation.Allrightsreserved.XtremIO在全闪存阵列市场占有领先地位全闪存阵列的发展历程:XtremIO领先于时代HP3PARStoreServ7450概览XtremIO与3PAR7450关键参数对比HP3PAR7450声称90万IOPS,0.7ms延迟,该指标欺骗用户,生产环境下能否兑现值得怀疑;为获得更好性能,7450建议采用RAID10配置,并且不能开启去重,低成本与高性能不能兼得;EMC内部测试,XtremIO半块砖的配置可以打败

闪存芯片是什么_类型有哪些_.docx

闪存芯片是什么_类型有哪些_1.闪存芯片是什么闪存芯片是一种对闪存存储单元进行分层管理的芯片,内部结构由高到低可表示为:芯片封装(Package)→层(Die)→块(Block)→页(Page)→存储胞元(Cell)。存芯片的操作单位为页(page),每个page的容量一般为4KB或者8KB,在page的数据区之外还有一块带外区域(OutofBand,OOB),一般在128字节以上,一般用来存储页面的元数据信息和校验信息。2.闪存芯片的类型闪存也有不同类型,其中主要分为NOR型和NAND型两大类。NOR型