时序逻辑电路.ppt

sy****28

亲,该文档总共176页,到这已经超出免费预览范围,如果喜欢就直接下载吧~

相关资料

时序逻辑电路.ppt

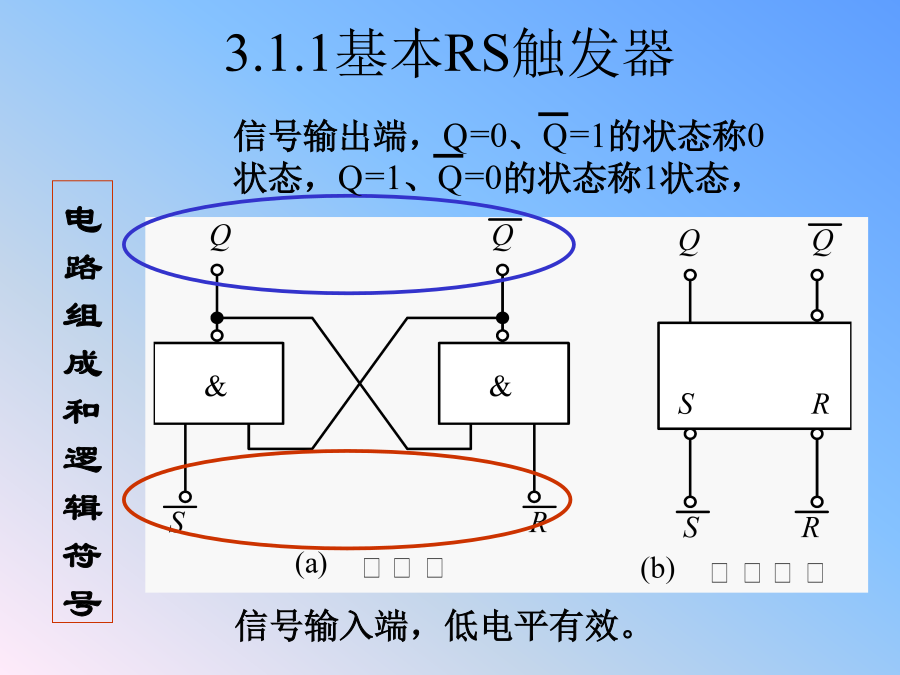

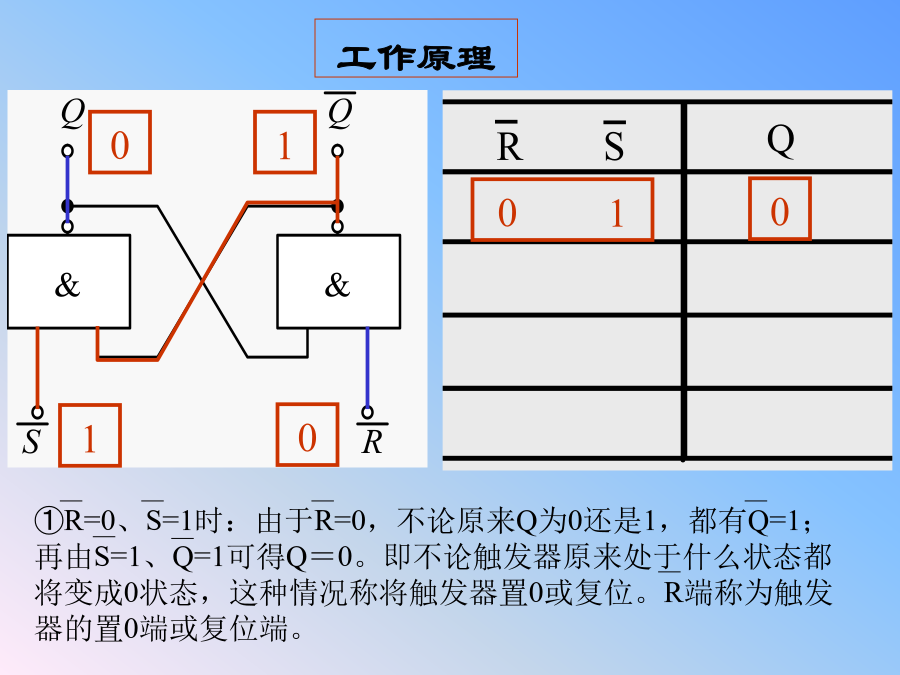

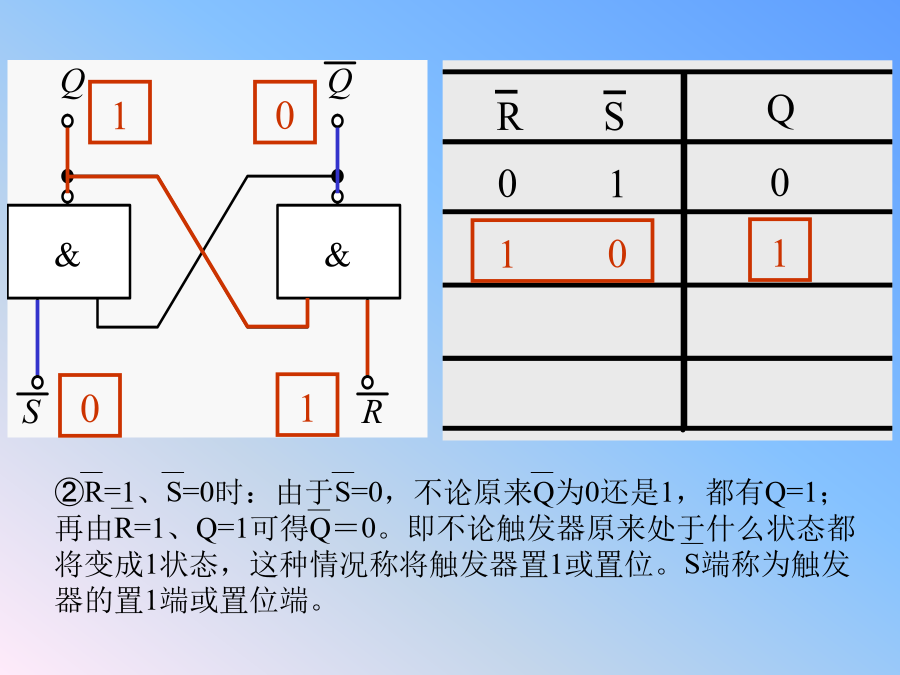

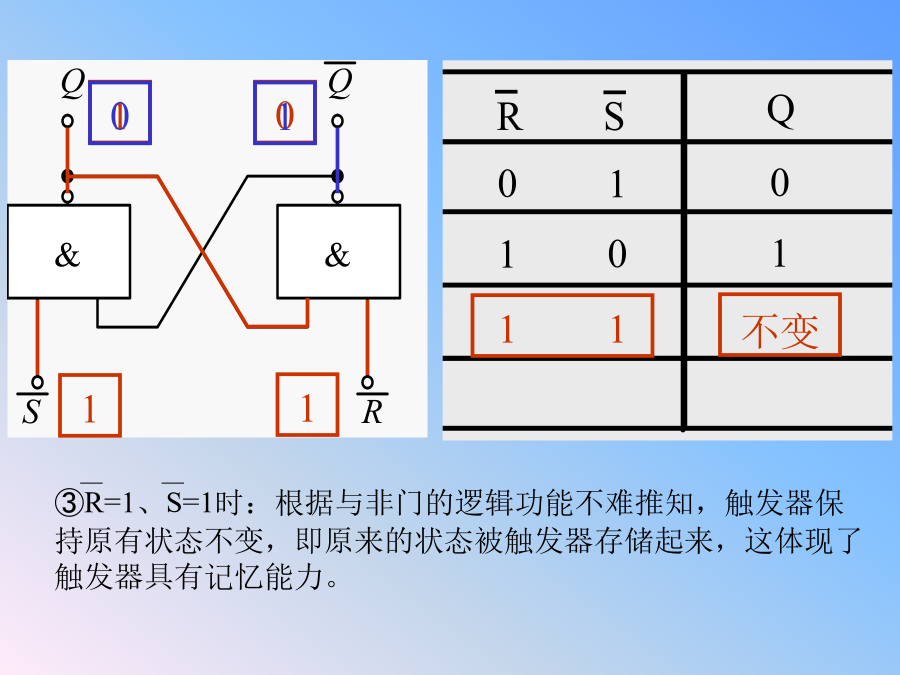

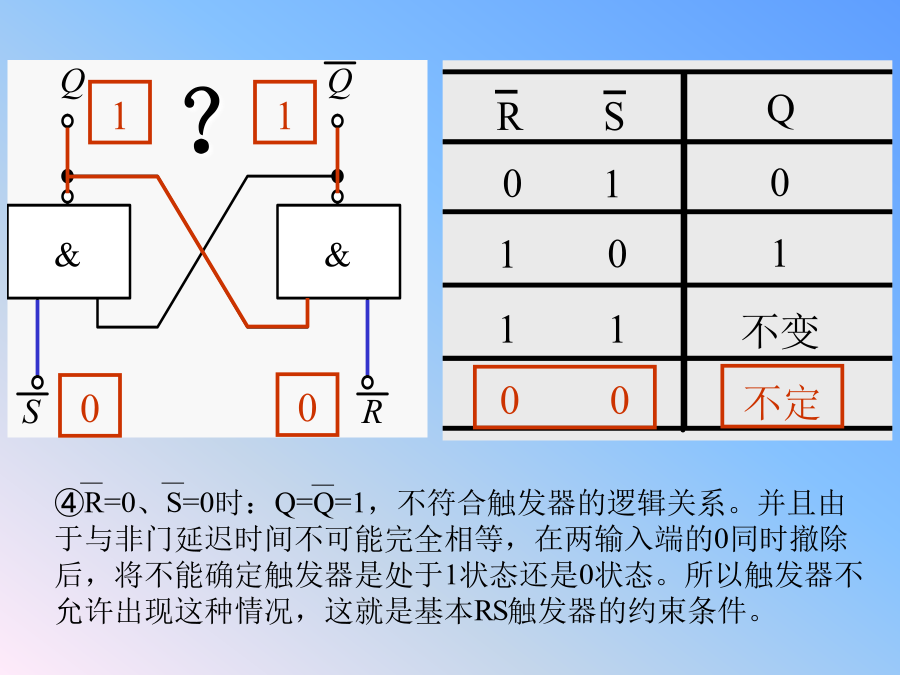

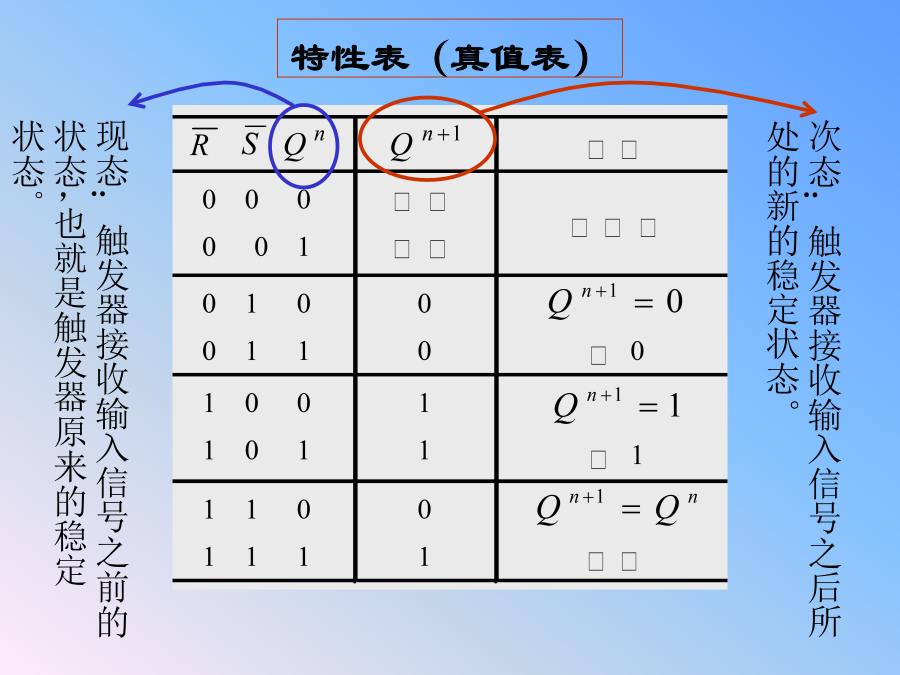

第三讲时序逻辑电路时序逻辑电路3.1触发器触发器是构成时序逻辑电路的基本逻辑部件。它有两个稳定的状态:0状态和1状态;在不同的输入情况下,它可以被置成0状态或1状态;当输入信号消失后,所置成的状态能够保持不变。电路组成和逻辑符号工作原理010特性表(真值表)次态Qn+1的卡诺图状态图波形图基本RS触发器的特点集成基本RS触发器1、同步RS触发器特性表主要特点2、同步JK触发器特性表状态图3、同步D触发器(D锁存器)状态图集成同步D触发器1、主从RS触发器0逻辑符号2、主从JK触发器特性表电路特点带清

《时序逻辑电路》.ppt

组合逻辑电路3.1组合逻辑电路特点3.1组合逻辑电路特点3.2小规模集成电路构成的组合电路的分析与设计3.2小规模集成电路构成的组合电路的分析与设计3.2小规模集成电路构成的组合电路的分析与设计3.2.2设计方法3.2.2设计方法3.2.2设计方法3.2.2设计方法3.2.2设计方法3.2.2设计方法3.3编码器3.3.1二进制编码器3.3.1二进制编码器3.3.1二进制编码器3.3.1二进制编码器3.3.2二进制优先编码器3.3.2二进制优先编码器3.3.2二进制优先编码器3.3.2二进制优先编码器3.

时序逻辑电路-.pptx

1组合电路与时序电路的区别3456789方法:将驱动方程代入JKFF的特性方程。1112图5-4时序图14151617181920212223242526272829RD'31323334353637383940414243444546474849505152535455序号575859606162636465666768697071100进制时序图(图5-38):737475解决方法Ⅱ:先第1片N→M1,第2片N→M2;再级联。77787980818283(1)列状态转换图/表其858687888990

时序逻辑电路.ppt

第6章时序逻辑电路一、时序逻辑电路概述组合逻辑电路:任何一个时刻的输出信号仅取决于当时的输入信号。时序逻辑电路:任何一个时刻的输出信号不仅取决于当时的输入信号,而且还取决于电路原来的工作状态。1、分析一个简单的时序逻辑电路。①组成:由两部分组成一部分是组合逻辑电路:3个与非门构成一部分是存储电路:由T触发器构成②分析:根据电路结构,可以写出T触发器的状态方程:Qn+1=[XQn+XQn]CP输出Z:Z=QnXCP③由上两式画出电路的工作波形。如下页图工作波形:3、时序逻辑电路的分类二时序逻辑电路的分析方法

时序逻辑电路.ppt

第21章触发器和时序逻辑电路21.1双稳态触发器触发器输出与输入的逻辑关系设原态为“0”态0