SDRAM原理及应用演示幻灯片.ppt

天真****目的

亲,该文档总共48页,到这已经超出免费预览范围,如果喜欢就直接下载吧~

相关资料

SDRAM原理及应用演示幻灯片.ppt

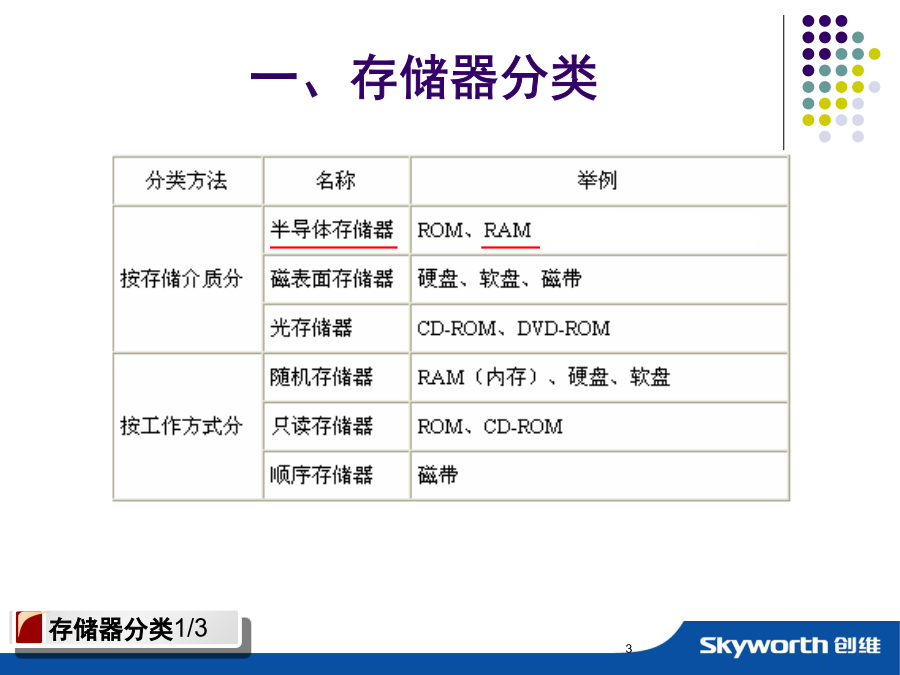

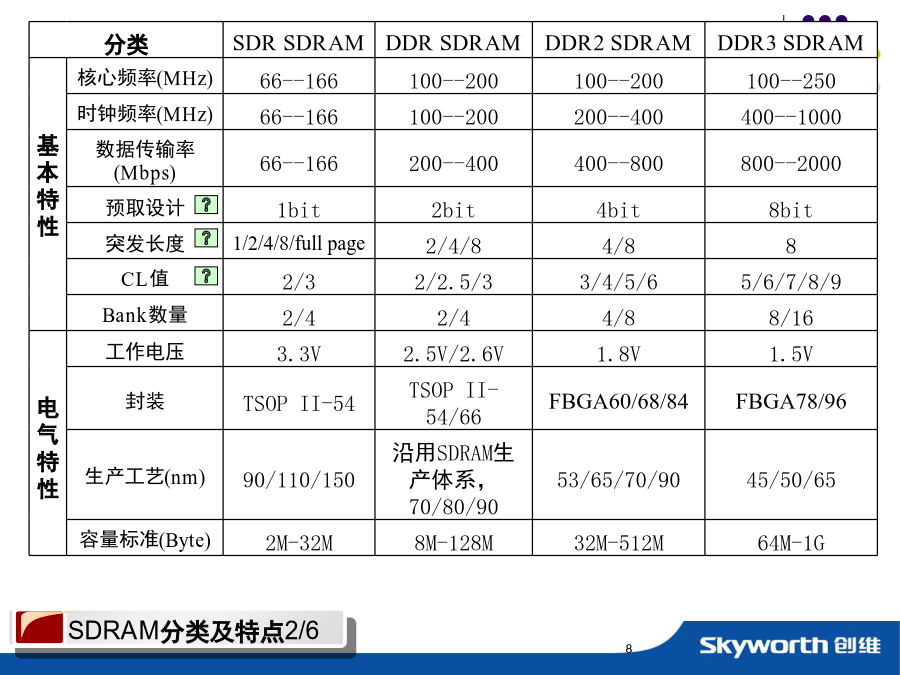

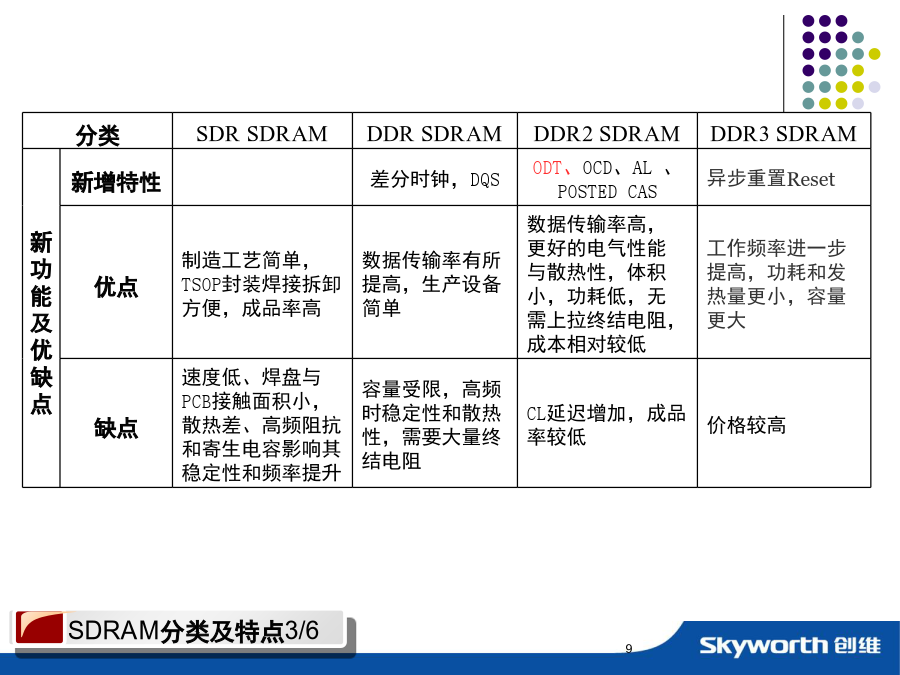

SDRAM原理及应用主要内容一、存储器分类随机存储器(RAM)和只读存储器(ROM)DRAM的特点二、SDRAM分类及特点SDRAM的分类分类分类关于频率和预取DRAM有两个时钟,一个是内部时钟,一个是外部时钟。在SDRAM与DDR1时代,这两个时钟频率是相同的,但在DDR2内存中,内部时钟变成了外部时钟的一半。以DDR2400为例说明,数据传输频率为400MHz(对于每个数据引脚,则是400Mbps/pin),外部时钟频率为200MHz,内部时钟频率为100MHz。因为内部一次传输的数据就可供外部接口传

红外遥控原理及应用演示幻灯片.ppt

红外遥控原理及应用一、红外遥控漫谈二、红外遥控系统遥控器的基本组成如图所示。它主要由形成遥控信号的微处理器芯片、晶体振荡器、放大晶体管、红外发光二极管以及键盘矩阵组成。注解:微处理器芯片IC1内部的振荡器通过2、3脚与外部的振荡晶体X组成一个高频振荡器,产生高频振荡信号。此信号送入定时信号发生器后进行分频产生正弦信号和定时脉冲信号。正弦信号送入编码调制器作为载波信号;定时脉冲信号送致扫描信号发生器、键控输入编码器和指令编码器作为这些电路的时间标准信号。IC1内部的扫描信号发生器产生五中不同时间的扫描脉冲信

NTC工作原理及应用演示幻灯片.ppt

主要内容一、概述二、NTC热敏电阻材料三、发展史四、基本物理特性五、应用六、原料及实验仪器原料及实验仪器原料及实验仪器七、实验步骤八、实验数据实验数据实验数据实验数据结束

第五讲-ADDA工作原理及应用演示幻灯片.ppt

第五讲A/D和D/A工作原理主要内容概述A/D工作原理量化编码AD芯片分类并行比较型ADC的转换原理逐次逼近式ADC的转换原理逐次逼近式的A/D转换器的特点双积分式A/D转换原理VFC式A/D转换原理∑-△型模数转换器A/D转换器的主要技术指标典型A/D转换芯片:AD0809ADC0809的工作过程例题一D/A工作原理转换原理D/A转换器的主要性能指标典型D/A转换芯片:DAC0832DAC0832内部结构及引脚DAC0832与80C51单片机的接口例题二作业

plasma原理演示幻灯片.ppt

等离子技术讲座:等离子原理及其应用PLASMATRAININGPROGRAM目录Agenda等离子技术在高级封装工业的应用PlasmaApplicationinAdvancedPackagingIndustries综述Overview:集成电路封装面临的挑战ICAssemblyandPackaging:SpecificChallenges等离子体应用PlasmaApplications表面活化:芯片粘结SurfaceActivation:DieAttach污染物去除:导线连接ContaminationRe