器件物理专题培训市公开课金奖市赛课一等奖课件.pptx

王子****青蛙

亲,该文档总共87页,到这已经超出免费预览范围,如果喜欢就直接下载吧~

相关资料

器件物理专题培训市公开课金奖市赛课一等奖课件.pptx

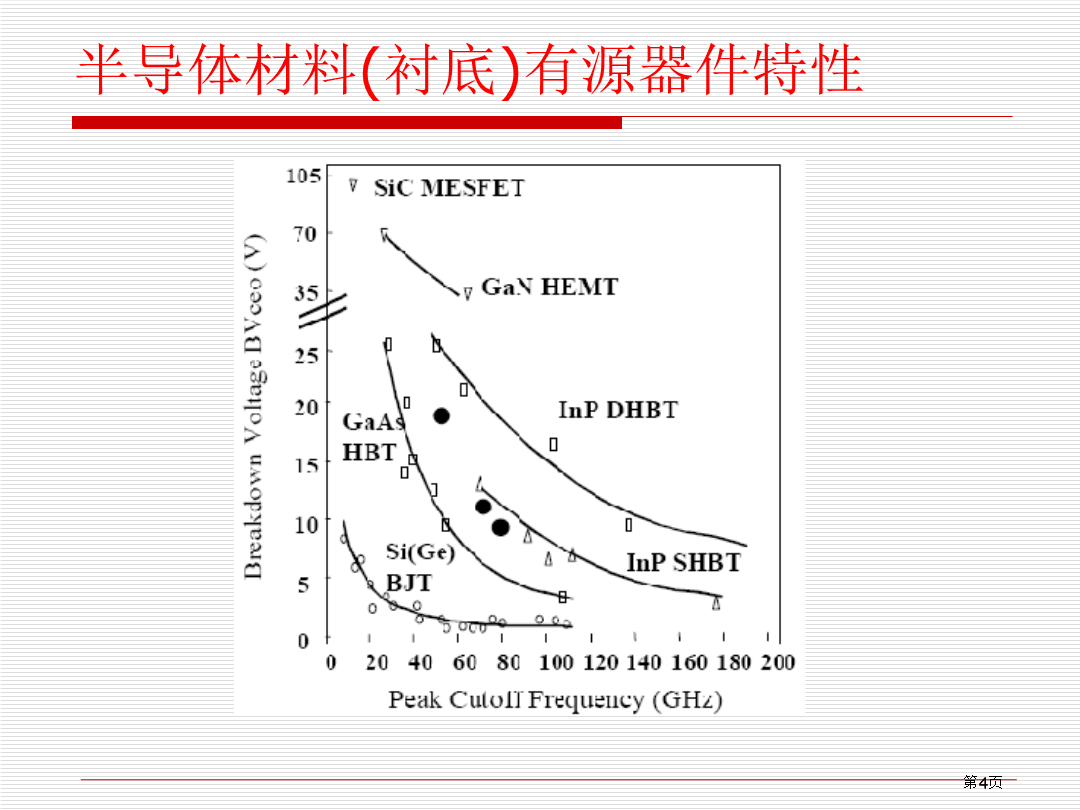

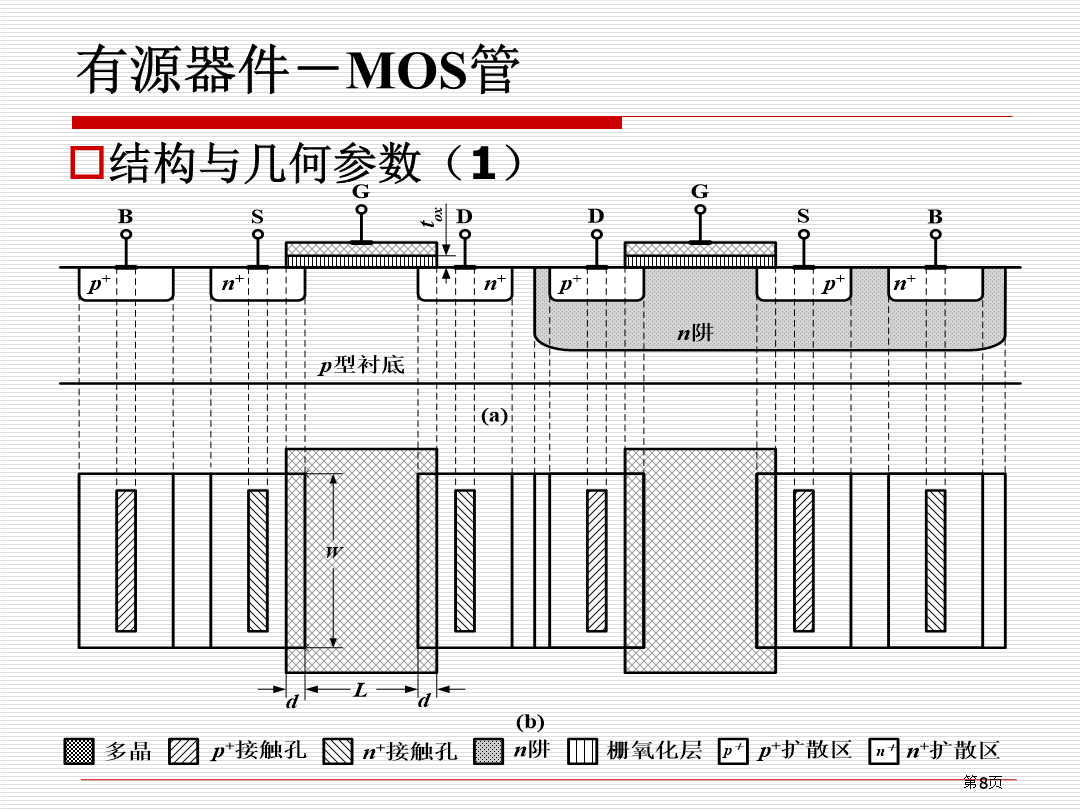

CMOS模拟集成电路分析与设计教材及参考书引言半导体材料(衬底)有源器件特性第一讲本章主要内容1、有源器件有源器件-MOS管结构与几何参数(2):在栅氧下衬底区域为器件有效工作区(即MOS管沟道)。MOS管两个有源区(源区与漏区)在制作时是几何对称:普通依据电荷输入与输出来定义源区与漏区:源端被定义为输出电荷(若为NMOS器件则为电子)端口;而漏端则为搜集电荷端口。当该器件三端电压发生改变时,源区与漏区就也许改变作用而互相互换定义。在模拟IC中还要考虑衬底(B)影响,衬底电位普通是通过一欧姆p+区(NMO

物理层专题培训市公开课金奖市赛课一等奖课件.pptx

计算机网络第2章物理层第2章物理层(续)2.1物理层基本概念2.2数据通信基础知识2.2.1数据通信系统模型几种术语模拟和数字数据、信号2.2.2相关信号几种基本概念基带(baseband)信号和宽带(broadband)信号2.2.3信道最高码元传播速率数字信号通过实际信道要强调下列两点要注意2.2.4信道极限信息传播速率香农公式表明奈氏准则和香农公式在数据通信系统中作用范围2.3物理层下面传播媒体2.3.1导向传播媒体各种电缆光线在光纤中折射光纤工作原理2.3.2非导向传播媒体2.4模拟传播与数字传播

诗律专题培训市公开课金奖市赛课一等奖课件.pptx

平仄我们现在普通话里有四个音调:阴平阳平平声上声去声入声而古时却多一个声调诗律一、什么是诗律诗律就是诗格律,即作诗规则。含义有二:广义:所有诗歌在句式、押韵等形式方面规则。狭义:特指近体诗在句式、押韵、平仄、对仗等形式方面规则和要求。近体诗(又称今体诗、格律诗):萌芽于六朝、成熟于唐代一个诗体,特点是:句数固定、押韵严格、讲究平仄、要求对仗。古诗古体诗(古风)近体诗(今体诗、格律诗)首联学诸进士作精卫衔石填海唐·韩愈鸟有偿冤者,终年抱寸诚。口衔山石细,心望海波平。渺渺功难见,区区命已轻。人皆讥造次,我独赏

物理组王伦专题培训市公开课金奖市赛课一等奖课件.pptx

复习课一、结识多用电表+二、多用电表原理欧姆表内部电路电流表改装成直接测量电阻欧姆表三、多用电表使用1、用多用电表测量小灯泡电压注意:红表笔接触点电势应比黑表笔高2、用多用电表测量通过小灯泡电流注意:电流应从红表笔流入电表3、用多用电表测量定值电阻4、测二极管正、反向电阻首先弄清两个问题:①二极管单向导电性。如图2.8-10:电流从正极流入电阻较小,从正极流出时电阻较大。四、多用电表读数1、最小分度是“1”仪器,测量误差出现在下一位,下一位按十分之一估读.2、最小分度是“2”或“5”仪器,测量误差出现在同

物理学史专题培训市公开课金奖市赛课一等奖课件.pptx

美籍中国物理学家杨振宁和李政道由于发觉在弱互相作用过程中宇称不守恒,共享了1957年度诺贝尔物理学奖。这是中国人初次取得诺贝尔物理学奖。能量守恒动量守恒角动量守恒宇称守恒由此相相应奇+偶=奇这种观点在20世纪50年代受到了来自弱互相作用方面冲击。这便是当初曾现在粒子物理学家面前一个著名矛盾,叫做“”之谜。为了揭开“”之谜,物理学家们发生了很大争论,无多物理学家想在不违反宇称守恒前提下解开这个谜,但是,我们杨振宁与李政道先生没有盲从,他们以惊人勇气与胆识对宇称守恒普遍性提出了怀疑。1956年夏天,杨振宁与李