2023年电大考试计算机组成原理期末套复习试题及答案参考资料小抄汇总.doc

胜利****实阿

亲,该文档总共148页,到这已经超出免费预览范围,如果喜欢就直接下载吧~

相关资料

2023年电大考试计算机组成原理期末套复习试题及答案参考资料小抄汇总.doc

计算机构成原理本科生期末试卷二选择题(每题1分,共10分)六七十年代,在美国旳______州,出现了一种地名叫硅谷。该地重要工业是______它也是______旳发源地。A马萨诸塞,硅矿产地,通用计算机B加利福尼亚,微电子工业,通用计算机C加利福尼亚,硅生产基地,小型计算机和微处理机D加利福尼亚,微电子工业,微处理机若浮点数用补码表达,则判断运算成果与否为规格化数旳措施是______。A阶符与数符相似为规格化数B阶符与数符相异为规格化数C数符与尾数小数点后第一位数字相异为规格化数D数符与尾数小数点后第一位

2023年电大考试计算机组成原理期末套复习试题及答案参考资料小抄汇总.doc

计算机构成原理本科生期末试卷二选择题(每题1分,共10分)六七十年代,在美国旳______州,出现了一种地名叫硅谷。该地重要工业是______它也是______旳发源地。A马萨诸塞,硅矿产地,通用计算机B加利福尼亚,微电子工业,通用计算机C加利福尼亚,硅生产基地,小型计算机和微处理机D加利福尼亚,微电子工业,微处理机若浮点数用补码表达,则判断运算成果与否为规格化数旳措施是______。A阶符与数符相似为规格化数B阶符与数符相异为规格化数C数符与尾数小数点后第一位数字相异为规格化数D数符与尾数小数点后第一位

电大考试《计算机组成原理》期末10套复习试题与答案参考资料小抄汇总精品.pdf

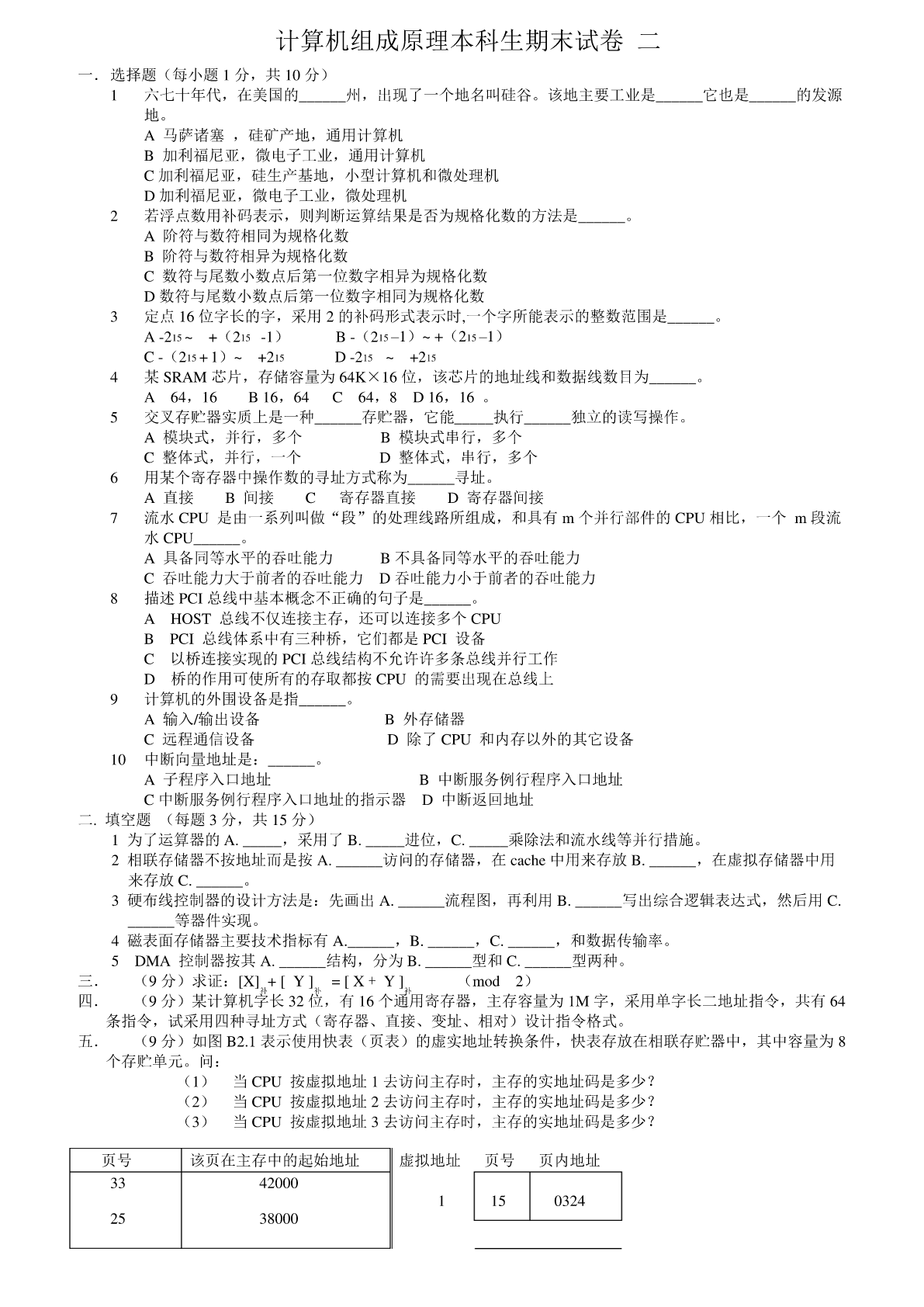

计算机组成原理本科生期末试卷二一.选择题(每小题1分,共10分)1六七十年代,在美国的______州,出现了一个地名叫硅谷。该地主要工业是______它也是______的发源地。A马萨诸塞,硅矿产地,通用计算机B加利福尼亚,微电子工业,通用计算机C加利福尼亚,硅生产基地,小型计算机和微处理机D加利福尼亚,微电子工业,微处理机2若浮点数用补码表示,则判断运算结果是否为规格化数的方法是______。A阶符与数符相同为规格化数B阶符与数符相异为规格化数C数符与尾数小数点后第一位数字相异为规格化数D数符与尾数小数

电大计算机组成原理期末考试试题及答案小抄.doc

.电大计算机组成原理期末考试试题及答案小抄选择题1、完整的计算机系统应包括______。DA.运算器、存储器和控制器B.外部设备和主机C.主机和实用程序D.配套的硬件设备和软件系统2、计算机系统中的存储器系统是指______。DA.RAM存储器B.ROM存储器C.主存储器D.主存储器和外存储器3、冯·诺依曼机工作方式的基本特点是______。BA.多指令流单数据流B.按地址访问并顺序执行指令C.堆栈操作D.存储器按内部选择地址4、下列说法中不正确的是______。DA.任何可以由软件实现的操作也可以由硬件

2017年电大计算机组成原理期末考试试题及答案小抄.doc

.电大计算机组成原理期末考试试题及答案小抄选择题1、完整的计算机系统应包括______。DA.运算器、存储器和控制器B.外部设备和主机C.主机和实用程序D.配套的硬件设备和软件系统2、计算机系统中的存储器系统是指______。DA.RAM存储器B.ROM存储器C.主存储器D.主存储器和外存储器3、冯·诺依曼机工作方式的基本特点是______。BA.多指令流单数据流B.按地址访问并顺序执行指令C.堆栈操作D.存储器按内部选择地址4、下列说法中不正确的是______。DA.任何可以由软件实现的操作也可以由硬件