正负脉宽数控调制信号发生器的设计.doc

黛娥****ak

在线预览结束,喜欢就下载吧,查找使用更方便

相关资料

正负脉宽数控调制信号发生器.pdf

EDA设计基础实验课程论文题目正负脉宽数控调制信号发生器学院专业班级通信班学生姓名大彬哥指导教师大力会EDA设计基础实验课程论文摘要介绍了Verilog-HDL语言在正负脉宽数控调制信号发生器中的具体应用,给出了仿真波形,说明了实现电子电路的自动化设计(EDA)过程和EDA技术在现代数字系统中的重要地位及作用.关键词:Verilog-HDLEDA仿真IEDA设计基础实验课程论文AbstractIntroducestheVerilogHDL-languageinpositiveandnegativepuls

正负脉宽数控调制信号发生器的设计.doc

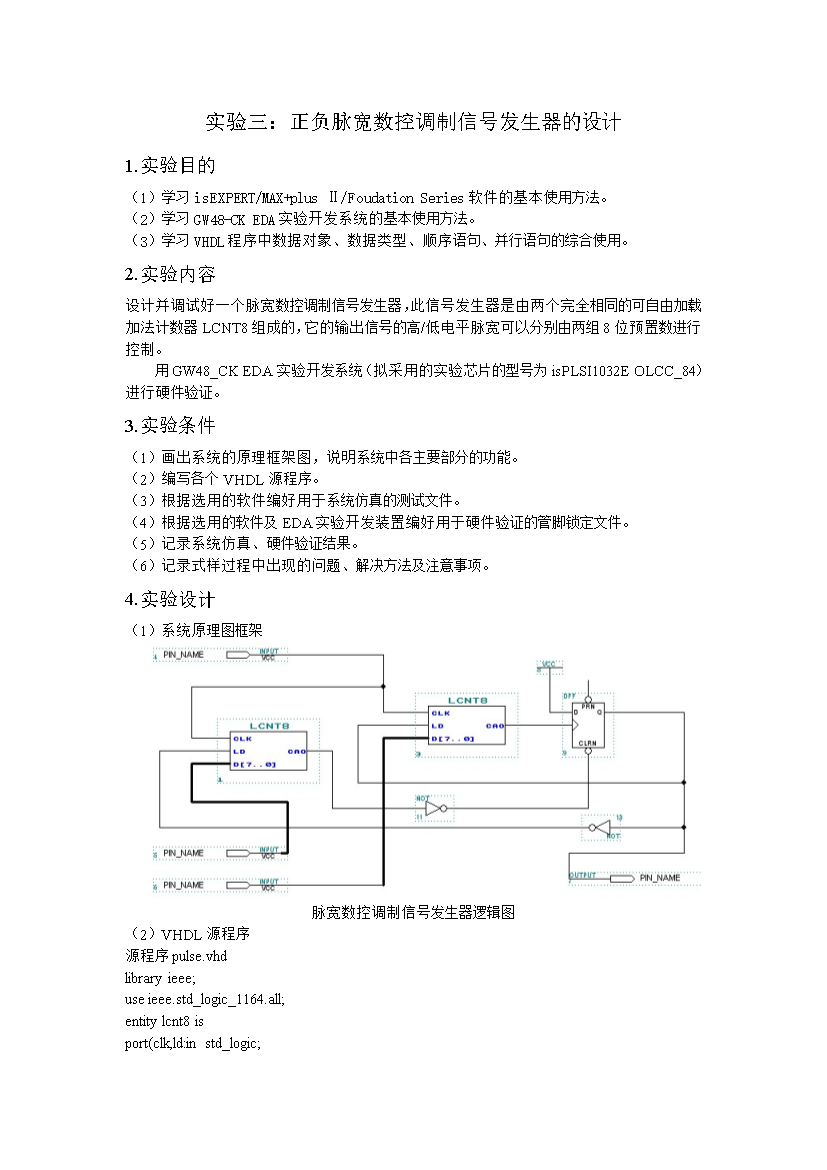

实验三:正负脉宽数控调制信号发生器的设计1.实验目的(1)学习isEXPERT/MAX+plusⅡ/FoudationSeries软件的基本使用方法。(2)学习GW48-CKEDA实验开发系统的基本使用方法。(3)学习VHDL程序中数据对象、数据类型、顺序语句、并行语句的综合使用。2.实验内容设计并调试好一个脉宽数控调制信号发生器此信号发生器是由两个完全相同的可自由加载加法计数器LCNT8组成的它的输出信号的高/低电平脉宽可以分别由两组8位预置数进行控制。用GW48_CKEDA实验开发系统(拟采用

正负脉宽数控调制信号发生器的设计.doc

实验三:正负脉宽数控调制信号发生器的设计1.实验目的(1)学习isEXPERT/MAX+plusⅡ/FoudationSeries软件的基本使用方法。(2)学习GW48-CKEDA实验开发系统的基本使用方法。(3)学习VHDL程序中数据对象、数据类型、顺序语句、并行语句的综合使用。2.实验内容设计并调试好一个脉宽数控调制信号发生器,此信号发生器是由两个完全相同的可自由加载加法计数器LCNT8组成的,它的输出信号的高/低电平脉宽可以分别由两组8位预置数进行控制。用GW48_CKEDA实验开发系统(拟采用的实

正负脉宽数控调制信号发生器的设计.doc

实验三:正负脉宽数控调制信号发生器的设计1.实验目的(1)学习isEXPERT/MAX+plusⅡ/FoudationSeries软件的基本使用方法。(2)学习GW48-CKEDA实验开发系统的基本使用方法。(3)学习VHDL程序中数据对象、数据类型、顺序语句、并行语句的综合使用。2.实验内容设计并调试好一个脉宽数控调制信号发生器,此信号发生器是由两个完全相同的可自由加载加法计数器LCNT8组成的,它的输出信号的高/低电平脉宽可以分别由两组8位预置数进行控制。用GW48_CKEDA实验开发系统(拟采用的实

最新精编医学专题—正负脉宽数控调制信号发生器.docx

EDA设计基础实验课程论文22EDA设计基础实验课程论文题目正负脉宽数控调制信号发生器学院专业班级通信班学生姓名大彬哥指导教师大力会摘要介绍了Verilog-HDL语言在正负脉宽数控调制信号发生器中的具体应用