ARM简介及其ARM体系结构.pptx

胜利****实阿

亲,该文档总共111页,到这已经超出免费预览范围,如果喜欢就直接下载吧~

相关资料

ARM简介及其ARM体系结构.pptx

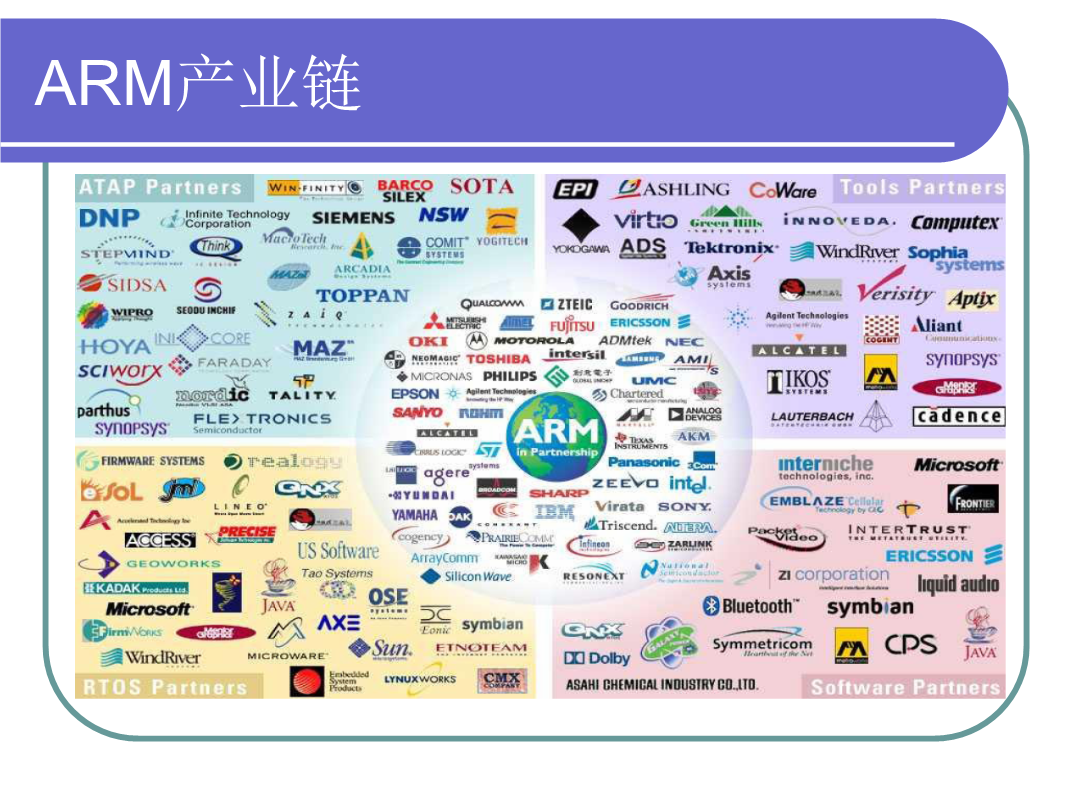

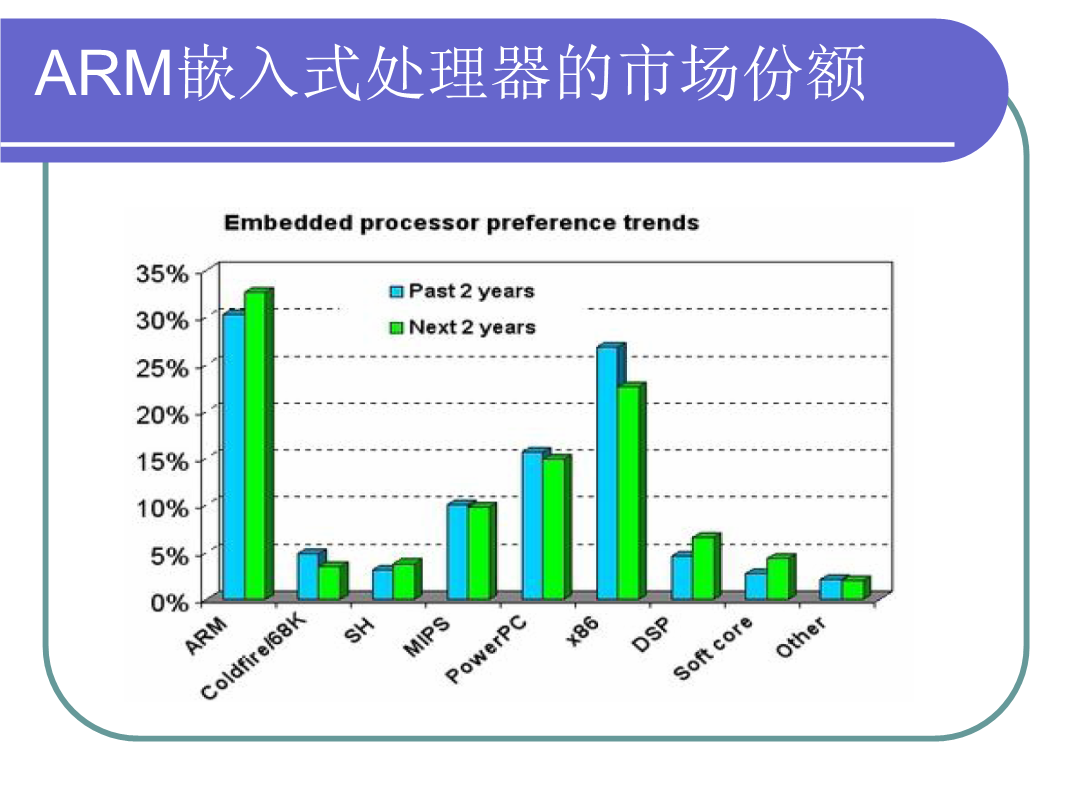

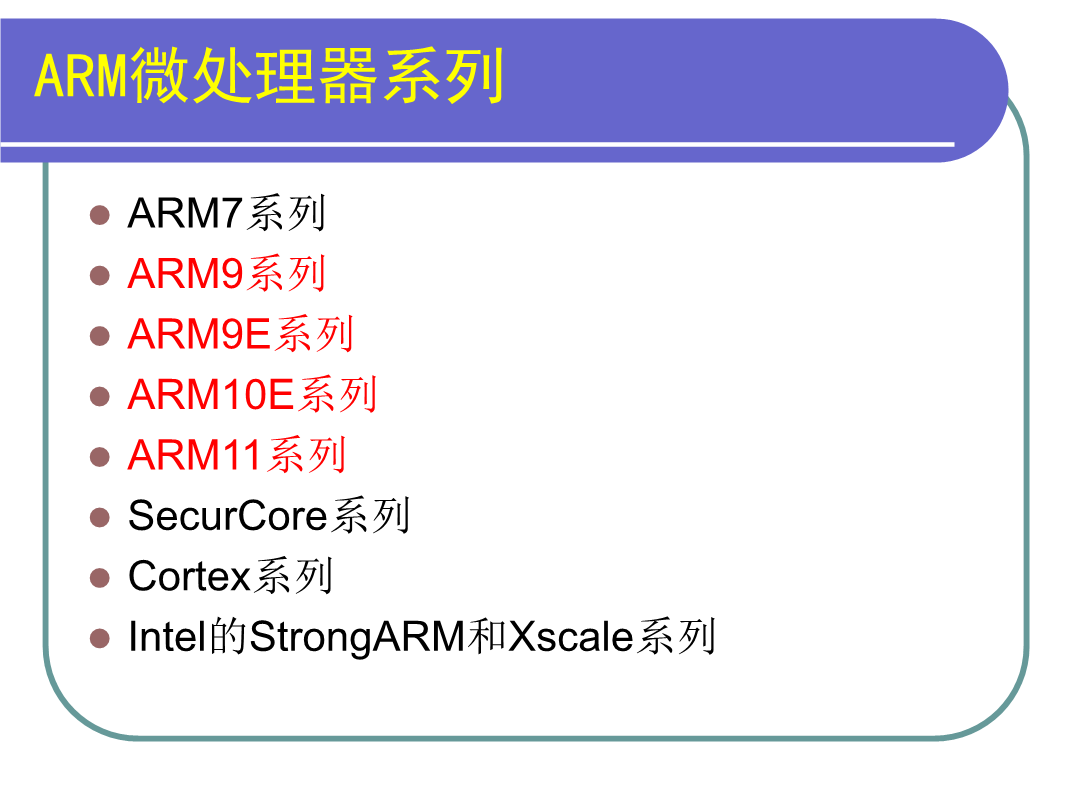

提要ARM简介3.1ARM简介ARM产业链ARM公司分支ARM嵌入式处理器的市场份额ARM应用领域ARM微处理器的应用领域ARM微处理器系列ARM体系结构的命名规则本节提要ARM基础知识ARM(IP核)体系结构32位机处理器的2种工作状态处理器模式操作系统体系结构处理器工作模式(2)处理器工作模式(3)ARM的寄存器个数寄存器类别寄存器类别寄存器类别寄存器类别寄存器类别寄存器类别寄存器类别寄存器类别寄存器类别寄存器类别Lable内部寄存器内部寄存器内部寄存器内部寄存器寄存器类别内部寄存器内部寄存器内部寄存

ARM技术与ARM体系结构.ppt

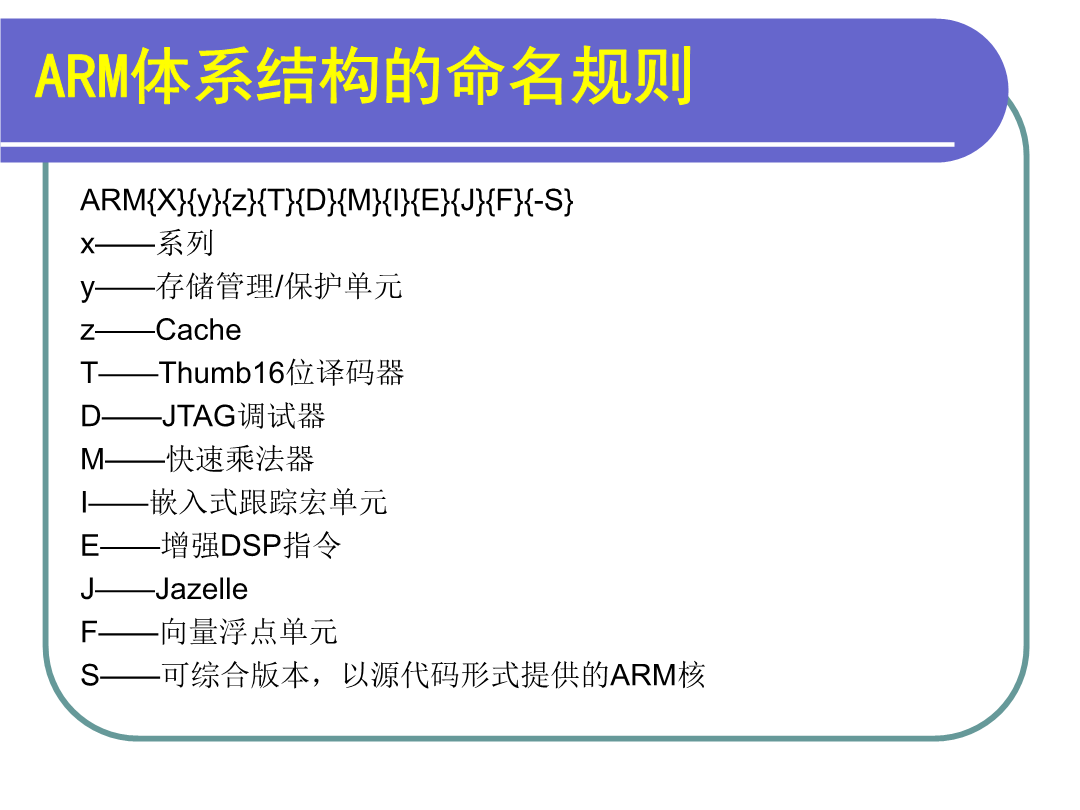

第2章ARM技术与ARM体系结构内容提要2.1ARM体系结构版本与内核2.1.1ARM体系结构版本2.1.2ARM体系结构的基本版本命名规则续ARM体系结构的基本版本2.2ARM内核模块ARM调试结构2.2.1ARM7TDMI-S内核结构ARM7TDMIARM7TDMI内核信号ARM7TDMI方框图外部地址产生T标志位的作用带Cache的ARM7TDMI2.2.2ARM9内核结构ARM920的5级流水线操作2.3ARM处理器的工作模式ARM处理器共有7种工作模式2.4内部寄存器寄存器组织概要ARM寄存器程

ARM技术与ARM体系结构.ppt

第2章ARM技术与ARM体系结构内容提要2.1ARM体系结构版本与内核2.1.1ARM体系结构版本2.1.2ARM体系结构的基本版本命名规则续ARM体系结构的基本版本2.2ARM内核模块ARM调试结构2.2.1ARM7TDMI-S内核结构ARM7TDMIARM7TDMI内核信号ARM7TDMI方框图外部地址产生T标志位的作用带Cache的ARM7TDMI2.2.2ARM9内核结构ARM920的5级流水线操作2.3ARM处理器的工作模式ARM处理器共有7种工作模式2.4内部寄存器寄存器组织概要ARM寄存器程

ARM体系结构及常用接口简介解析.ppt

1ARM-AdvancedRISCMachinesARM公司的Chipless模式ARM微处理器的特点—低功耗、低成本、高性能ARM微处理器的特点—采用RISC体系结构ARM微处理器的特点—大量使用寄存器ARM微处理器的特点—高效的指令系统ARM微处理器的特点—其他技术ARM微处理器系列ARM处理器核心技术演进路线ARM9微处理器系列ARM9微处理器系列ARM920T系统结构分析ARM920T系统结构分析嵌入式微处理器ARM微处理器的工作状态ARM微处理器:处理器工作状态ARM微处理器:处理器工作状态AR

ARM体系结构及常用接口简介解析.ppt

第二章ARM体系结构及常用接口简介ARM-AdvancedRISCMachinesARM公司的Chipless模式ARM微处理器的特点—低功耗、低成本、高性能ARM微处理器的特点—采用RISC体系结构ARM微处理器的特点—大量使用寄存器ARM微处理器的特点—高效的指令系统ARM微处理器的特点—其他技术ARM微处理器系列ARM处理器核心技术演进路线ARM9微处理器系列ARM9微处理器系列ARM920T系统结构分析ARM920T系统结构分析嵌入式微处理器ARM微处理器的工作状态ARM微处理器:处理器工作状态A