基于FPGA的SPI接口设计说明.doc

胜利****实阿

亲,该文档总共16页,到这已经超出免费预览范围,如果喜欢就直接下载吧~

相关资料

基于FPGA的SPI接口设计说明.doc

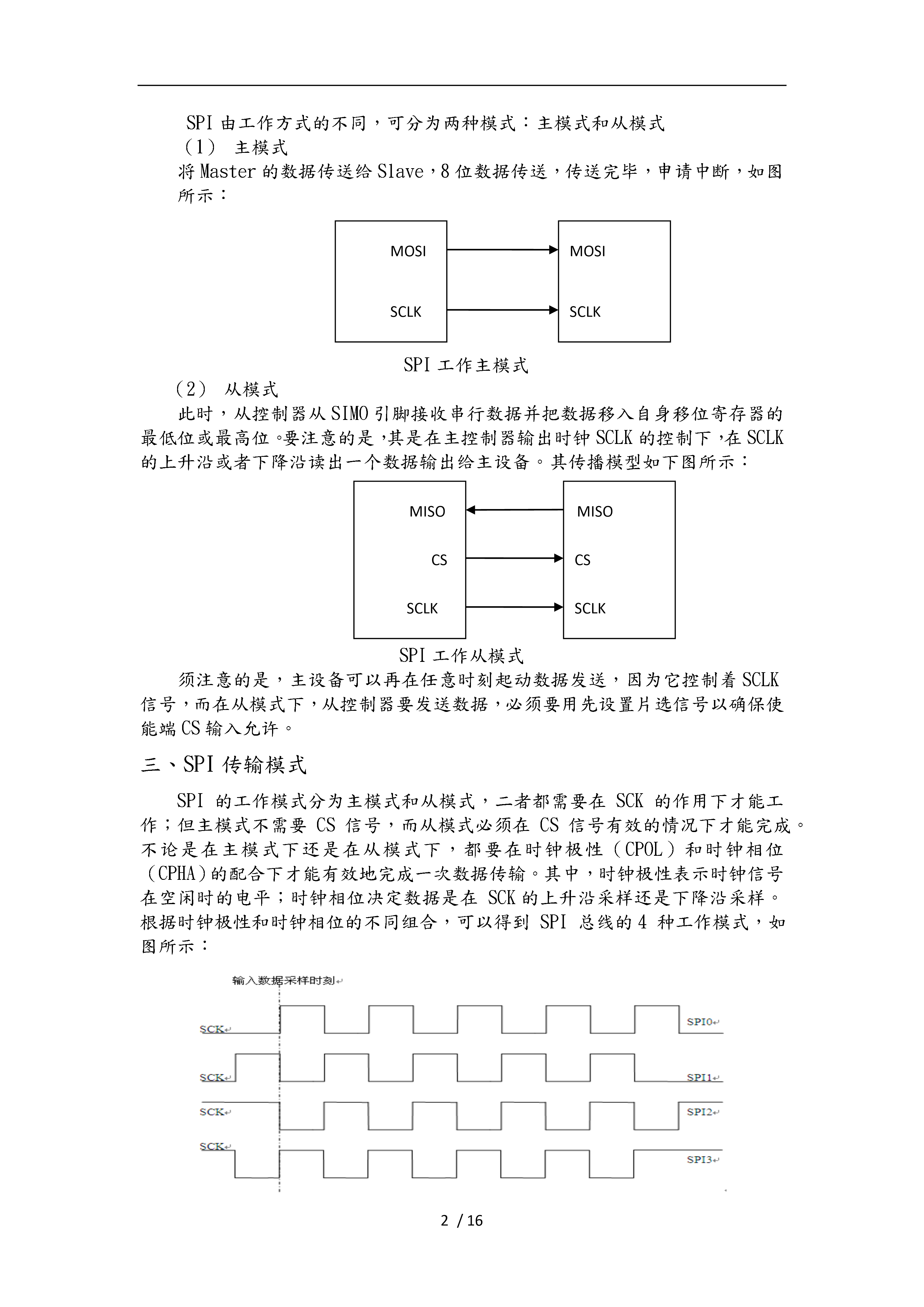

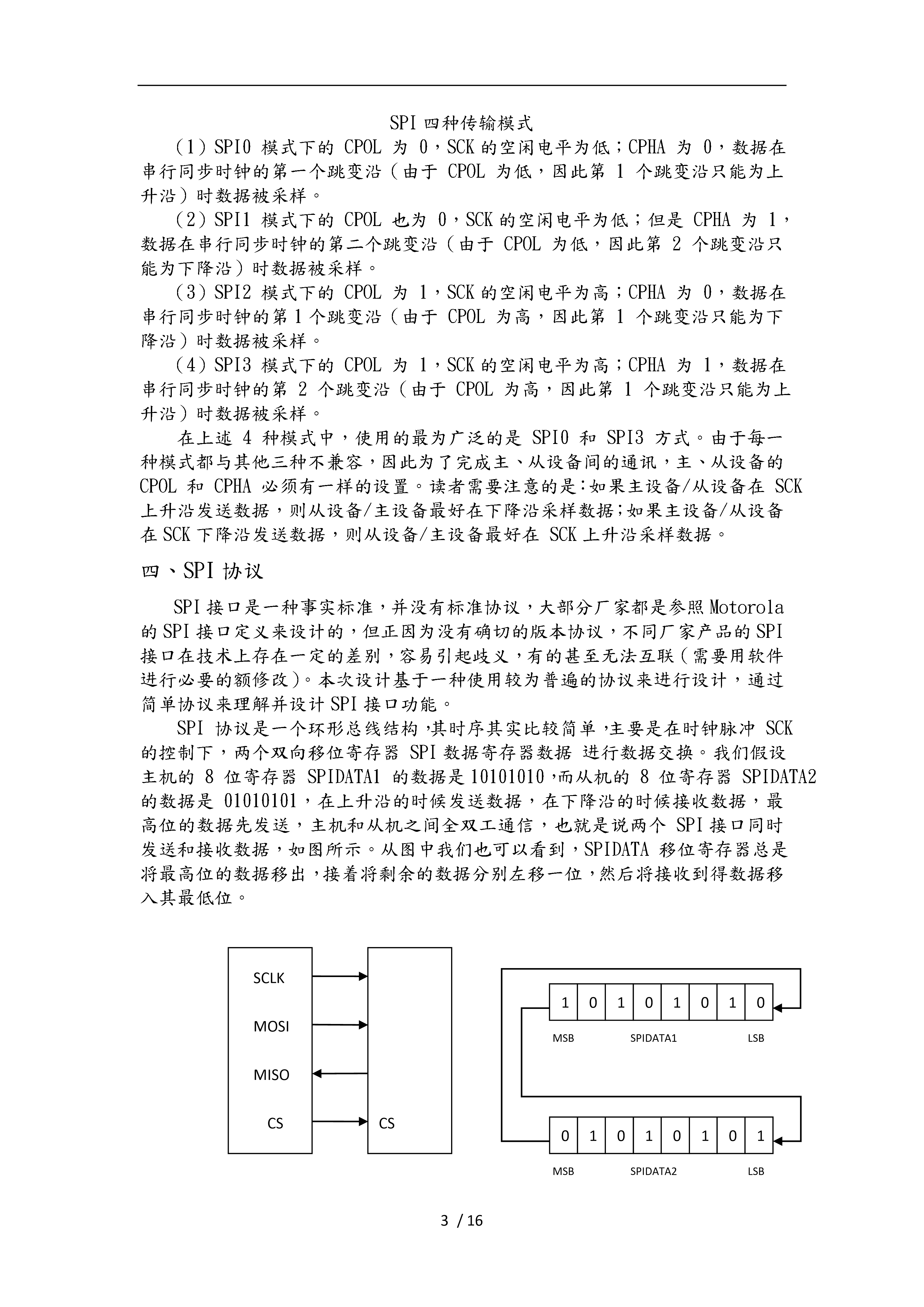

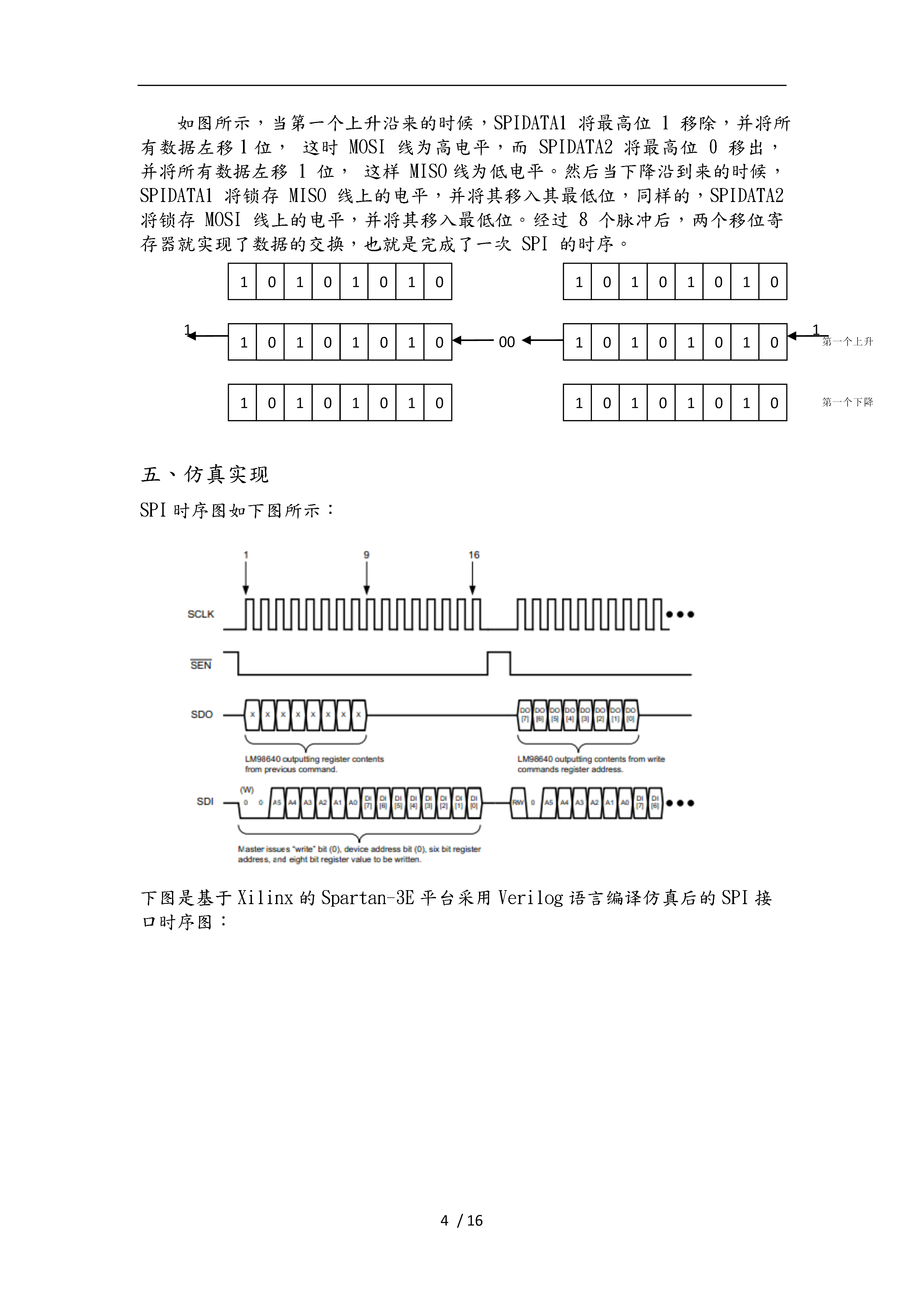

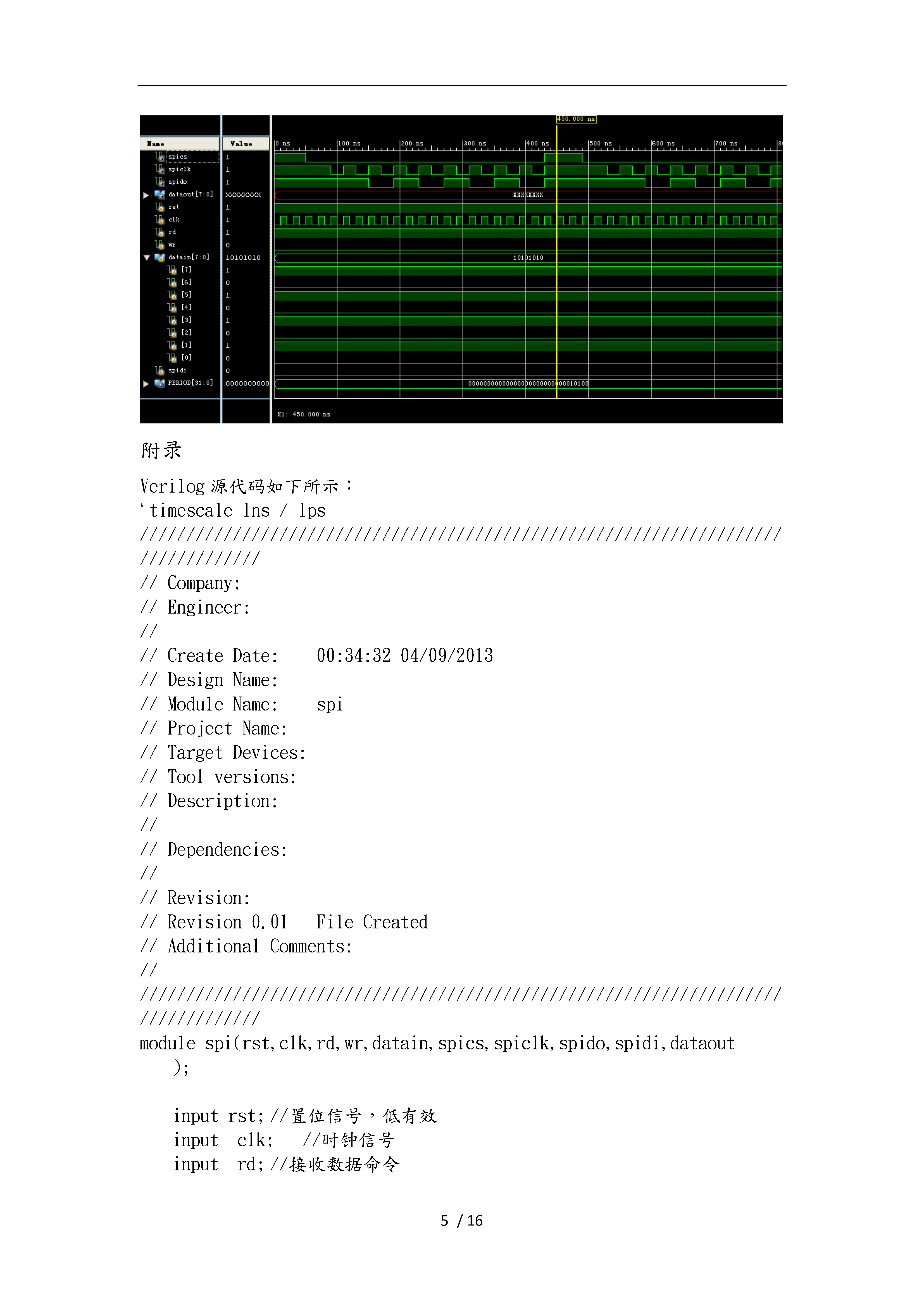

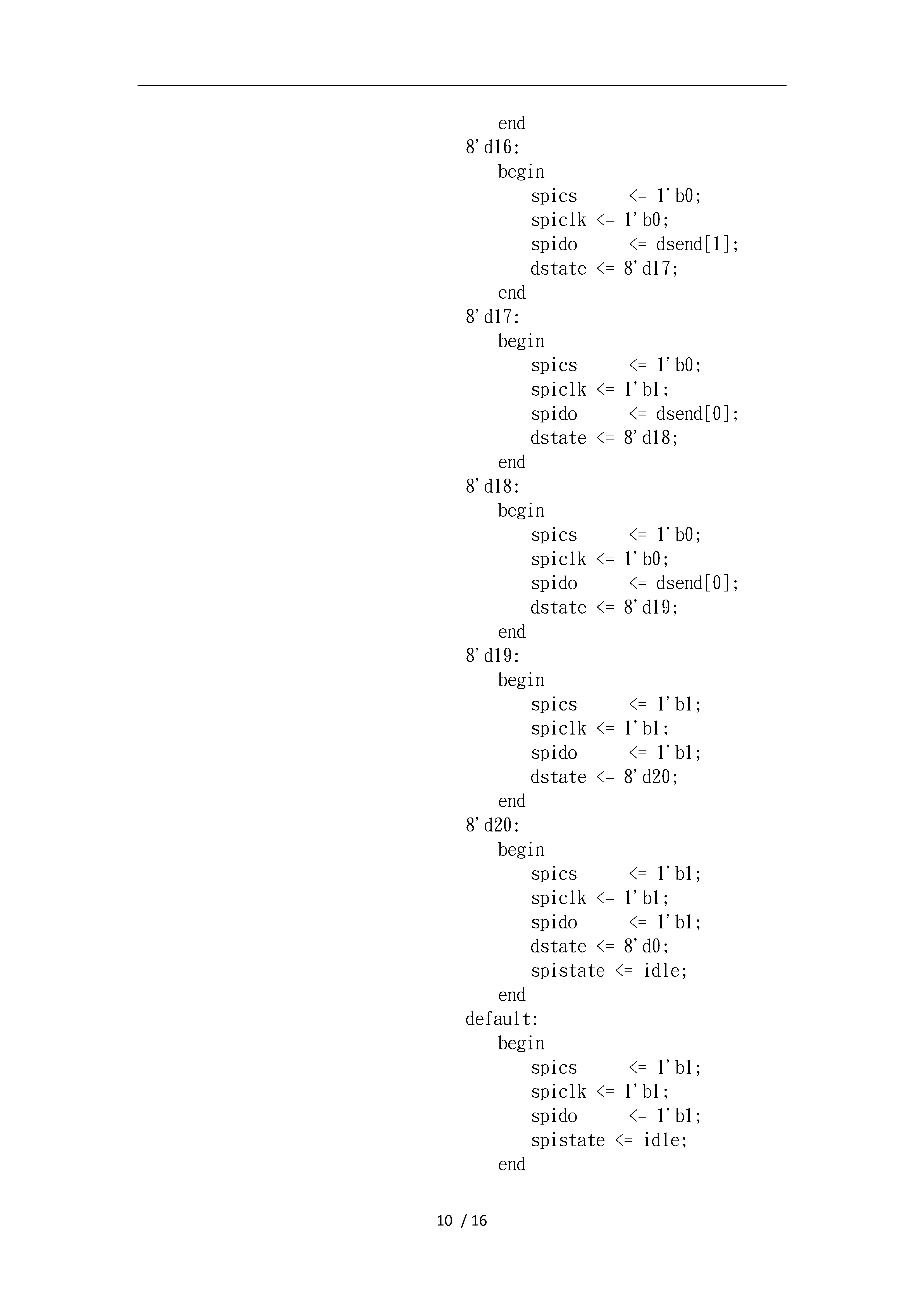

16/16基于ISE的SPI接口的仿真设计一、SPI介绍SPI总线系统是一种同步串行外设接口,它可以使MCU与各种外围设备以串行方式进行通信以交换信息。外围设置FLASHRAM、网络控制器、LCD显示驱动器、A/D转换器和MCU等。SPI总线系统可直接与各个厂家生产的多种标准外围器件直接接口,该接口一般使用4条线:串行时钟线(SCK)、主机输入/从机输出数据线MISO、主机输出/从机输入数据线MOST和低电平有效的从机选择线SS(有的SPI接口芯片带有中断信号线INT或INT、有的SPI接口芯片没有主机输

基于FPGA的SPI4.2接口设计.docx

基于FPGA的SPI4.2接口设计SPI4.2(ScalableParallelInterface4.2)是一种高速串行接口,用于连接网络交换机芯片中的各个模块。基于FPGA的SPI4.2接口设计是一项挑战性的工作,要求FPGA能够实现SPI4.2协议的各种功能,同时具备高性能和可扩展性。一、SPI4.2协议概述SPI4.2协议是传输高速数据的一种串行接口协议。它是适用于网络交换机的接口协议,采用高速串行数据传输技术,可以保证数据传输的可靠性和稳定性。SPI4.2协议支持多个数据通道的并行传输,其中包括元

(整理)基于FPGA的SPI接口设计-徐慧军.doc

(整理)基于FPGA的SPI接口设计-徐慧军.(整理)基于FPGA的SPI接口设计-徐慧军.精品文档精品文档(整理)基于FPGA的SPI接口设计-徐慧军.精品文档基于ISE的SPI接口的仿真设计一、SPI介绍SPI总线系统是一种同步串行外设接口,它可以使MCU与各种外围设备以串行方式进行通信以交换信息。外围设置FLASHRAM、网络控制器、LCD显示驱动器、A/D转换器和MCU等。SPI总线系统可直接与各个厂家生产的多种标准外围器件直接接口,该接口一般使用4条线:串行时钟线(SCK)、主机输入/从机输出数

(整理)基于FPGA的SPI接口设计-徐慧军..doc

(整理)基于FPGA的SPI接口设计-徐慧军.(整理)基于FPGA的SPI接口设计-徐慧军.精品文档精品文档(整理)基于FPGA的SPI接口设计-徐慧军.精品文档基于ISE的SPI接口的仿真设计一、SPI介绍SPI总线系统是一种同步串行外设接口,它可以使MCU与各种外围设备以串行方式进行通信以交换信息。外围设置FLASHRAM、网络控制器、LCD显示驱动器、A/D转换器和MCU等。SPI总线系统可直接与各个厂家生产的多种标准外围器件直接接口,该接口一般使用4条线:串行时钟线(SCK)、主机输入/从机输出数

(完整word版)基于FPGA的SPI接口设计-徐慧军.doc

基于ISE的SPI接口的仿真设计一、SPI介绍SPI总线系统是一种同步串行外设接口,它可以使MCU与各种外围设备以串行方式进行通信以交换信息。外围设置FLASHRAM、网络控制器、LCD显示驱动器、A/D转换器和MCU等。SPI总线系统可直接与各个厂家生产的多种标准外围器件直接接口,该接口一般使用4条线:串行时钟线(SCK)、主机输入/从机输出数据线MISO、主机输出/从机输入数据线MOST和低电平有效的从机选择线SS(有的SPI接口芯片带有中断信号线INT或INT、有的SPI接口芯片没有主机输出/从机输