信号波形处理设计论文.doc

胜利****实阿

亲,该文档总共11页,到这已经超出免费预览范围,如果喜欢就直接下载吧~

相关资料

信号波形处理设计论文.doc

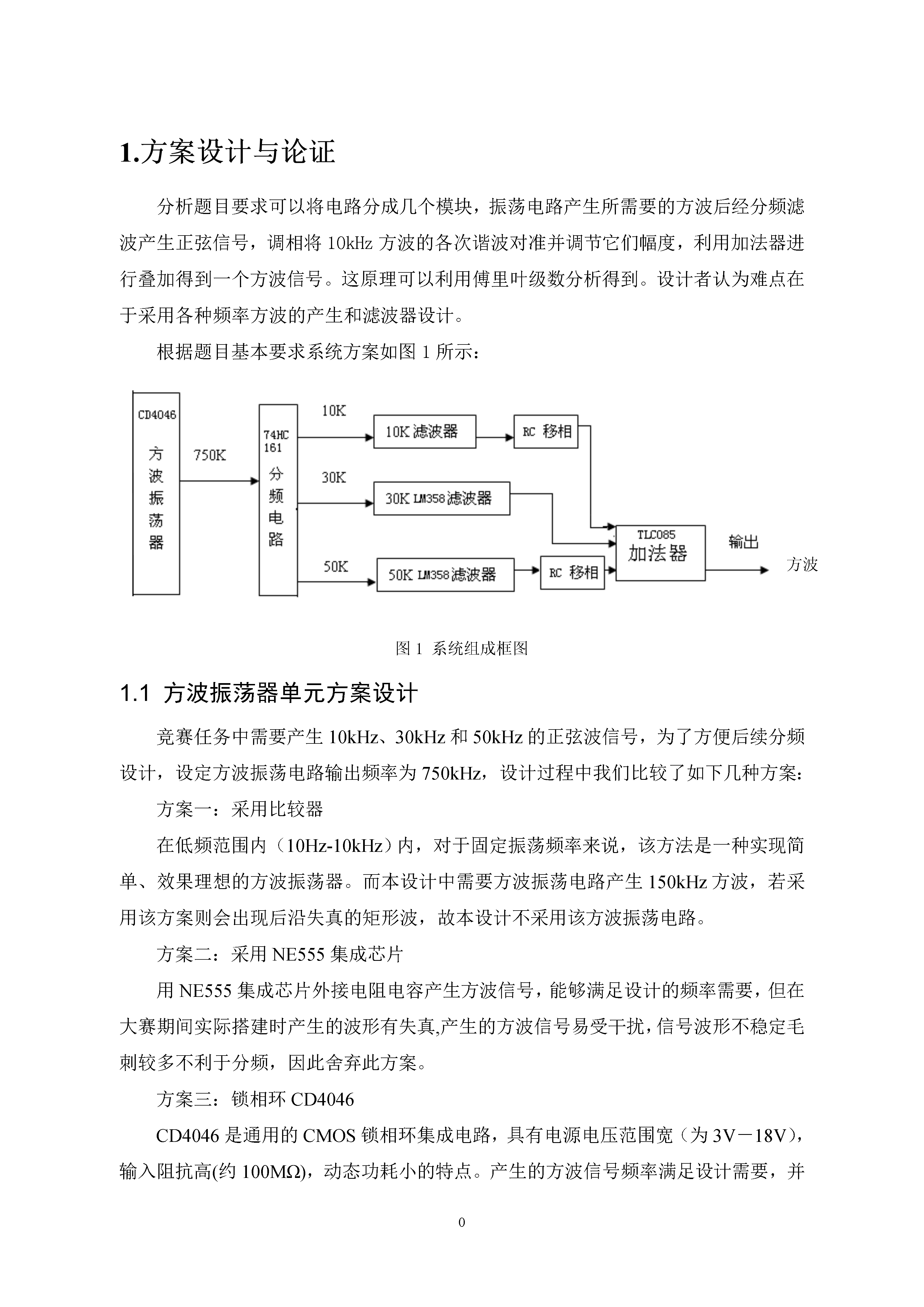

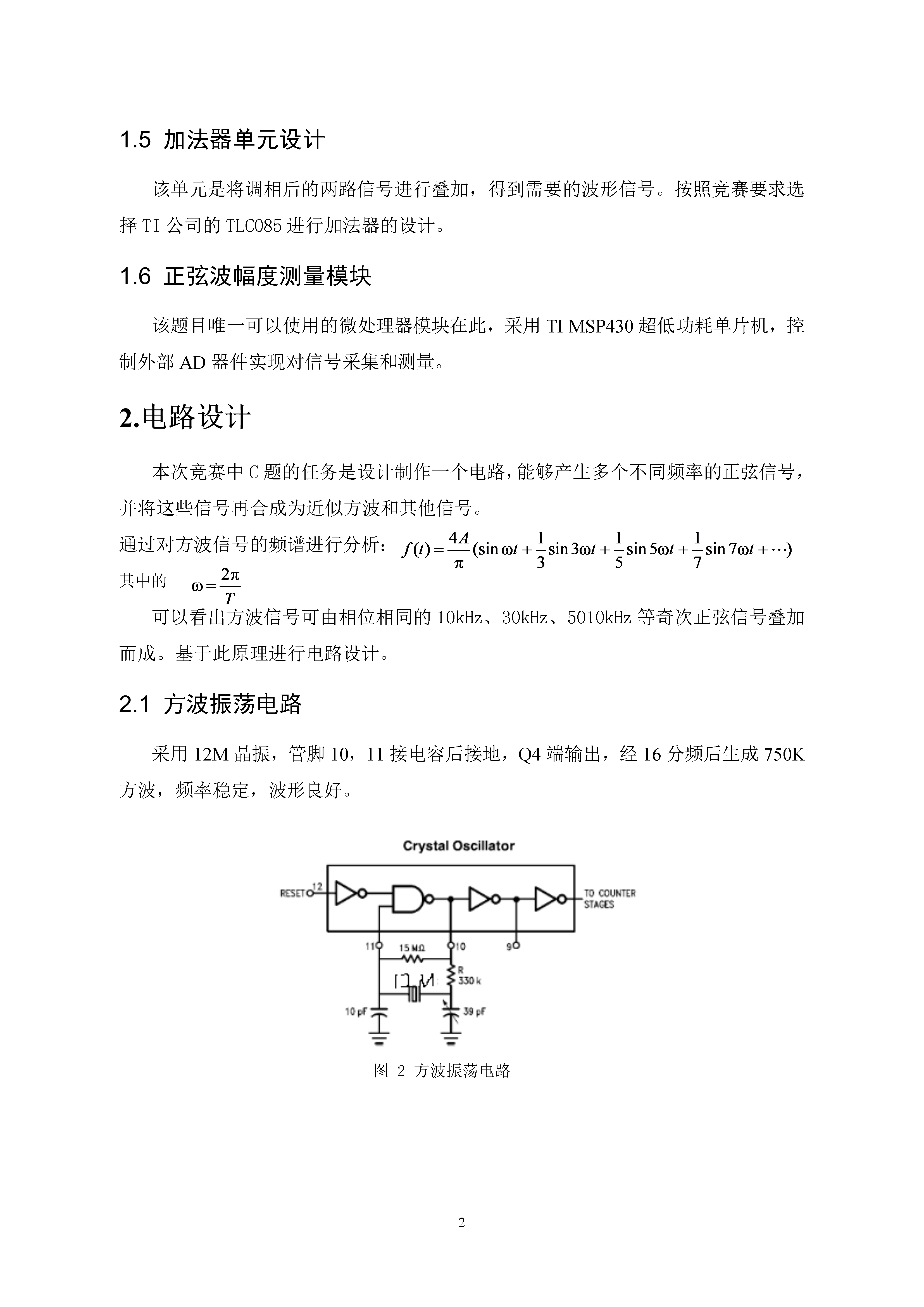

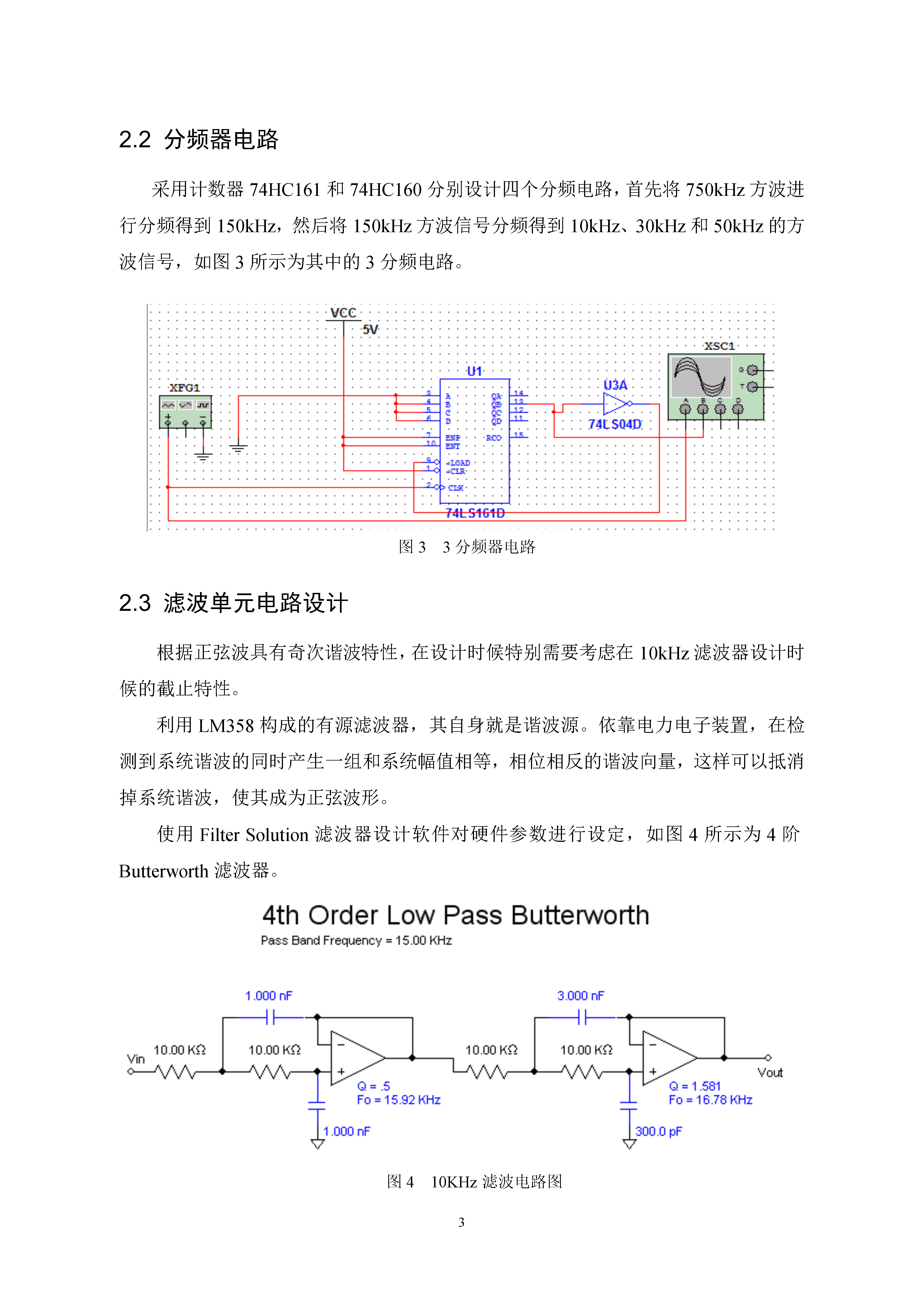

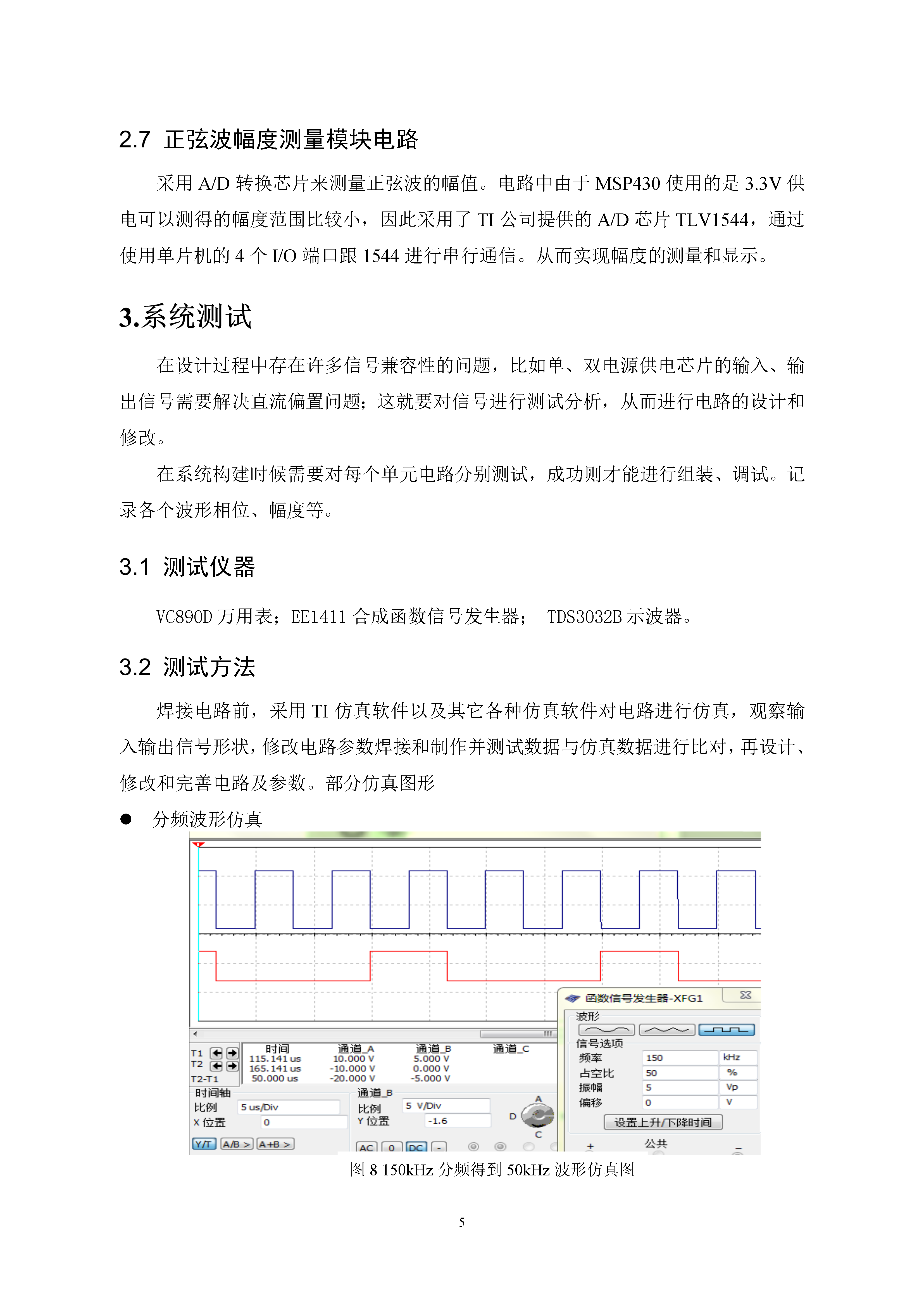

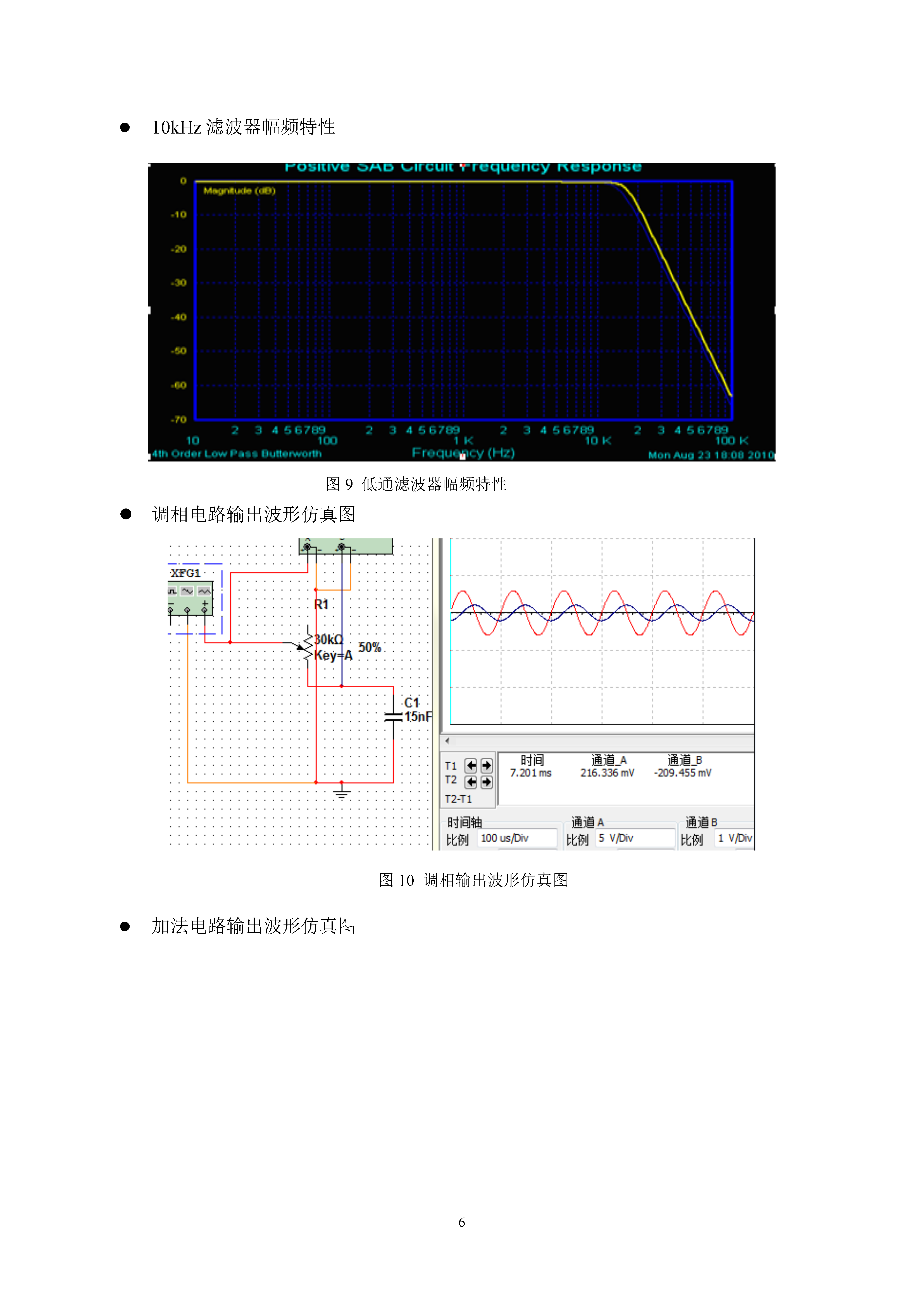

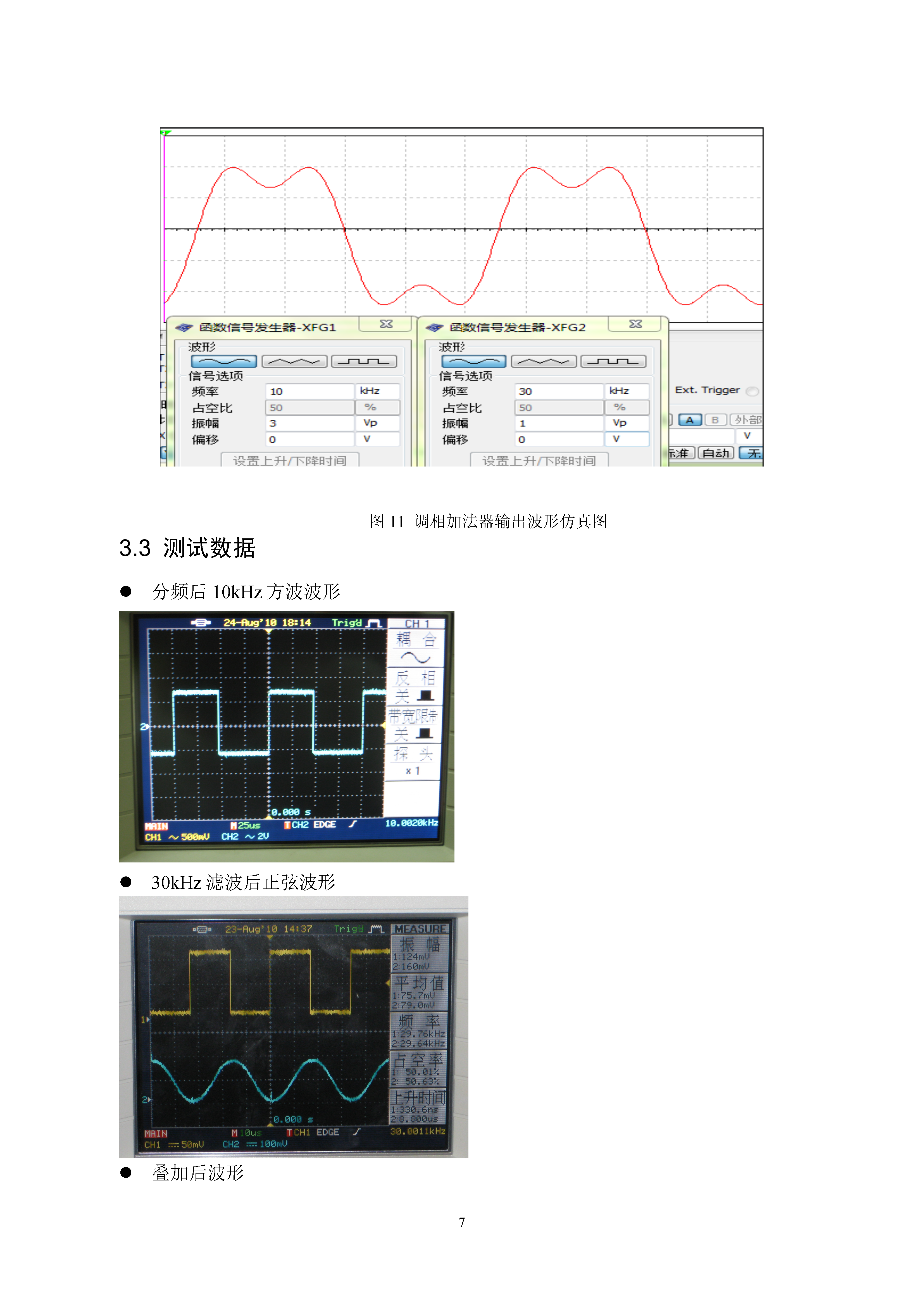

8信号波形合成实验电路摘要:本设计由六个模块构成:方波信号产生模块,正弦信号产生模块(滤波模块),幅度调节模块,波形叠加模块,以及正弦波幅值测量。利用晶振和CD4060产生方波,以提高信号的频率稳定度,采用74LS161构成分频电路得到所需要的信号频率。使用FilterSolution软件设置RC参数实现具有较好截止特性的低通滤波器对方波进行滤波,以得到所需正弦信号,幅度、相位调节后用运算法放大器构成加法电路实现正弦信号的合成,采用减法电路实现三角波。采用MSP430单片机控制TLV1544实现了电压测量

信号波形处理设计论文.doc

信号波形合成实验电路摘要:本设计由六个模块构成:方波信号产生模块,正弦信号产生模块(滤波模块),幅度调节模块,波形叠加模块,以及正弦波幅值测量。利用晶振和CD4060产生方波,以提高信号的频率稳定度,采用74LS161构成分频电路得到所需要的信号频率。使用FilterSolution软件设置RC参数实现具有较好截止特性的低通滤波器对方波进行滤波,以得到所需正弦信号,幅度、相位调节后用运算法放大器构成加法电路实现正弦信号的合成,采用减法电路实现三角波。采用MSP430单片机控制TLV1544

信号波形处理设计论文.doc

信号波形合成实验电路摘要:本设计由六个模块构成:方波信号产生模块,正弦信号产生模块(滤波模块),幅度调节模块,波形叠加模块,以及正弦波幅值测量。利用晶振和CD4060产生方波,以提高信号的频率稳定度,采用74LS161构成分频电路得到所需要的信号频率。使用FilterSolution软件设置RC参数实现具有较好截止特性的低通滤波器对方波进行滤波,以得到所需正弦信号,幅度、相位调节后用运算法放大器构成加法电路实现正弦信号的合成,采用减法电路实现三角波。采用MSP430单片机控制TLV154

信号波形处理设计.doc

信号波形合成实验电路摘要:本设计由六个模块构成:方波信号产生模块,正弦信号产生模块(滤波模块),幅度调节模块,波形叠加模块,以及正弦波幅值测量。利用晶振和CD4060产生方波,以提高信号的频率稳定度,采用74LS161构成分频电路得到所需要的信号频率。使用FilterSolution软件设置RC参数实现具有较好截止特性的低通滤波器对方波进行滤波,以得到所需正弦信号,幅度、相位调节后用运算法放大器构成加法电路实现正弦信号的合成,采用减法电路实现三角波。采用MSP430单片机控制TLV154

信号波形处理设计大学毕设论文.doc

信号波形合成实验电路摘要:本设计由六个模块构成:方波信号产生模块,正弦信号产生模块(滤波模块),幅度调节模块,波形叠加模块,以及正弦波幅值测量。利用晶振和CD4060产生方波,以提高信号的频率稳定度,采用74LS161构成分频电路得到所需要的信号频率。使用FilterSolution软件设置RC参数实现具有较好截止特性的低通滤波器对方波进行滤波,以得到所需正弦信号,幅度、相位调节后用运算法放大器构成加法电路实现正弦信号的合成,采用减法电路实现三角波。采用MSP430单片机控制TLV1544