锁相环的频率鉴定器及锁相环.pdf

涵蓄****09

在线预览结束,喜欢就下载吧,查找使用更方便

相关资料

锁相环的频率鉴定器及锁相环.pdf

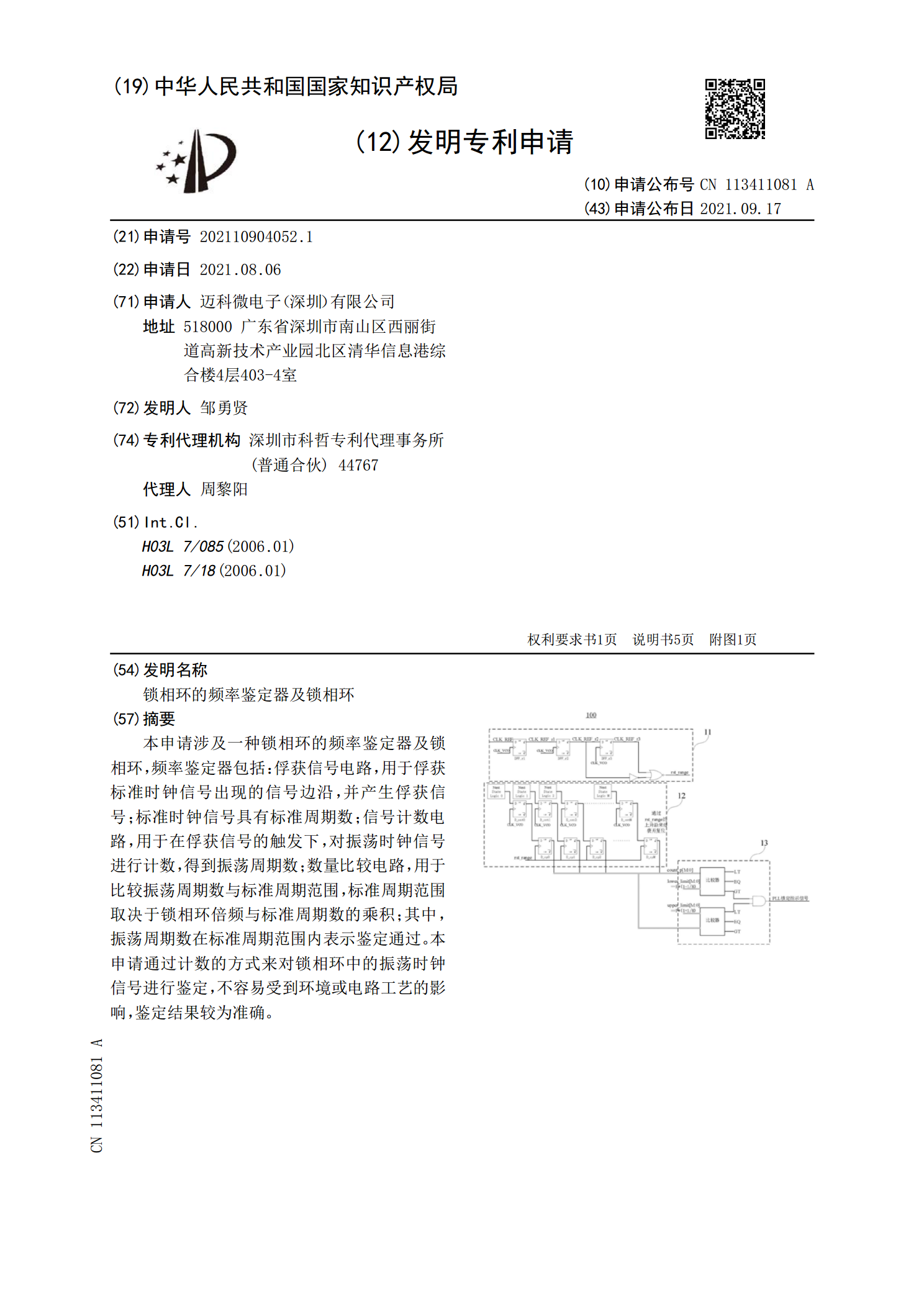

本申请涉及一种锁相环的频率鉴定器及锁相环,频率鉴定器包括:俘获信号电路,用于俘获标准时钟信号出现的信号边沿,并产生俘获信号;标准时钟信号具有标准周期数;信号计数电路,用于在俘获信号的触发下,对振荡时钟信号进行计数,得到振荡周期数;数量比较电路,用于比较振荡周期数与标准周期范围,标准周期范围取决于锁相环倍频与标准周期数的乘积;其中,振荡周期数在标准周期范围内表示鉴定通过。本申请通过计数的方式来对锁相环中的振荡时钟信号进行鉴定,不容易受到环境或电路工艺的影响,鉴定结果较为准确。

锁相环的频率校准方法及锁相环电路.pdf

本发明公开了一种锁相环的频率校准方法及锁相环电路,该方法包括:在锁相环上电过程中获取锁相环中压控振荡器的输出频率;根据目标频率值对压控振荡器的输出频率进行校准,以使得压控振荡器的输出频率与目标频率值的差值小于预设阈值;在锁相环工作过程中获取压控振荡器的输出频率;根据目标频率区间对压控振荡器的输出频率进行校准,以使得压控振荡器的输出频率位于所述目标频率区间内。本发明能够同时保证系统的校准性能和校准时间,也能够实现对系统参数的精准控制,大幅提升了锁相环电路的稳定性和可靠性。

锁相环频率合成技术.ppt

锁相环与频率合成技术目录LC震荡电路晶体振荡电路振荡电路的应用需求举例PLL的特点及应用PLL的框架及结构锁相环工作原理频率锁定过程PLL系统完整框图加入PLL系统后的接收机框图锁相环IC举例(MB1504应用电路)PLL的关键器件及指标PLL电路分析PLL效果演示结束

锁相环路与频率合成.doc

§7-1锁相环路概述第七章锁相环路与频率合成§7-2锁相环路基本工作原理§7-3锁相环路分析§7-5频率合成§7-4锁相环路的应用§7-1锁相环路概述一、发展历史三、锁相环路分析方法二、锁相环路的特点§7-1锁相环路概述一.发展历史第七章锁相环路与频率合成20世纪30年代——接收设备锁相同步控制20世纪40年代——电视接收同步扫描20世纪50年代——锁相接收机实现卫星通信技术20世纪60年代——各部件制作费用昂贵所以它的发展受限制20世纪70年代——成为现代通信、电子技术领域中不可缺少的重要控制技术●●●

锁相环频率综合器关键技术研究.docx

锁相环频率综合器关键技术研究摘要随着现代通信技术的不断发展,锁相环频率综合器作为一种重要的频率合成技术,已经在现代通信系统中得到了广泛的应用。锁相环频率综合器的关键技术主要包括相位检测器的设计、环路滤波器的设计、参考时钟源的选择和输出驱动器的设计等方面。本文将对锁相环频率综合器的关键技术进行探讨,并结合实例进行讲解,以期对读者有所帮助。关键词:锁相环频率综合器;相位检测器;环路滤波器;参考时钟源;输出驱动器前言近年来,随着通信技术的不断发展,锁相环频率综合器成为了一种日益重要的频率合成技术。锁相环频率综合