在嵌入式系统中降低CPLD的功耗.pdf

是你****优呀

在线预览结束,喜欢就下载吧,查找使用更方便

相关资料

在嵌入式系统中降低CPLD的功耗.pdf

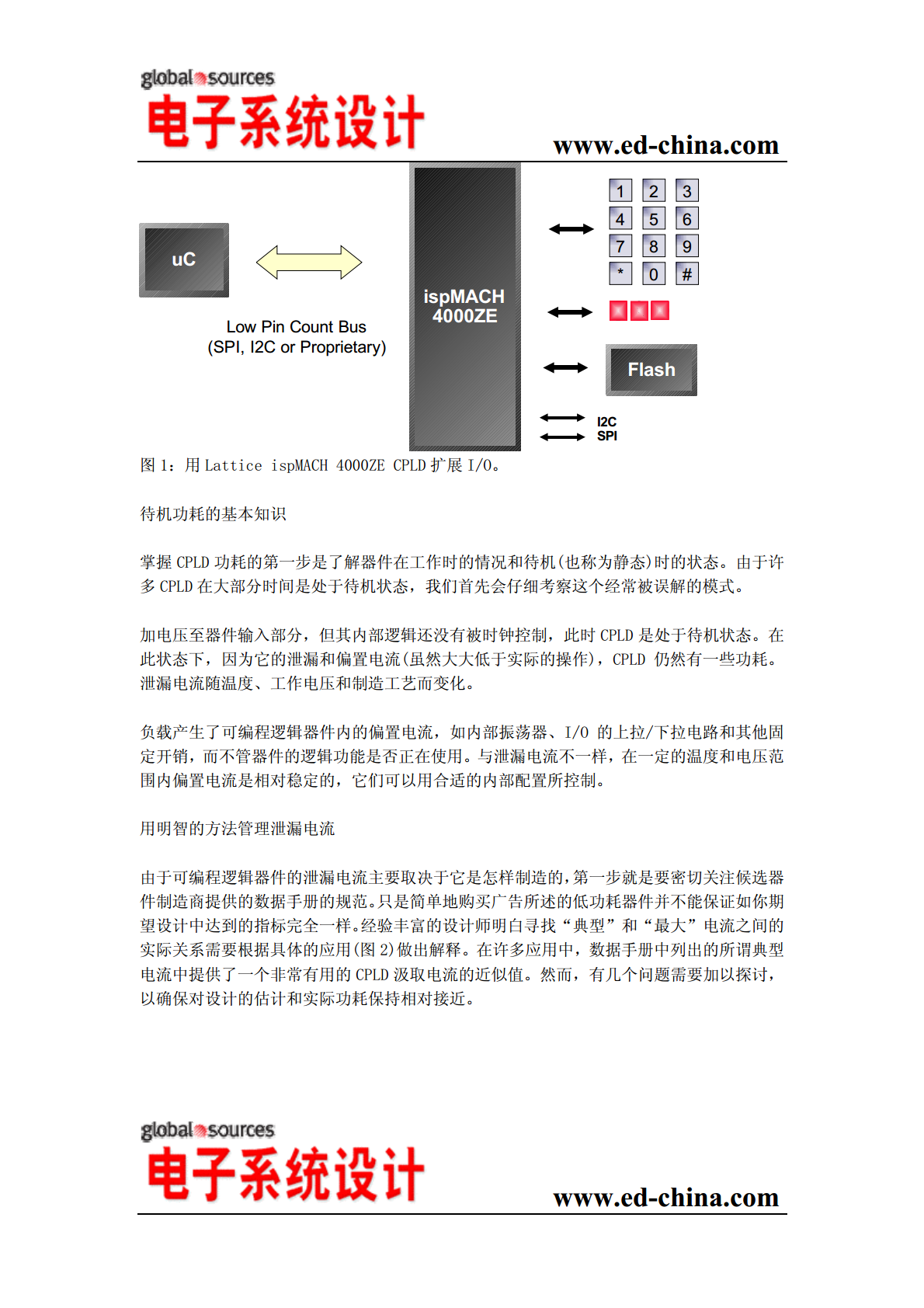

www.ed-china.com在嵌入式设计中降低CPLD的功耗

降低嵌入式医疗电子应用中的功耗.docx

降低嵌入式医疗电子应用中的功耗随着嵌入式技术在医疗电子应用中的应用越来越广泛,功耗控制成为了一个很重要的课题。医疗设备需要长时间连续运行,因此功耗控制不仅可以延长设备的使用寿命,还可以降低医疗运营的成本。本文将介绍一些降低嵌入式医疗电子应用中的功耗的方法。一、优化软件算法1.1减少执行次数优化软件算法是降低功耗的一种有效方法。在程序设计时,可以采用一些技术来减少程序的执行次数,从而降低功耗。比如,采用快速排序算法代替冒泡排序算法可以大大减少处理的时间,从而减少功耗。图1快速排序算法与冒泡排序算法的时间复杂

降低近场通信系统中功耗的技术.pdf

各种实施例一般地涉及一种在蜂窝通信频率范围内通信的技术,响应于用于蜂窝通信的蜂窝通信频率范围内的通信而检测谐振信号,谐振信号指示非接触式卡的存在。实施例还包括基于谐振信号的检测启用近场通信设备以向非接触式卡发送通信,近场通信设备在近场通信频率范围内与非接触式卡通信。

降低近场通信系统中的连接建立的功耗.pdf

本发明公开了用于降低与在近场通信系统中建立连接相关联的功耗的方法和装置。根据一些实施例,当请求主动模式NFC连接时,发起设备可以在向目标设备发送轮询命令之后通过扩展的时间段来选择性地扩展其NFC载波信号的传输。扩展的时间段使目标设备具有额外的时间来稳定其时钟信号,并且将其自己的NFC载波信号发送回发起设备。因此,发起设备可以等待直到在接收到请求主动模式NFC会话的轮询命令之后启用其NFC时钟发生器,以这种方式,当发起设备请求被动模式NFC连接时,目标设备可以不启用其NFC时钟发生器,从而降低功耗。

无线传输中降低系统功耗的方法研究.docx

无线传输中降低系统功耗的方法研究无线通信作为一种无线电技术,已经被广泛应用于生活和工作中。然而,传统的无线通信技术在能耗和功耗方面存在着一些问题。为了解决这些问题,研究人员提出了许多方法来降低系统功耗,保证系统的可持续性。本文将探讨这些方法的有效性,以及它们如何在无线传输中降低系统功耗。第一种方法是通过优化通信协议来降低功耗。通信协议是无线传输中最重要的部分之一,因为它规定了通信的方式和流程。通过优化通信协议,我们可以尽可能地减少干扰,从而达到降低功耗的目的。例如,在低功耗蓝牙(BLE)协议中,BLE将设