IIC总线通讯接口器件的CPLD实现.pdf

猫巷****盟主

在线预览结束,喜欢就下载吧,查找使用更方便

相关资料

IIC总线通讯接口器件的CPLD实现.pdf

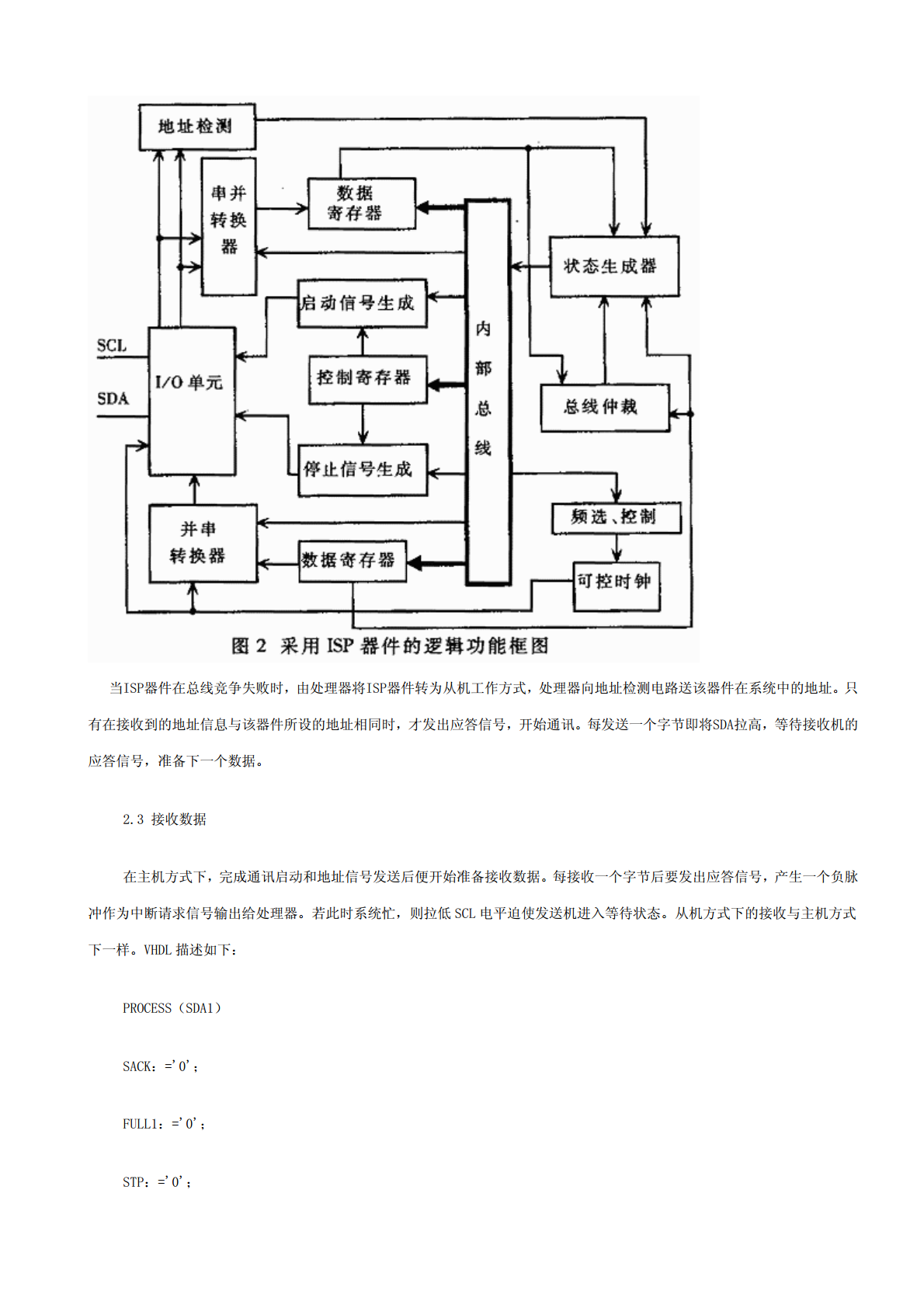

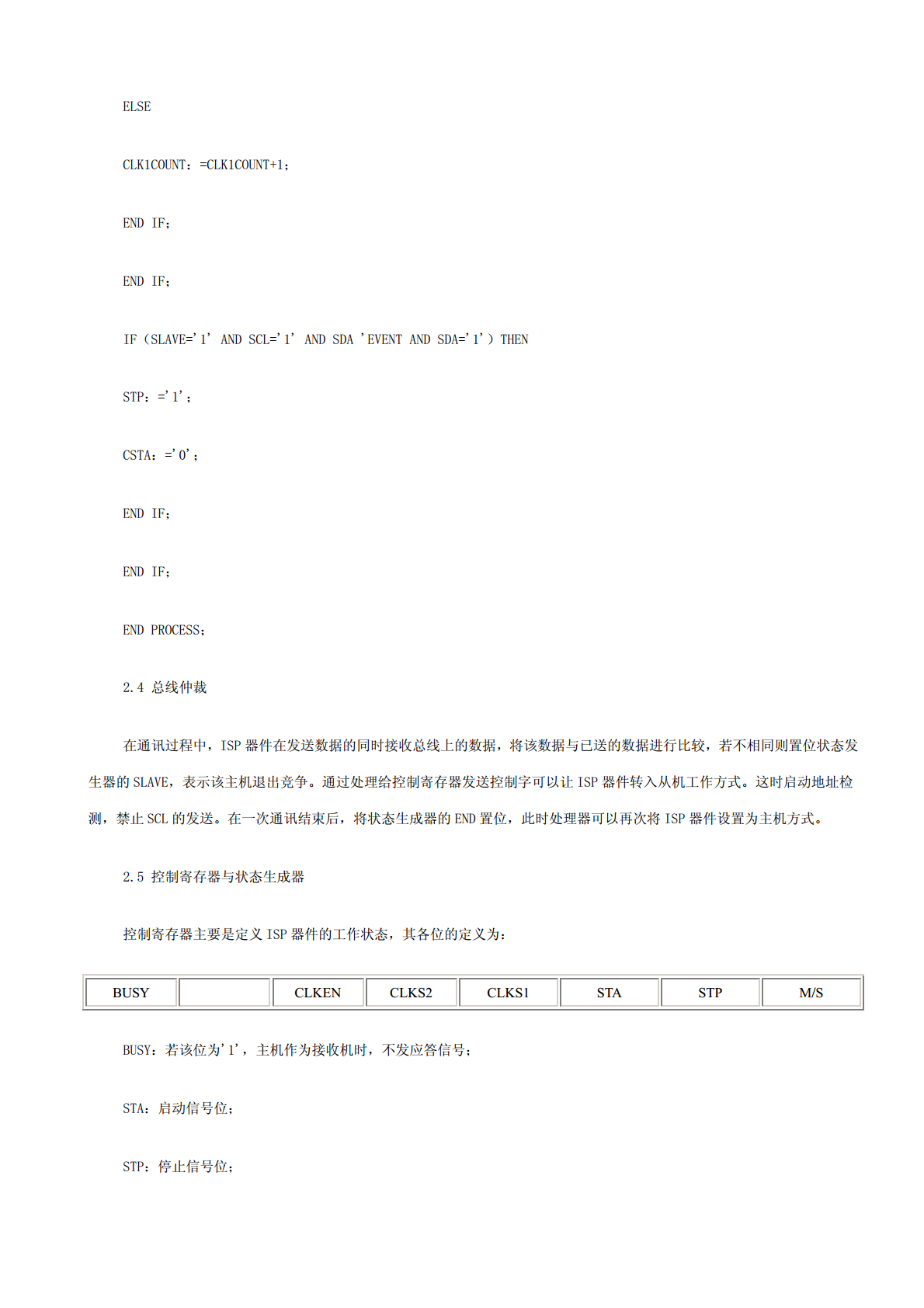

IIC总线通讯接口器件的CPLD实现文章作者:张冬冬

IIC总线通讯接口器件的CPLD实现.pdf

IIC总线通讯接口器件的CPLD实现文章作者:张冬冬

ARM 2440 IIC总线接口 中文资料.pdf

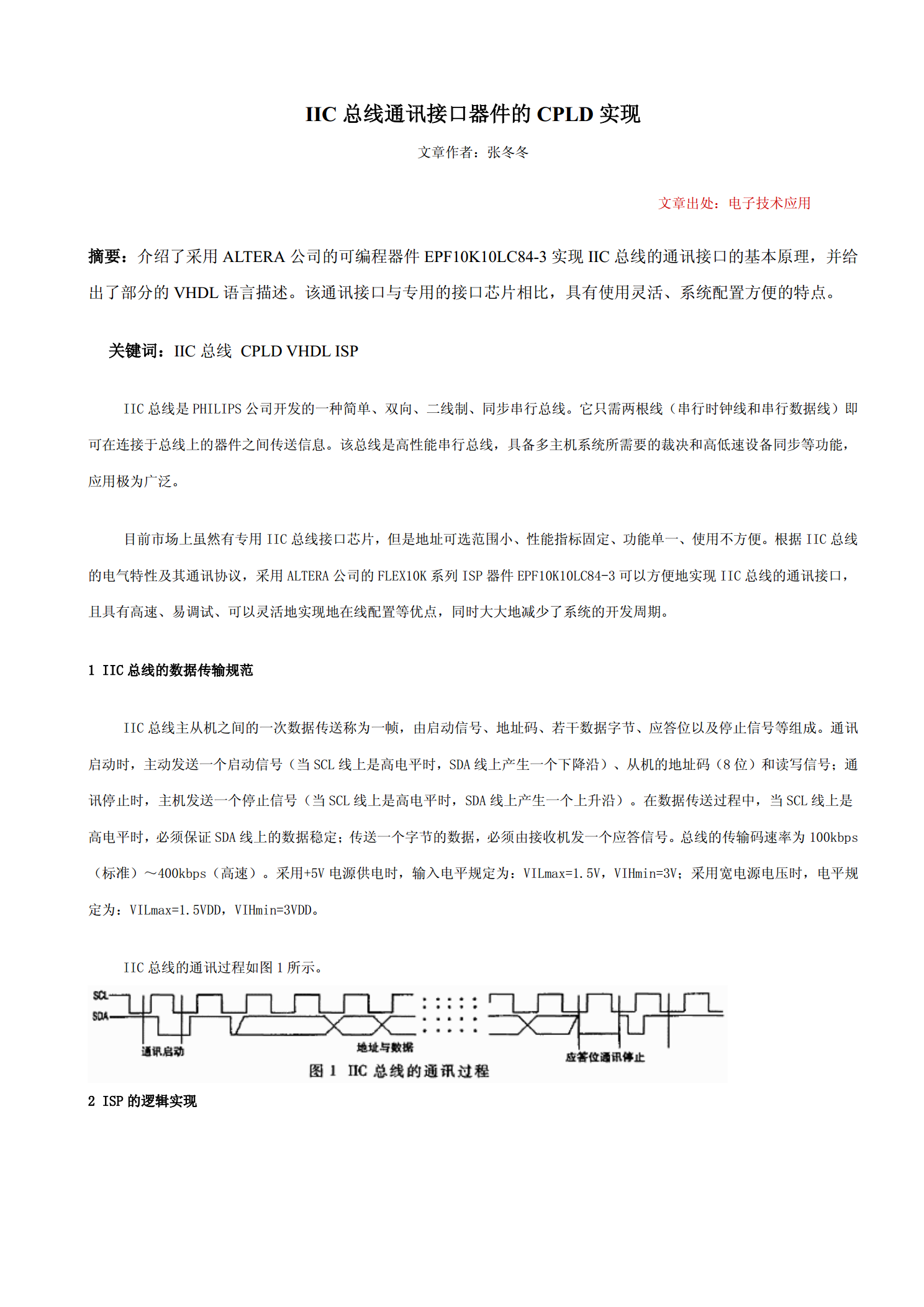

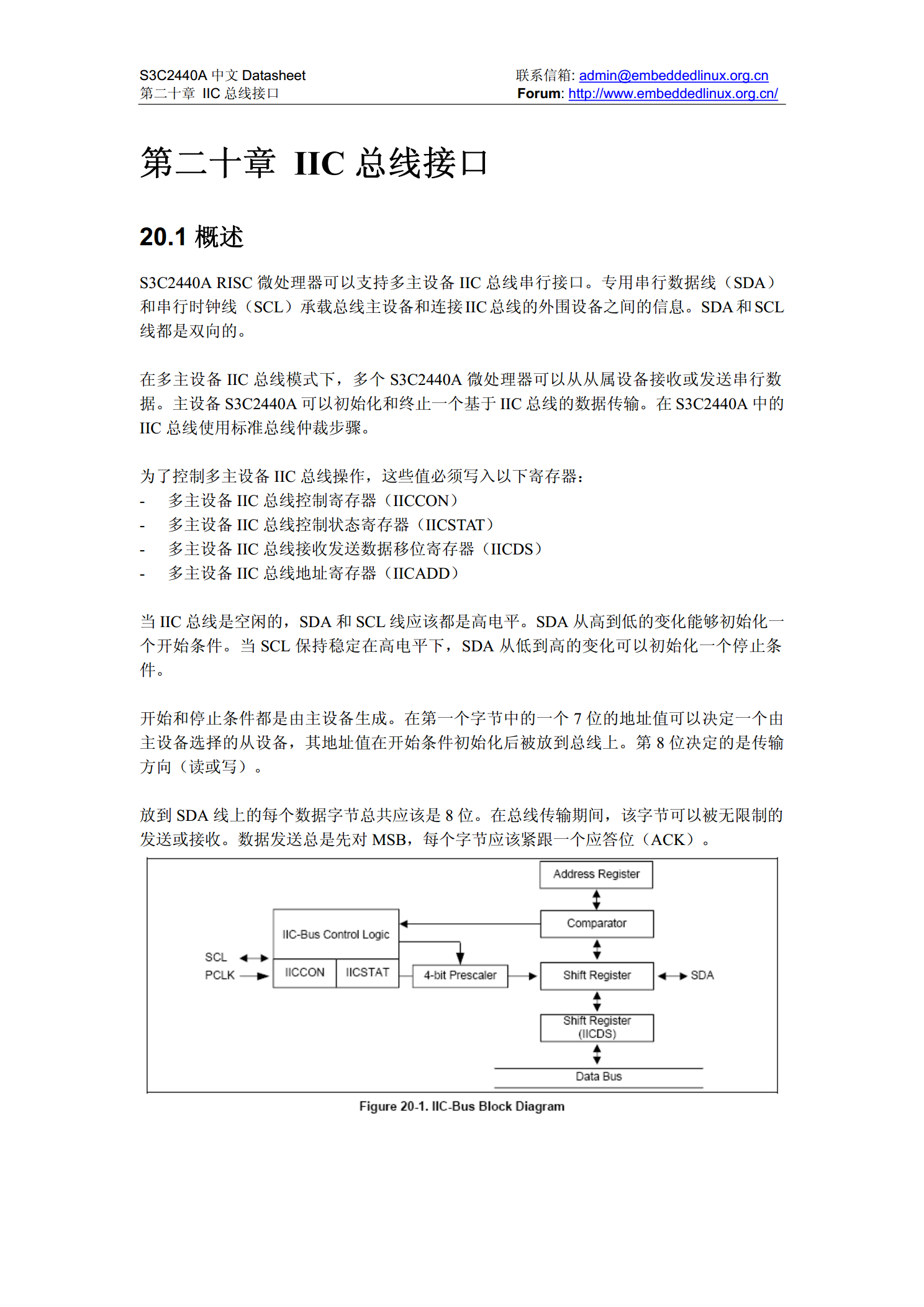

S3C2440A中文Datasheet联系信箱:admin@embeddedlinux.org.cn第二十章IIC总线接口Forum:http://www.embeddedlinux.org.cn/第二十章IIC总线接口20.1概述S3C2440ARISC微处理器可以支持多主设备IIC总线串行接口。专用串行

用CPLD实现单片机与ISA总线接口的并行通信.docx

用CPLD实现单片机与ISA总线接口的并行通信摘要:介绍了用ALTERA公司MAX7000系列CPLD芯片实现单片机与PC104ISA总线接口之间的关行通信。给出了系统设计方法及程序源代码。关键词:CPLDISA总线并行通信CPLD(ComplexProgrammableLogicDevice)是一种复杂的用户可编程逻辑器件,由于采用连续连接结构,易于预测延时,从而使电路仿真更加准确。CPLD是标准的大规模集成电路产品,可用于各种数字逻辑系统的设计。近年来,由于采用先进的集成工艺和大指量生产,CPLD器件

用可编程器件CPLD实现收音机数据与CAN总线网络的连接接口.doc

用可编程器件CPLD实现收音机数据与CAN总线网络的连接接口可编程逻辑器件PLD(ProgrammablelogicDevice)就是由用户进行编程实现所需逻辑功能的数字专用集成电路ASIC。可编程逻辑器件在现代电子工程设计中得到了广泛应用。它是在PAL,GAL等逻辑器件的基础上发展起来的,具有高密度,高速度,低功耗体系结构和逻辑单元,灵活以及运用范围宽等特点,同时还具有设计周期短,制造成本低,开发工具先进,标准产品无需测试,质量稳定及可实时布线检验等优点。现场总线技术广泛应用于工业和军用测控局域网中,特