“聚芯”SoC的IBIS仿真模型的研究及应用.pdf

Ro****44

亲,该文档总共70页,到这已经超出免费预览范围,如果喜欢就直接下载吧~

相关资料

“聚芯”SoC的IBIS仿真模型的研究及应用的中期报告.docx

“聚芯”SoC的IBIS仿真模型的研究及应用的中期报告本报告对“聚芯”SoC的IBIS仿真模型的研究及应用进行了中期汇报。我们团队致力于研发高质量的IBIS仿真模型,以帮助我们的客户更好地设计和验证各种电子产品。在过去的几个月中,我们主要完成了以下任务:1.中期评估报告我们在项目的中期进行了评估报告,对我们已经完成的工作进行了总结,并提出了下一步改进方案。我们发现我们已经取得了很好的进展,但是还需要继续努力提高我们的模型质量和完整性。2.设计和验证测试模式我们已经设计和验证了各种测试模式,包括各种方波、正

“聚芯”SoC的IBIS仿真模型的研究及应用.pdf

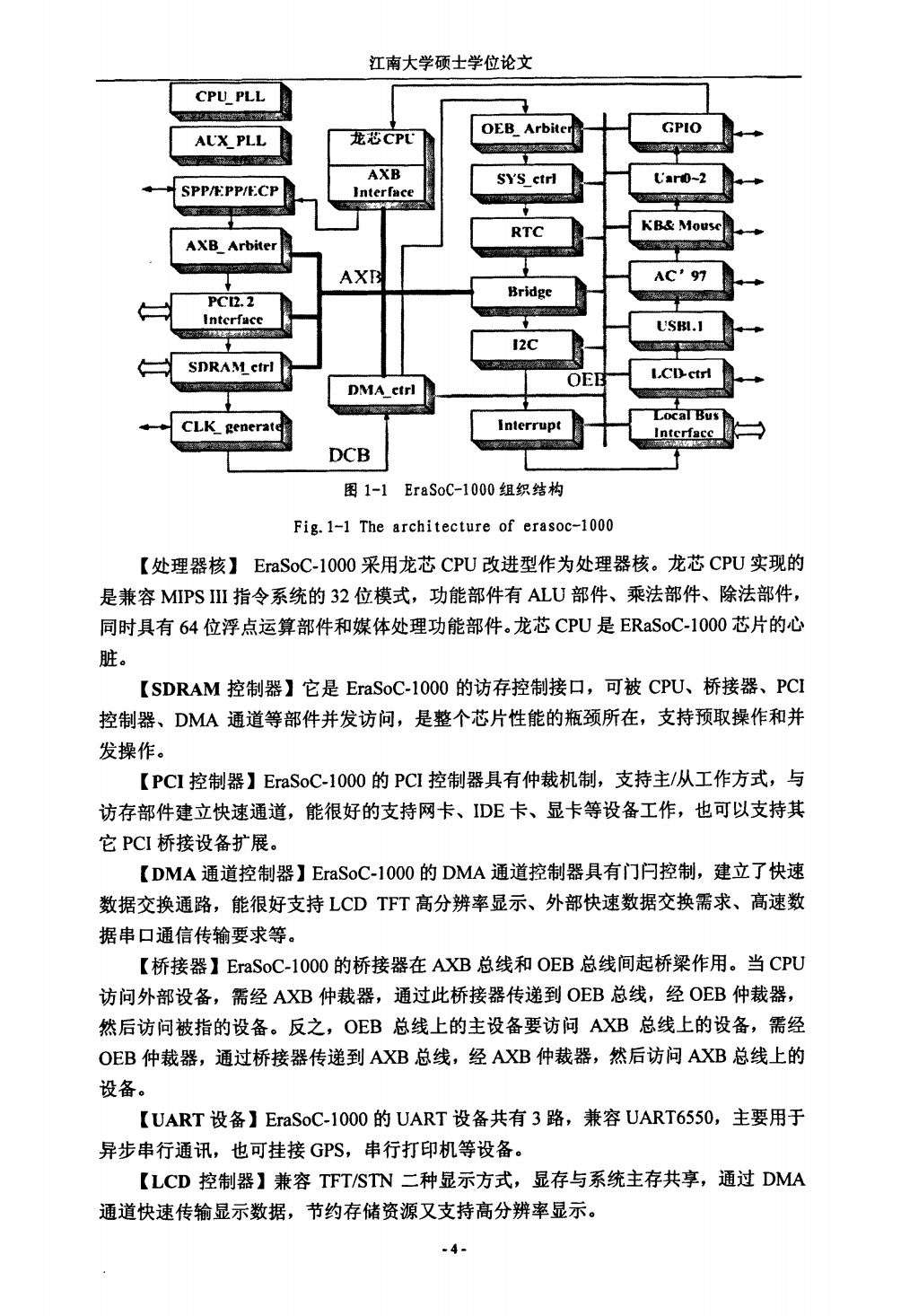

江南大学硕士学位论文“聚芯”SoC的IBIS仿真模型的研究及应用姓名:归敏丹申请学位级别:硕士专业:计算机应用指导教师:吴锡生;张志敏20080701摘要鲥够窒笠踩找嫱怀觯伤近年来随着集成电路技术和印制电路板加工制造工艺的不断提高纷纷出现的高速集成电路芯片及其构成的电子系统性能速度越来越快、面积越来越小、规模和密度越来越大。这在为用户带来方

“聚芯”SoC的IBIS仿真模型的研究及应用.pdf

江南大学硕士学位论文“聚芯”SoC的IBIS仿真模型的研究及应用姓名:归敏丹申请学位级别:硕士专业:计算机应用指导教师:吴锡生;张志敏20080701摘要鲥够窒笠踩找嫱怀觯伤近年来随着集成电路技术和印制电路板加工制造工艺的不断提高纷纷出现的高速集成电路芯片及其构成的电子系统性能速度越来越快、面积越来越小、规模和密度越来越大。这在为用户带来方

IBIS模型的仿真研究与应用分析.pdf

第!"卷#第$期#######武汉理工大学学报·信息与管理工程版#########%&’(!")&($!**$年+*月#####-./)01-23.4(5)2-/6045-)760)08969)49)85)99/5)8)######-:;(!**$文章编号:+**"<+==>(!**$)*$<***?<*=!"!#模型的仿真研究与应用

IBIS仿真模型的应用.docx

IBIS仿真模型的应用IBIS仿真模型是一种电线特性模型,是半导体行业使用最广泛的、成熟的仿真工具。它能够精确地描述IC芯片的特性,包括时钟、信号延迟等。在电路设计中,IBIS仿真模型的应用非常广泛。本文将介绍IBIS仿真模型的应用范围、功能和优势。1.IBIS仿真模型的应用范围IBIS仿真模型通常被应用于模拟电路、半导体芯片设计和PCB布线设计等领域。在这些领域中,IBIS仿真模型可以模拟电路中的信号传输、滤波器设计、放大器设计、时钟信号传输、布线设计等方面的问题。IBIS仿真模型还可以模拟内部、外部信