一种存储器芯片位线失效分析方法.pdf

雨巷****怡轩

亲,该文档总共13页,到这已经超出免费预览范围,如果喜欢就直接下载吧~

相关资料

一种存储器芯片位线失效分析方法.pdf

本发明提供一种存储器芯片位线失效分析方法,包括以下步骤:通过机械研磨去除待分析芯片的互连金属层和位线层的大部分;通过机械研磨去除待分析芯片的衬底的大部分;通过湿法刻蚀完全去除待分析芯片的残存的衬底;通过干法刻蚀去除待分析芯片位线接触窗底部的介质层的大部分,保留一薄层的介质层;对待分析芯片的位线接触窗的顶部进行检测,确定位线失效的具体位置。本发明方法可使待分析芯片充分减薄,可直接通过电子显微镜进行观测确定其位线短路失效的具体位置,大大提高了工作效率,节省了时间成本。

一种芯片失效分析方法.pdf

本发明提供一种芯片失效分析方法,用于检测芯片栅极的缺陷特征,其步骤包括:通过机械研磨去除进行失效分析的芯片的衬底和有源区的大部分;通过湿法刻蚀去除芯片残存的衬底和有源区;通过干法刻蚀去除芯片的栅氧层的大部分,保留的部分栅氧层用于保护栅极第一多晶硅层;检测所述第一多晶硅层是否存在缺陷特征。本发明方法可将芯片准确剥离至栅极第一层多晶硅的底部,测得其底部的精确尺寸参数,并可大大提高工作效率,节省时间成本。

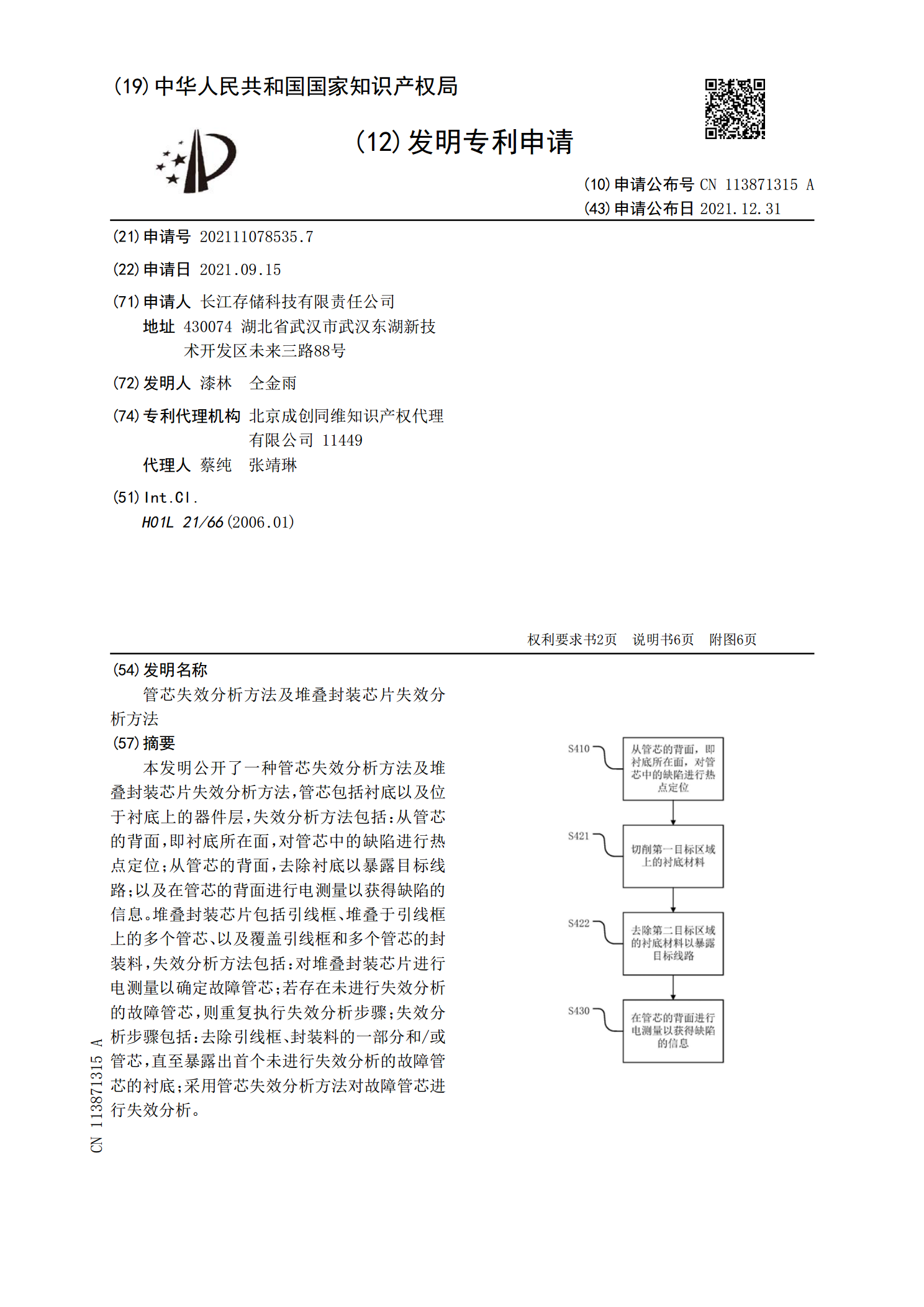

管芯失效分析方法及堆叠封装芯片失效分析方法.pdf

本发明公开了一种管芯失效分析方法及堆叠封装芯片失效分析方法,管芯包括衬底以及位于衬底上的器件层,失效分析方法包括:从管芯的背面,即衬底所在面,对管芯中的缺陷进行热点定位;从管芯的背面,去除衬底以暴露目标线路;以及在管芯的背面进行电测量以获得缺陷的信息。堆叠封装芯片包括引线框、堆叠于引线框上的多个管芯、以及覆盖引线框和多个管芯的封装料,失效分析方法包括:对堆叠封装芯片进行电测量以确定故障管芯;若存在未进行失效分析的故障管芯,则重复执行失效分析步骤;失效分析步骤包括:去除引线框、封装料的一部分和/或管芯,直至

芯片失效分析_.pdf

电子元器件失效分析技术信息产业部电子五所信息产业部电子五所分析中心http://www.rac.ceprei.com课程安排•1失效分析方法和技术•2失效机理与失效分析方法•3失效分析案例信息产业部电子五所分析中心http://www.rac.ceprei.com第1章失效分析方法和技术•1失效分析基本概念•2失效分析的程序•3失效分析方法和技术测试、模拟、无损分析、样品制备、失效定位、缺陷的形貌观察信息产业部电子五所分析中心http://www.rac.ceprei.com失效分析的概念失效分析的定义失

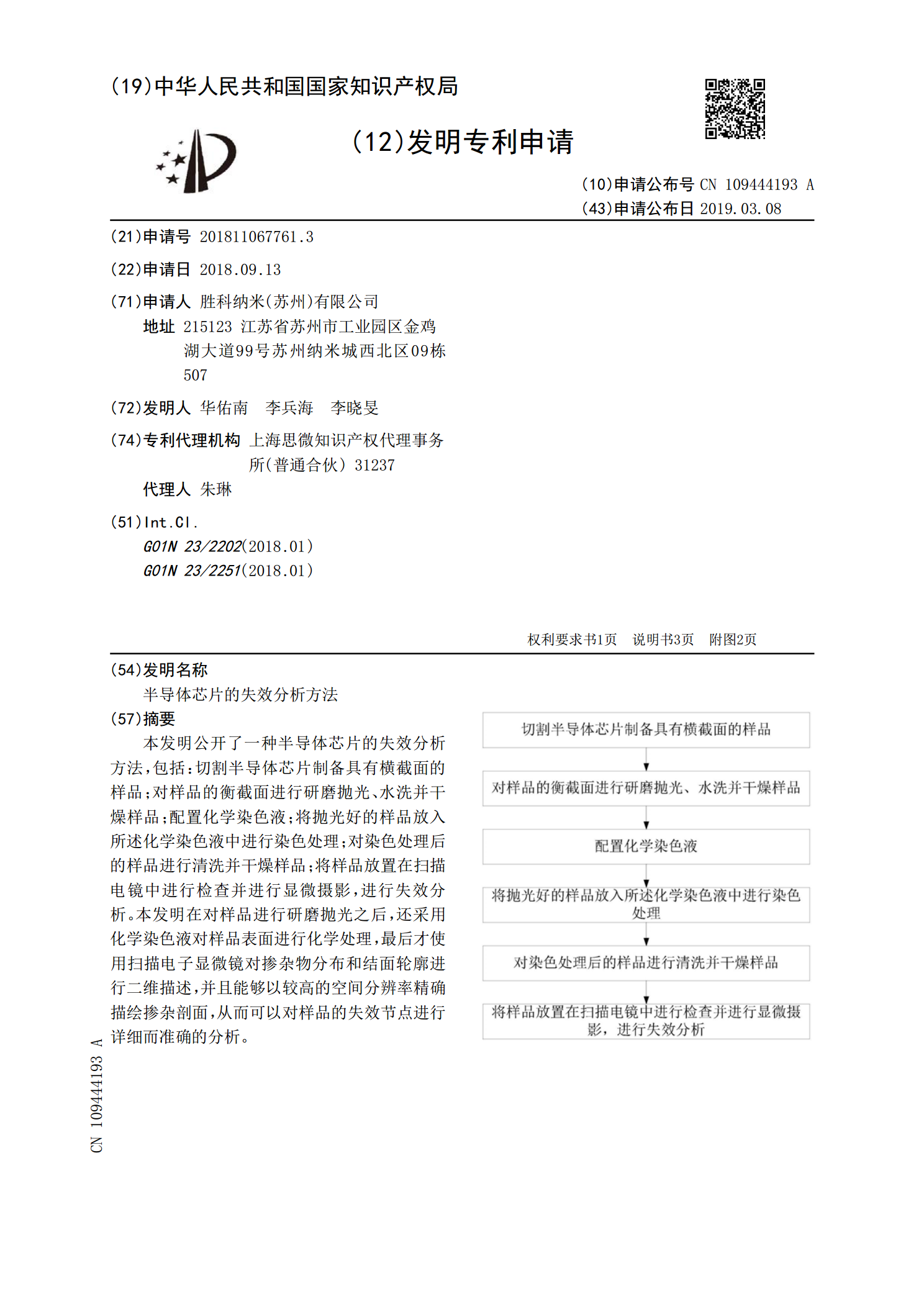

半导体芯片的失效分析方法.pdf

本发明公开了一种半导体芯片的失效分析方法,包括:切割半导体芯片制备具有横截面的样品;对样品的衡截面进行研磨抛光、水洗并干燥样品;配置化学染色液;将抛光好的样品放入所述化学染色液中进行染色处理;对染色处理后的样品进行清洗并干燥样品;将样品放置在扫描电镜中进行检查并进行显微摄影,进行失效分析。本发明在对样品进行研磨抛光之后,还采用化学染色液对样品表面进行化学处理,最后才使用扫描电子显微镜对掺杂物分布和结面轮廓进行二维描述,并且能够以较高的空间分辨率精确描绘掺杂剖面,从而可以对样品的失效节点进行详细而准确的分析