一种层叠栅极制作方法.pdf

小新****ou

亲,该文档总共22页,到这已经超出免费预览范围,如果喜欢就直接下载吧~

相关资料

一种层叠栅极制作方法.pdf

本发明提供了一种层叠栅极制作方法,提供具有N阱、P阱和STI的硅衬底的晶片,在所述晶片器件面依次制作层间栅氧化层和高介电系数栅极电介质层,该方法包括,先在沉积的第一高介电系数栅介质覆盖层表面形成第一二氧化硅层,在P阱上方依次刻蚀形成第一保护层和n型高介电系数栅介质覆盖层后第一灰化去除第一保护层上残留的光刻胶;接着在在N阱上方形成第二保护层和p型高介电系数栅介质覆盖层后第二灰化去除光刻胶,然后湿法刻蚀去除第一、第二保护层;最后沉积金属层刻蚀形成层叠栅极。本发明在灰化去除光刻胶的过程中,由第一、第二保护层作为

一种栅极制作方法.pdf

本发明提供一种栅极制作方法,该方法包括:提供半导体衬底,于半导体衬底上依次形成栅介质层、多晶硅层及氧化硅掩膜层;刻蚀多晶硅层和栅介质层以形成被沟槽隔离的假栅结构,沟槽显露半导体衬底;于沟槽中形成预设厚度的层间介质层,层间介质层的顶面低于假栅结构的顶面并高于多晶硅层的顶面;采用离子植入工艺对层间介质层进行改性;去除氧化硅掩膜层和多晶硅层;于栅介质层上形成金属栅。本发明于多晶硅层上仅形成一氧化硅硬掩膜层,降低沟槽的深宽比,利于沟槽填充;并且,采用离子植入工艺对层间介质层进行改性,作为假栅结构刻蚀的停止层,以改

一种栅极结构的制作方法.pdf

本发明提供了一种栅极结构的制作方法,首先使形成的多晶硅层的厚度大于目标厚度,然后平坦化处理所述多晶硅层,直至保留的所述多晶硅层的厚度等于所述目标厚度。如此,在保证最终的所述多晶硅层的厚度达到目标厚度的同时,也可避免最终形成的所述多晶硅层的表面存在突起部或表面比较粗糙的情况,故而提高了器件的可靠性。

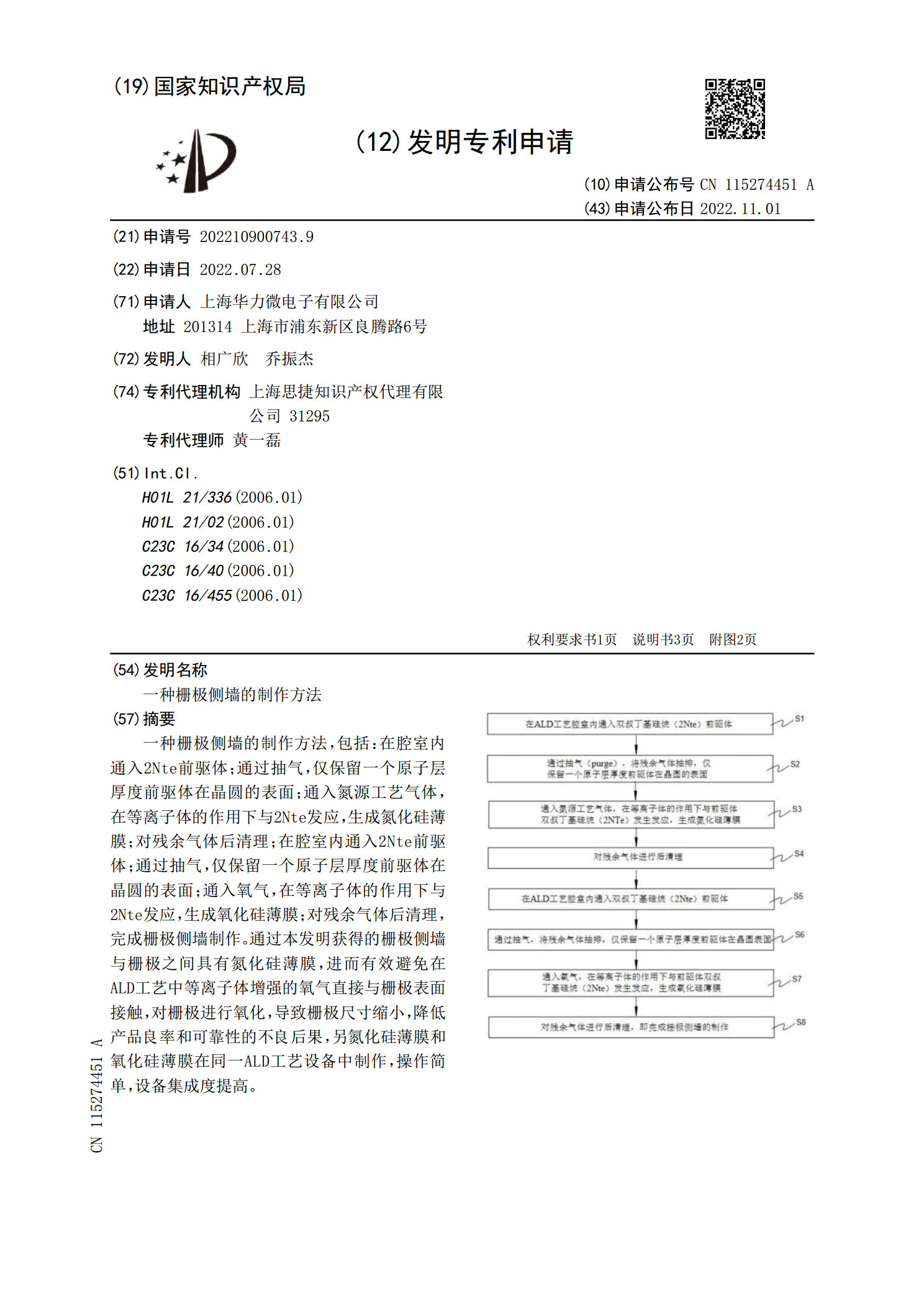

一种栅极侧墙的制作方法.pdf

一种栅极侧墙的制作方法,包括:在腔室内通入2Nte前驱体;通过抽气,仅保留一个原子层厚度前驱体在晶圆的表面;通入氮源工艺气体,在等离子体的作用下与2Nte发应,生成氮化硅薄膜;对残余气体后清理;在腔室内通入2Nte前驱体;通过抽气,仅保留一个原子层厚度前驱体在晶圆的表面;通入氧气,在等离子体的作用下与2Nte发应,生成氧化硅薄膜;对残余气体后清理,完成栅极侧墙制作。通过本发明获得的栅极侧墙与栅极之间具有氮化硅薄膜,进而有效避免在ALD工艺中等离子体增强的氧气直接与栅极表面接触,对栅极进行氧化,导致栅极尺寸

栅极结构的制作方法.pdf

本发明提供一种栅极结构的制作方法。该制作方法包括:提供基底,基底上表面包括沿第一方向伸长且跨越多个有源区的多个第一区域、跨越第一区域的多个第二区域、以及位于相邻两个第一区域之间的第三区域;在基底的上表面形成栅极材料层和硬掩模层;刻蚀去除第二区域上的硬掩模层形成凹槽,在凹槽的内表面形成聚合物层;刻蚀去除第三区域上的硬掩模层,且在该刻蚀过程中,聚合物层作为牺牲层,且第三区域上的栅极材料层的上表面露出时,露出凹槽底面的栅极材料层的上表面;以第一区域上保留的硬掩模层为掩模,刻蚀栅极材料层以形成栅极。如此,栅极的制