半导体器件收缩尺寸的封装结构及方法.pdf

一吃****春晓

亲,该文档总共11页,到这已经超出免费预览范围,如果喜欢就直接下载吧~

相关资料

半导体器件收缩尺寸的封装结构及方法.pdf

本发明提供一种半导体器件收缩尺寸的封装结构及方法,封装方法为:提供一用于制作第一产品的半导体基底,在半导体基底上制作按照第一产品的尺寸收缩的第二产品,第二产品具有位于顶部的第一顶层金属层;淀积一介质层并开孔;在开孔内形成第一焊盘,并在第一焊盘以及介质层的表面上形成第二顶层金属层,采用光刻工艺保留用于连接第二产品的第一焊盘到第一产品的第二焊盘之间区域的第二顶层金属层;覆盖一绝缘层,在对应于绝缘层中制作第二焊盘;对准第二焊盘采用第一产品的晶圆级封装测试工艺,对上述结构进行封装测试,使尺寸收缩后的产品完全采用原

半导体封装模具、半导体器件及半导体器件的封装方法.pdf

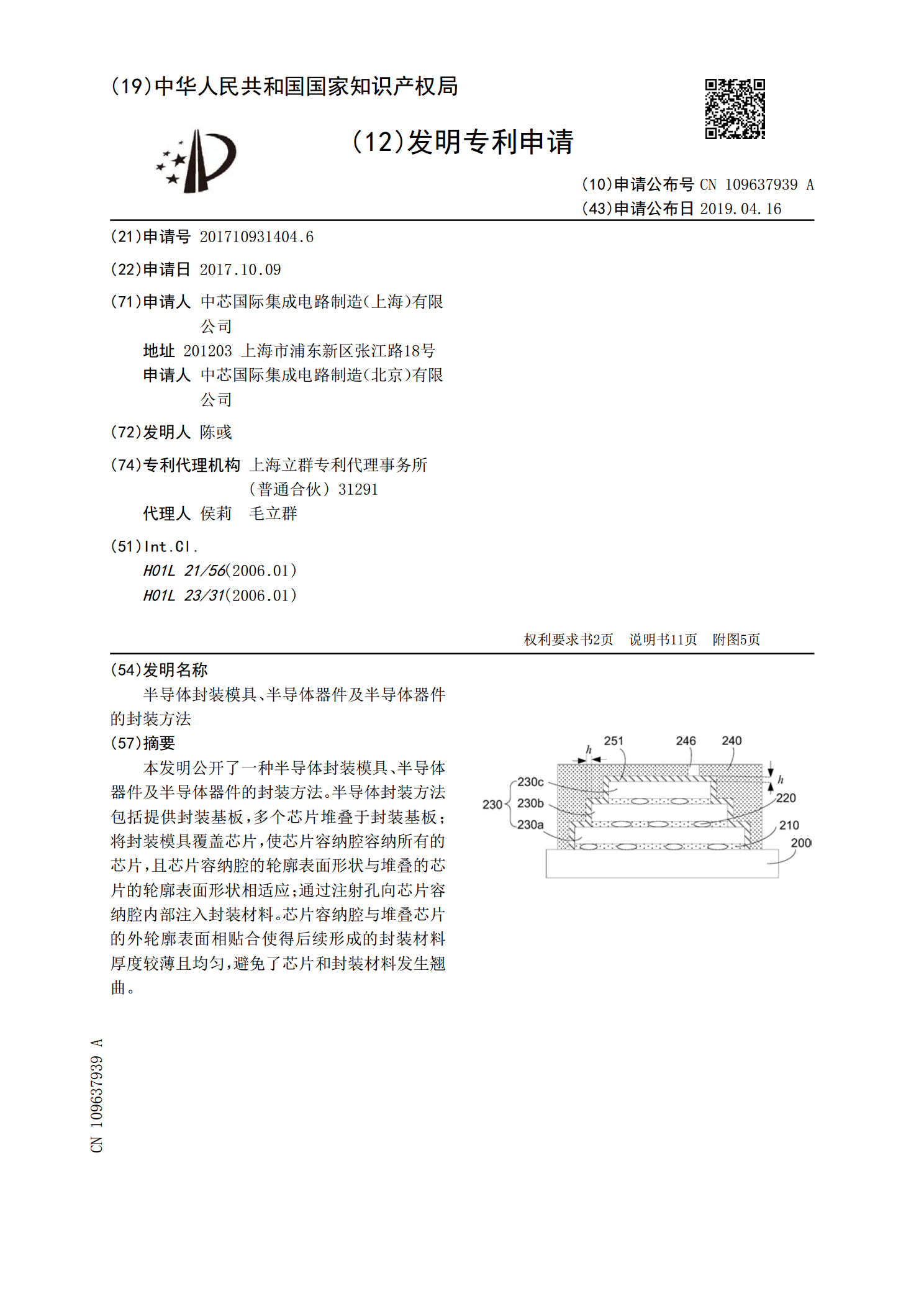

本发明公开了一种半导体封装模具、半导体器件及半导体器件的封装方法。半导体封装方法包括提供封装基板,多个芯片堆叠于封装基板;将封装模具覆盖芯片,使芯片容纳腔容纳所有的芯片,且芯片容纳腔的轮廓表面形状与堆叠的芯片的轮廓表面形状相适应;通过注射孔向芯片容纳腔内部注入封装材料。芯片容纳腔与堆叠芯片的外轮廓表面相贴合使得后续形成的封装材料厚度较薄且均匀,避免了芯片和封装材料发生翘曲。

三维封装结构、半导体器件及封装方法.pdf

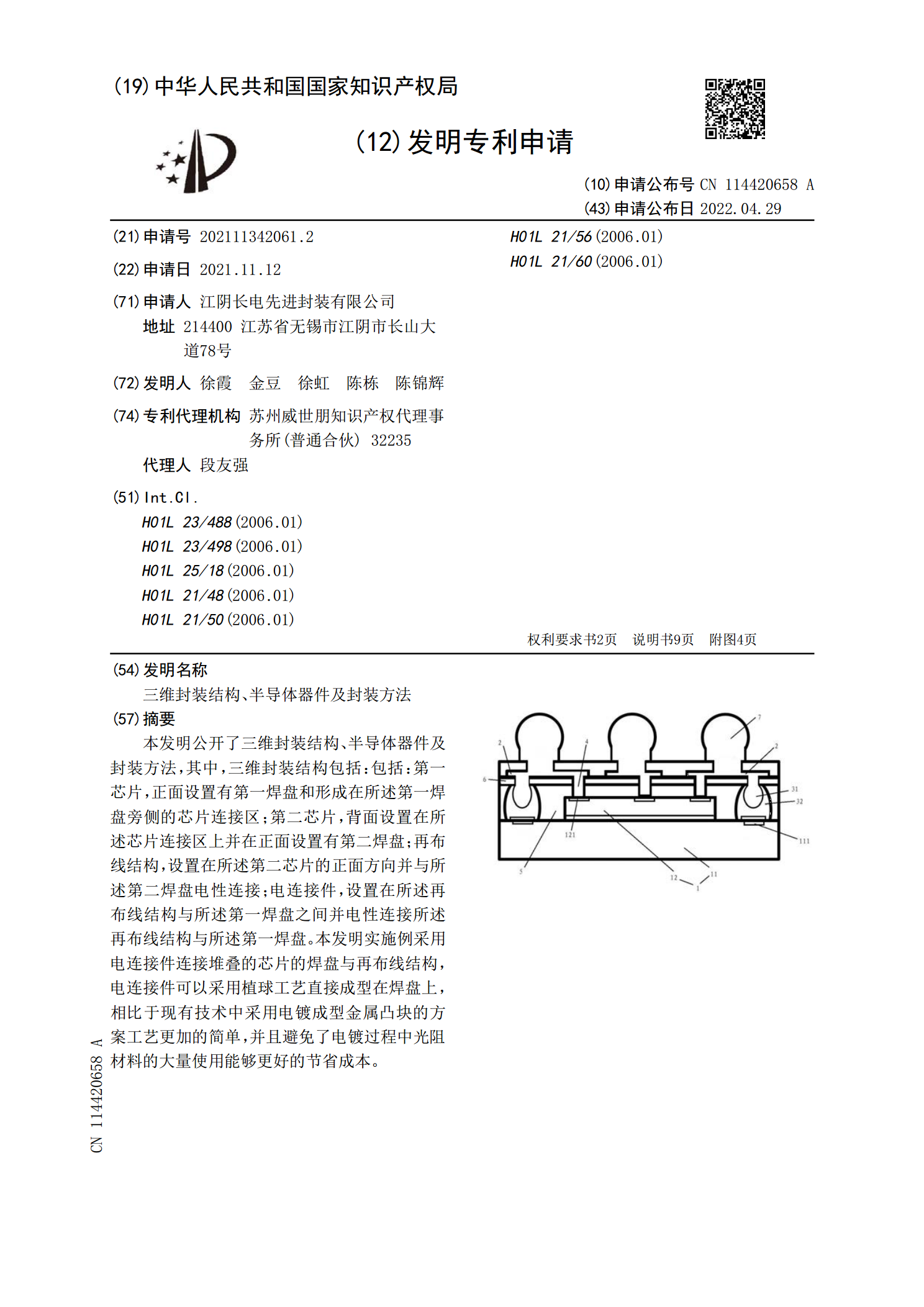

本发明公开了三维封装结构、半导体器件及封装方法,其中,三维封装结构包括:包括:第一芯片,正面设置有第一焊盘和形成在所述第一焊盘旁侧的芯片连接区;第二芯片,背面设置在所述芯片连接区上并在正面设置有第二焊盘;再布线结构,设置在所述第二芯片的正面方向并与所述第二焊盘电性连接;电连接件,设置在所述再布线结构与所述第一焊盘之间并电性连接所述再布线结构与所述第一焊盘。本发明实施例采用电连接件连接堆叠的芯片的焊盘与再布线结构,电连接件可以采用植球工艺直接成型在焊盘上,相比于现有技术中采用电镀成型金属凸块的方案工艺更加的

半导体器件的封装结构及其封装方法及电子设备.pdf

本申请公开了一种半导体器件的封装结构及其封装方法及电子设备,所述封装结构包括:壳体,所述壳体具有容纳腔;所述容纳腔具有开口;所述壳体的侧壁固定有多个第一电极管脚,所述第一电极管脚的一端位于所述容纳腔的内部,另一端穿过所述壳体的侧壁,位于所述容纳腔的外部;基板,所述基板固定在所述容纳腔的底部;多个半导体器件,所述半导体器件固定在所述基板上;所述半导体器件与所述基板连接,通过所述基板与所述第一电极管脚连接;封帽,所述封帽用于密封所述容纳腔的开口。本申请技术方案通过同一壳体同时对多个半导体器件进行封装,相对于多

功率半导体器件封装结构及其制备方法.pdf

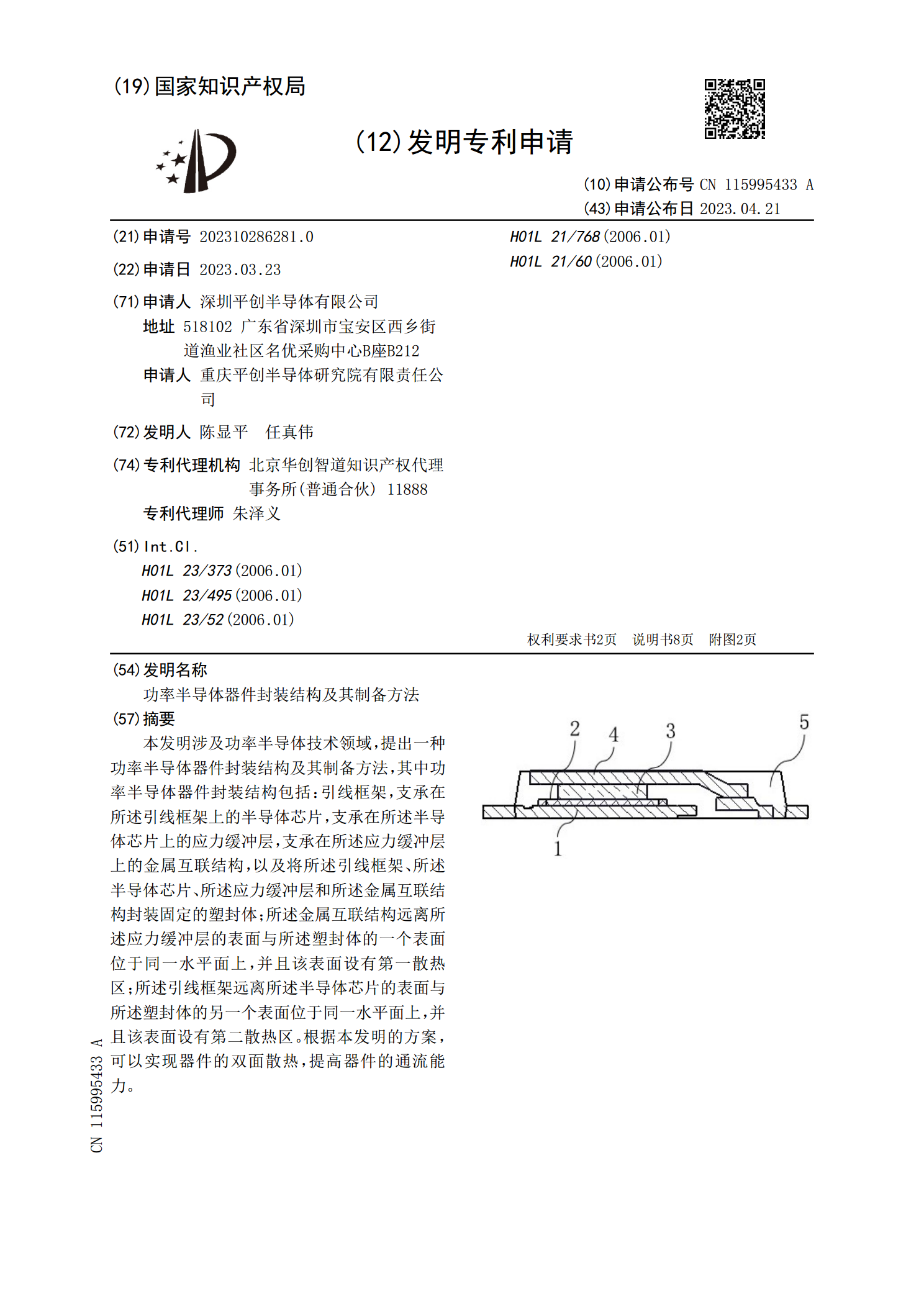

本发明涉及功率半导体技术领域,提出一种功率半导体器件封装结构及其制备方法,其中功率半导体器件封装结构包括:引线框架,支承在所述引线框架上的半导体芯片,支承在所述半导体芯片上的应力缓冲层,支承在所述应力缓冲层上的金属互联结构,以及将所述引线框架、所述半导体芯片、所述应力缓冲层和所述金属互联结构封装固定的塑封体;所述金属互联结构远离所述应力缓冲层的表面与所述塑封体的一个表面位于同一水平面上,并且该表面设有第一散热区;所述引线框架远离所述半导体芯片的表面与所述塑封体的另一个表面位于同一水平面上,并且该表面设有第