高K金属栅器件及其制备方法.pdf

鸿朗****ka

在线预览结束,喜欢就下载吧,查找使用更方便

相关资料

高K金属栅器件及其制备方法.pdf

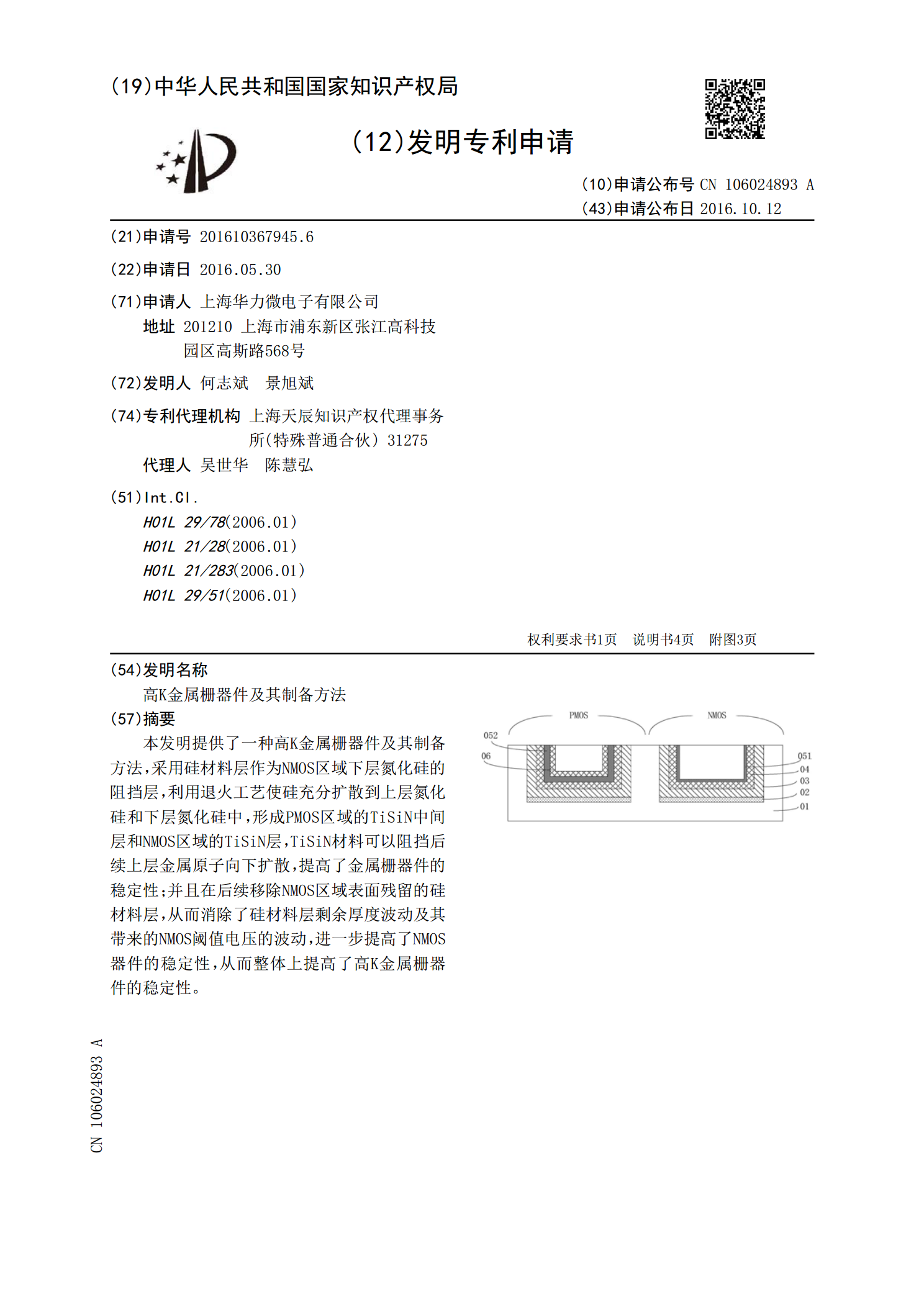

本发明提供了一种高K金属栅器件及其制备方法,采用硅材料层作为NMOS区域下层氮化硅的阻挡层,利用退火工艺使硅充分扩散到上层氮化硅和下层氮化硅中,形成PMOS区域的TiSiN中间层和NMOS区域的TiSiN层,TiSiN材料可以阻挡后续上层金属原子向下扩散,提高了金属栅器件的稳定性;并且在后续移除NMOS区域表面残留的硅材料层,从而消除了硅材料层剩余厚度波动及其带来的NMOS阈值电压的波动,进一步提高了NMOS器件的稳定性,从而整体上提高了高K金属栅器件的稳定性。

铪基高K栅介质薄膜的制备及其器件性能研究.docx

铪基高K栅介质薄膜的制备及其器件性能研究铪基高K栅介质薄膜的制备及其器件性能研究摘要:铪基高K栅介质薄膜在电子器件领域具有广泛的应用前景。本文以研究铪基高K栅介质薄膜的制备方法和器件性能为目标,通过对已有研究成果的综述和分析,总结了目前铪基高K栅介质薄膜的制备方法和器件性能的研究现状,并探讨了未来的研究和应用方向。结果表明,采用溶液旋涂法制备铪基高K栅介质薄膜具有效率高、成本低的优势,并且这种方法可以制备出具有良好电学性能的薄膜,适用于各种电子器件的制备。此外,铪基高K栅介质薄膜在MOSFET器件中展现出

一种具有高K金属栅结构的半导体器件及其制作方法.pdf

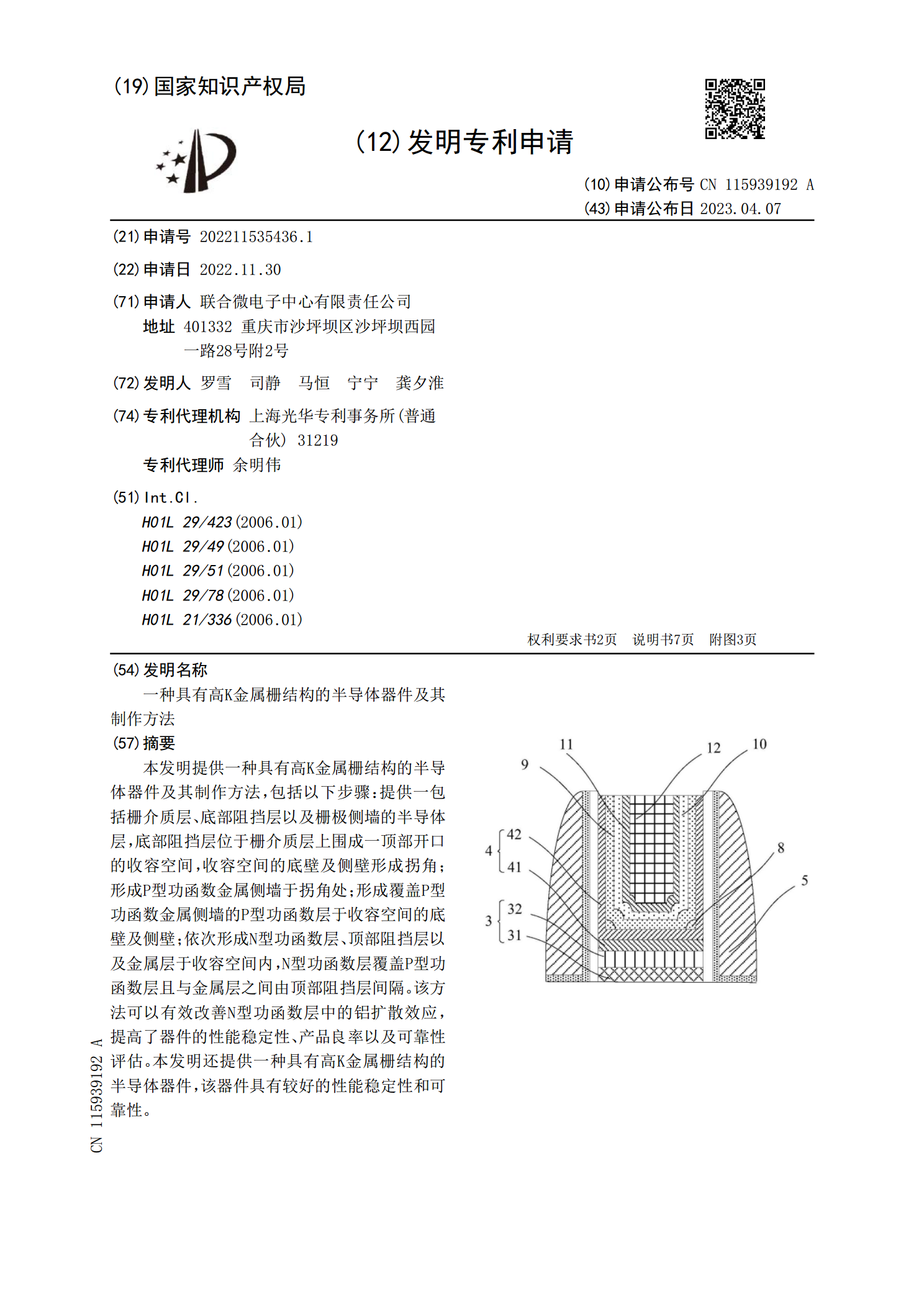

本发明提供一种具有高K金属栅结构的半导体器件及其制作方法,包括以下步骤:提供一包括栅介质层、底部阻挡层以及栅极侧墙的半导体层,底部阻挡层位于栅介质层上围成一顶部开口的收容空间,收容空间的底壁及侧壁形成拐角;形成P型功函数金属侧墙于拐角处;形成覆盖P型功函数金属侧墙的P型功函数层于收容空间的底壁及侧壁;依次形成N型功函数层、顶部阻挡层以及金属层于收容空间内,N型功函数层覆盖P型功函数层且与金属层之间由顶部阻挡层间隔。该方法可以有效改善N型功函数层中的铝扩散效应,提高了器件的性能稳定性、产品良率以及可靠性评估

铪基高K栅介质薄膜的制备及其器件性能研究的开题报告.docx

铪基高K栅介质薄膜的制备及其器件性能研究的开题报告一、研究背景随着移动互联网、智能终端等技术的迅速发展,对微波通信和射频技术的需求越来越多,也对微波器件中高性能K栅介质的要求越来越高。目前,常见的微波K栅介质材料有氧化铝、氧化锆、二氧化硅等,但它们多存在一些问题,如氧化锆的介质常数较低,氧化铝的品质因数较低,二氧化硅受热降解等。近年来,铪基高K介质材料因其介电损耗小、频率稳定、高温稳定等优点引起了广泛关注。因此,铪基高K栅介质材料在微波器件中有着广阔的应用前景。二、研究内容和方法本项目的主要研究内容是铪基

沟槽栅功率器件及其制备方法.pdf

本申请实施例公开了一种沟槽栅功率器件的制备方法及沟槽栅功率器件,其中所述制备方法包括:提供一衬底,刻蚀衬底以在衬底中形成沟槽;在沟槽的内表面上形成一场氧化层,并进一步在沟槽中形成屏蔽栅以及用于形成沟槽栅的栅极凹槽;在屏蔽栅上形成隔离介质层,并对隔离介质层回刻蚀,以保留屏蔽栅上的隔离介质层;在栅极凹槽中填充多晶硅并回刻蚀,以形成沟槽栅;去除沟槽栅所暴露出的隔离介质层;生长一层栅氧化层,在栅极凹槽的衬底侧壁形成栅氧化层,同时在暴露的屏蔽栅上形成栅间介质层。这样能解决现有技术中存在的屏蔽栅残留FOX表面的风险及