阵列基板、液晶显示面板及其点反转驱动方法.pdf

猫巷****松臣

亲,该文档总共12页,到这已经超出免费预览范围,如果喜欢就直接下载吧~

相关资料

阵列基板、液晶显示面板及其点反转驱动方法.pdf

本发明公开了一种阵列基板、液晶显示面板及其点反转驱动方法,阵列基板上设置有矩阵排列的多个子像素,每个子像素被分别划分为主区与子区,在显示画面时,主区的像素电压高于所述子区的像素电压;所述子像素被配置为,当子像素被正极性电压驱动时,第一加载路径的加载速率等于第二加载路径的加载速率,且大于第三加载路径的加载速率;当子像素被负极性电压驱动时,第一加载路径的加载速率等于第二加载路径的加载速率,且小于第三加载路径的加载速率。基于该阵列基板构成的液晶显示面板进行点反转驱动,可以解决多畴结构子像素的主区和子区的像素电极

阵列基板、显示面板及其驱动方法.pdf

本发明公开了一种阵列基板、显示面板及其驱动方法,所述阵列基板包括多条栅线和多条数据线,多条所述栅线和多条所述数据线将该阵列基板划分为多个像素单元,每个所述像素单元内包括一个开关晶体管,每个所述像素单元内还包括一个放电模块,所述放电模块的控制端与该像素单元所在行的上一行栅线相连,所述放电模块用于在扫描上一行栅线时,将本行像素单元的像素电极与低电平信号端导通。本发明通过设置放电模块,能够在每个像素单元显示之前将其像素电极上残留的电荷充分释放掉,避免了极性翻转过程中残留电荷的积累,从而能够避免残像现象的发生,改

显示面板的驱动电路、阵列基板及其驱动方法.pdf

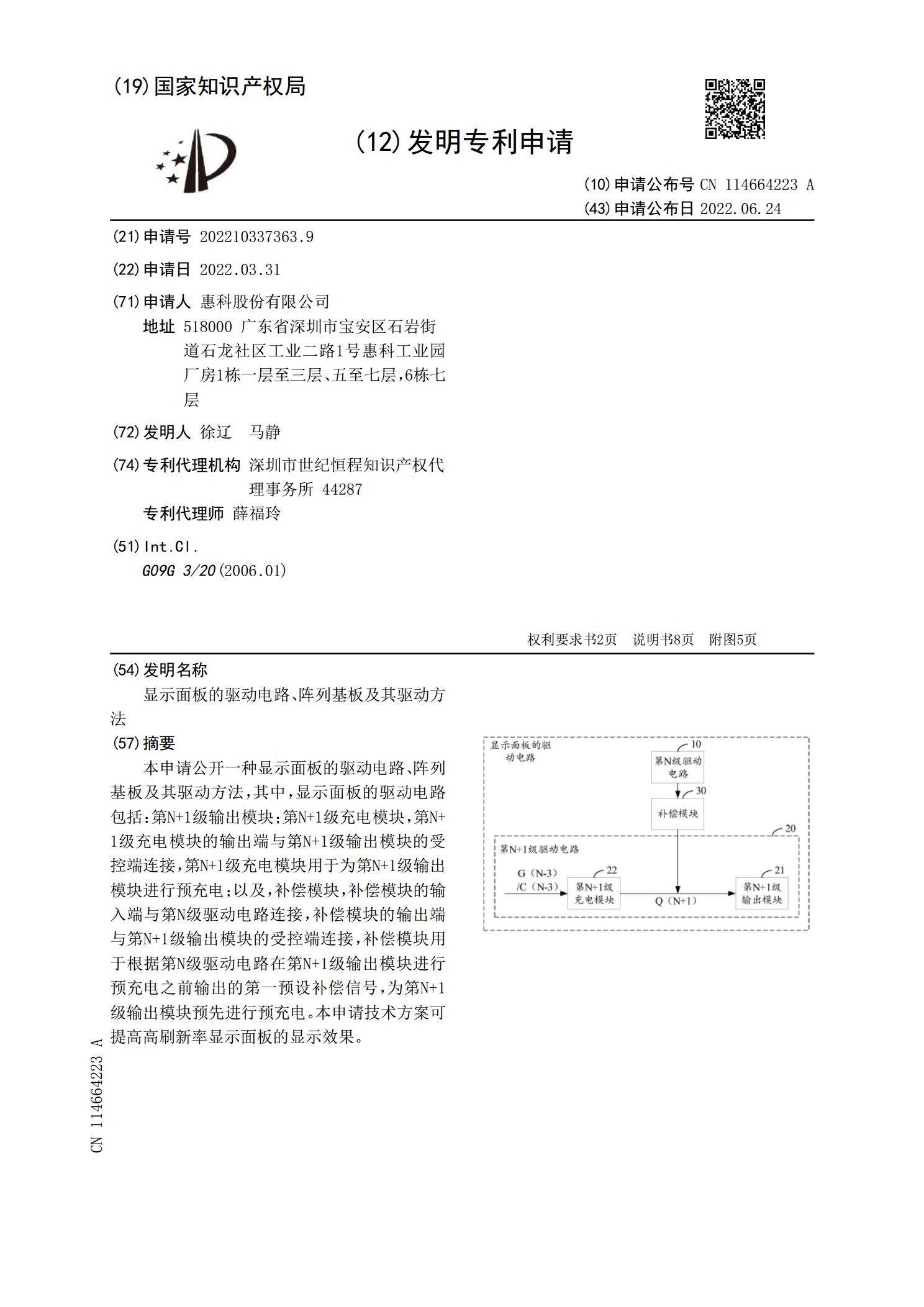

本申请公开一种显示面板的驱动电路、阵列基板及其驱动方法,其中,显示面板的驱动电路包括:第N+1级输出模块;第N+1级充电模块,第N+1级充电模块的输出端与第N+1级输出模块的受控端连接,第N+1级充电模块用于为第N+1级输出模块进行预充电;以及,补偿模块,补偿模块的输入端与第N级驱动电路连接,补偿模块的输出端与第N+1级输出模块的受控端连接,补偿模块用于根据第N级驱动电路在第N+1级输出模块进行预充电之前输出的第一预设补偿信号,为第N+1级输出模块预先进行预充电。本申请技术方案可提高高刷新率显示面板的显示

阵列基板、柔性液晶显示面板及其像素补偿方法.pdf

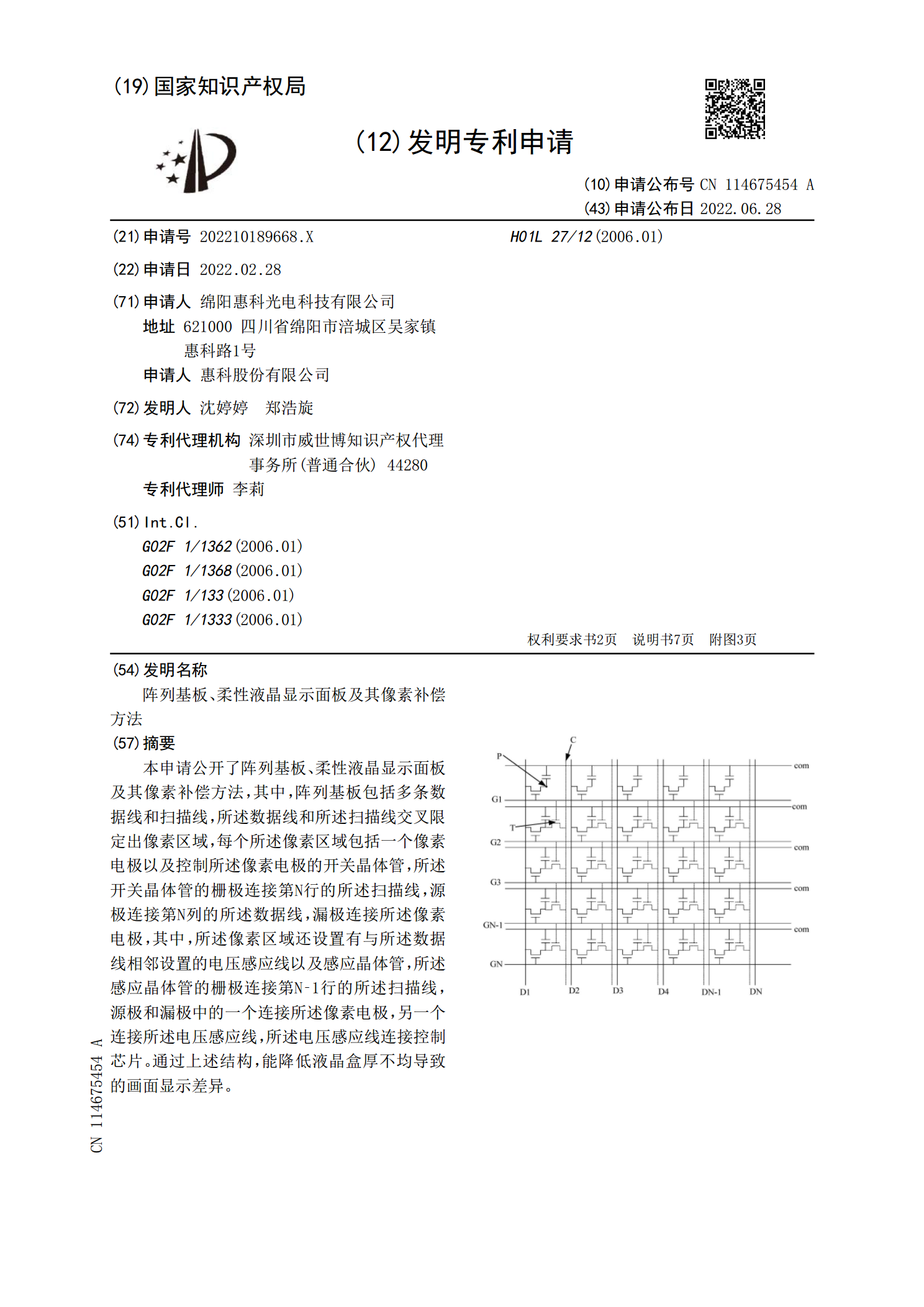

本申请公开了阵列基板、柔性液晶显示面板及其像素补偿方法,其中,阵列基板包括多条数据线和扫描线,所述数据线和所述扫描线交叉限定出像素区域,每个所述像素区域包括一个像素电极以及控制所述像素电极的开关晶体管,所述开关晶体管的栅极连接第N行的所述扫描线,源极连接第N列的所述数据线,漏极连接所述像素电极,其中,所述像素区域还设置有与所述数据线相邻设置的电压感应线以及感应晶体管,所述感应晶体管的栅极连接第N?1行的所述扫描线,源极和漏极中的一个连接所述像素电极,另一个连接所述电压感应线,所述电压感应线连接控制芯片。通

阵列基板及液晶显示面板.pdf

本申请涉及一种阵列基板及液晶显示面板。该阵列基板的驱动阵列层包括沿第一方向延伸的扫描线和沿第二方向延伸的数据线;透明金属层包括沿第一方向和第二方向交错排布的第一像素电极和第二像素电极,以及位于第一像素电极和第二像素电极的间隔区域内的屏蔽公共电极,色阻层包括与第一像素电极和第二像素电极分别对应的色阻单元,在第二方向上,第一像素电极和第二像素电极之间的间隔与扫描线交叉形成的目标区域内,相邻的两个色阻单元之间对应于目标区域的第一交叠宽度大于其余位置处相邻的两个色阻单元之间的第二交叠宽度。该阵列基板可以避免因残留