半导体基板及半导体板制作方法.pdf

雨巷****彦峰

亲,该文档总共15页,到这已经超出免费预览范围,如果喜欢就直接下载吧~

相关资料

半导体基板及半导体板制作方法.pdf

本发明涉及提供一种半导体基板及芯片制作方法,其中半导体基板包括:用于制作电路的半导体层、隔离层、和预留被消减厚度的辅助层;半导体层、隔离层、辅助层依次层叠设置,辅助层的厚度大于半导体层的厚度。采用所述的半导体基板的芯片制作方法,包括:电路制作过程,在所述半导体基板的半导体层上制作电路;降低厚度过程,对辅助层进行磨削或者蚀刻,消减辅助层的厚度,使半导体基板整体的厚度减小而获得电路基板;封装过程,电路基板进行封装获得芯片。在半导体层上制作电路时,辅助层为半导体层提供辅助支撑,半导体层不易变形,可以保证半导体电

半导体基板、半导体器件及半导体基板的制造方法.pdf

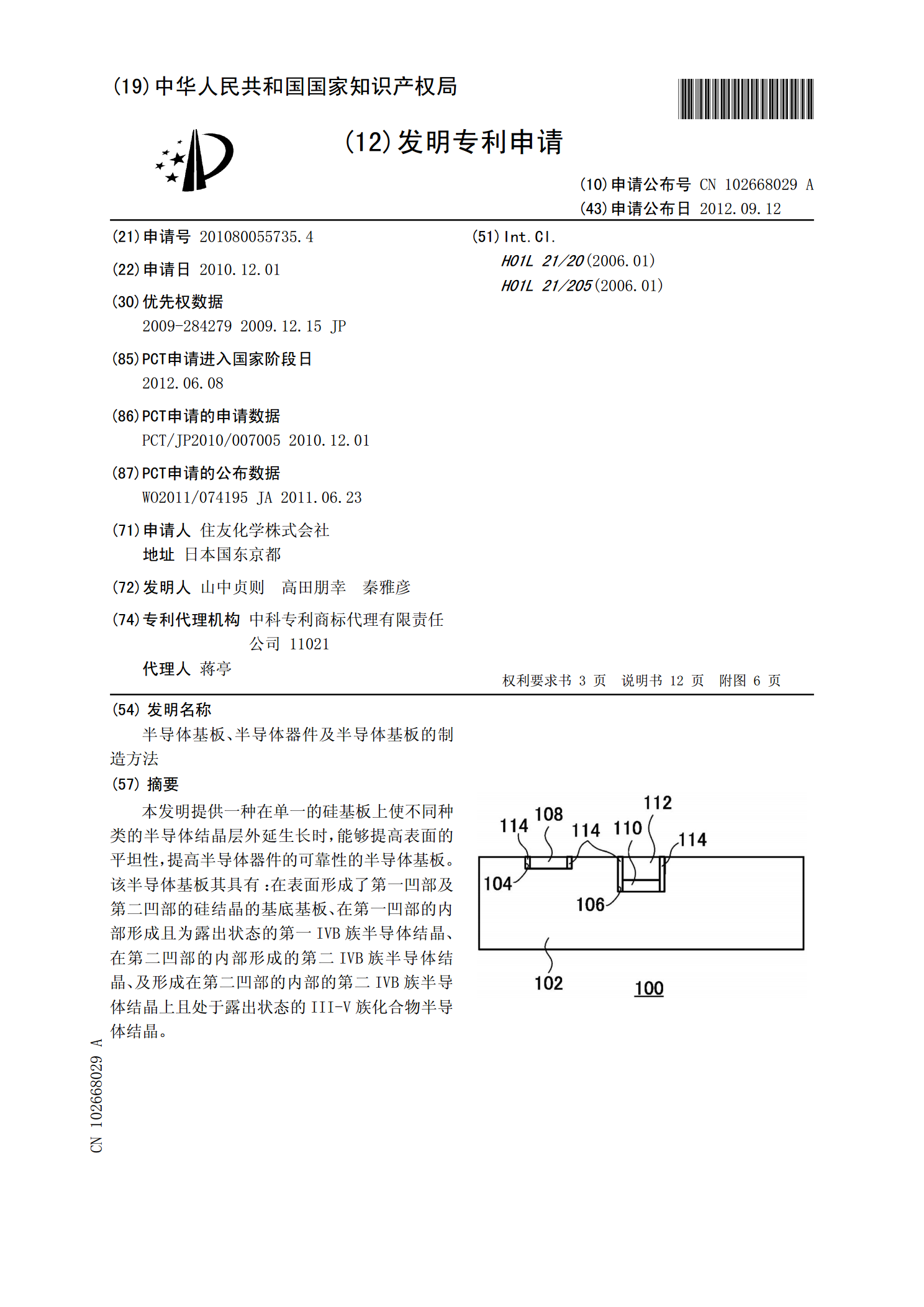

本发明提供一种在单一的硅基板上使不同种类的半导体结晶层外延生长时,能够提高表面的平坦性,提高半导体器件的可靠性的半导体基板。该半导体基板其具有:在表面形成了第一凹部及第二凹部的硅结晶的基底基板、在第一凹部的内部形成且为露出状态的第一IVB族半导体结晶、在第二凹部的内部形成的第二IVB族半导体结晶、及形成在第二凹部的内部的第二IVB族半导体结晶上且处于露出状态的III-V族化合物半导体结晶。

半导体基板的制造方法及半导体基板.pdf

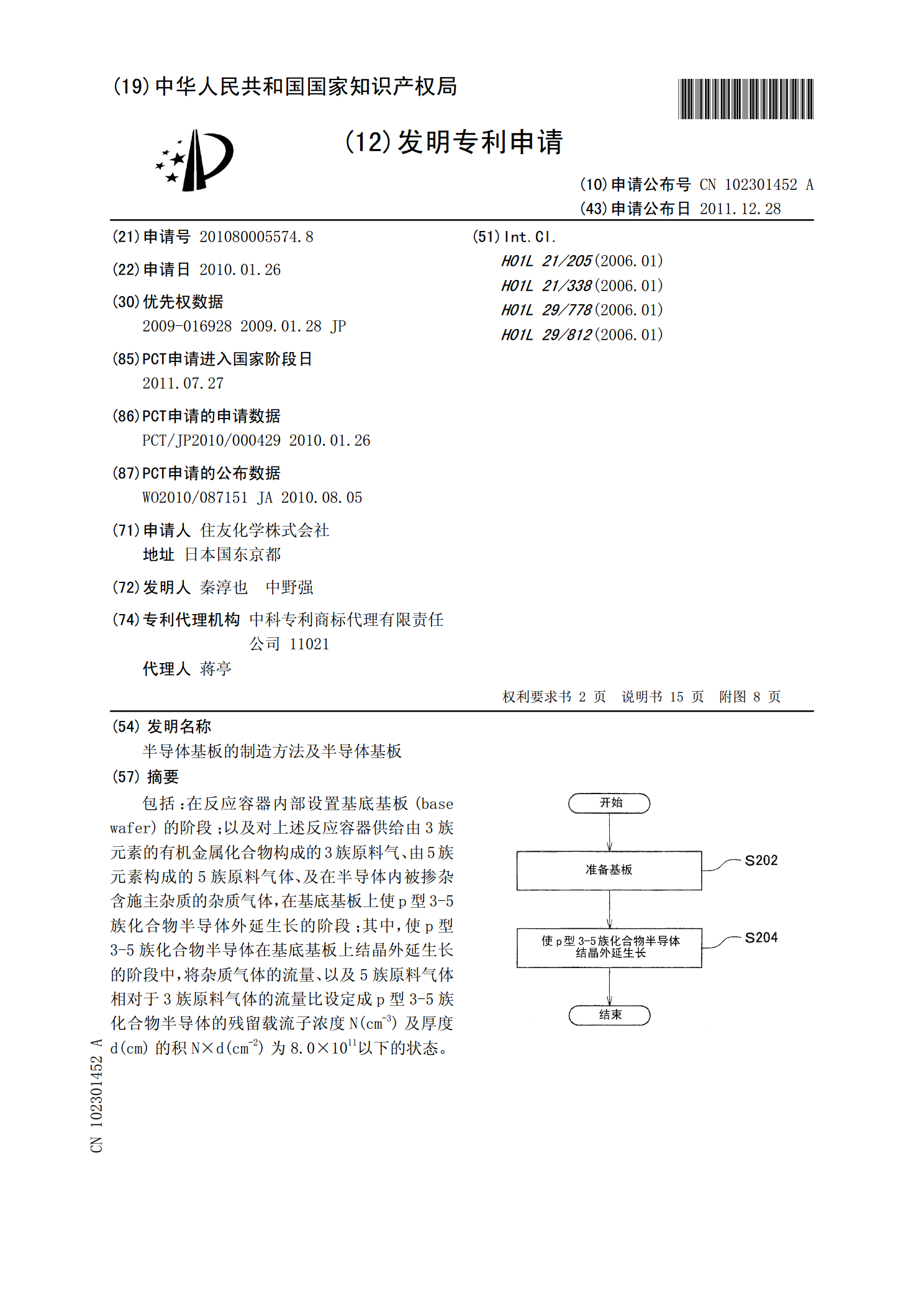

包括:在反应容器内部设置基底基板(base?wafer)的阶段;以及对上述反应容器供给由3族元素的有机金属化合物构成的3族原料气、由5族元素构成的5族原料气体、及在半导体内被掺杂含施主杂质的杂质气体,在基底基板上使p型3-5族化合物半导体外延生长的阶段;其中,使p型3-5族化合物半导体在基底基板上结晶外延生长的阶段中,将杂质气体的流量、以及5族原料气体相对于3族原料气体的流量比设定成p型3-5族化合物半导体的残留载流子浓度N(cm-3)及厚度d(cm)的积N×d(cm-2)为8.0×1011以下的状态。

半导体基板、半导体装置以及半导体基板的制造方法.pdf

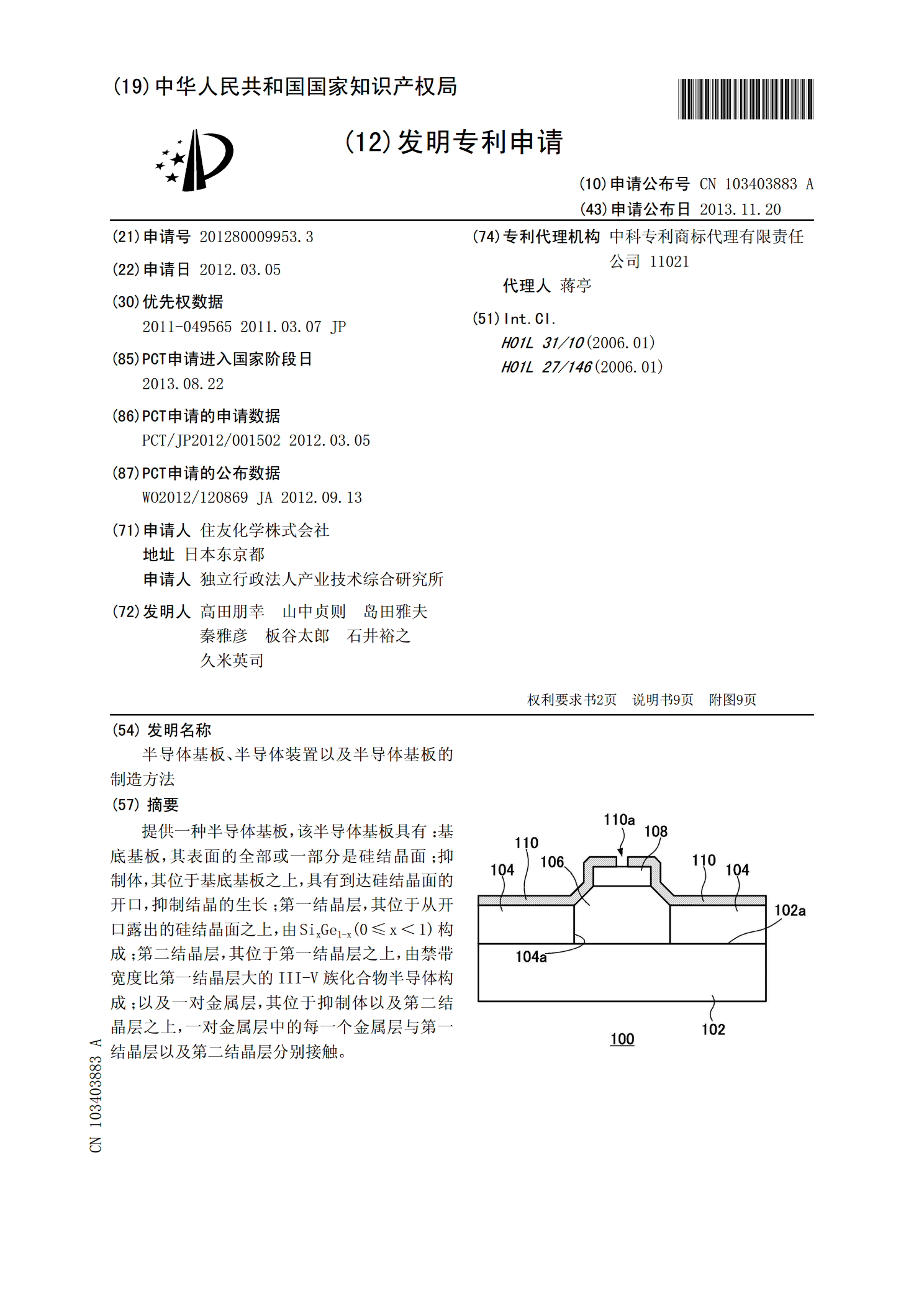

提供一种半导体基板,该半导体基板具有:基底基板,其表面的全部或一部分是硅结晶面;抑制体,其位于基底基板之上,具有到达硅结晶面的开口,抑制结晶的生长;第一结晶层,其位于从开口露出的硅结晶面之上,由SixGe1-x(0≤x<1)构成;第二结晶层,其位于第一结晶层之上,由禁带宽度比第一结晶层大的III-V族化合物半导体构成;以及一对金属层,其位于抑制体以及第二结晶层之上,一对金属层中的每一个金属层与第一结晶层以及第二结晶层分别接触。

半导体器件、半导体基板、半导体基板的制造方法及半导体器件的制造方法.pdf

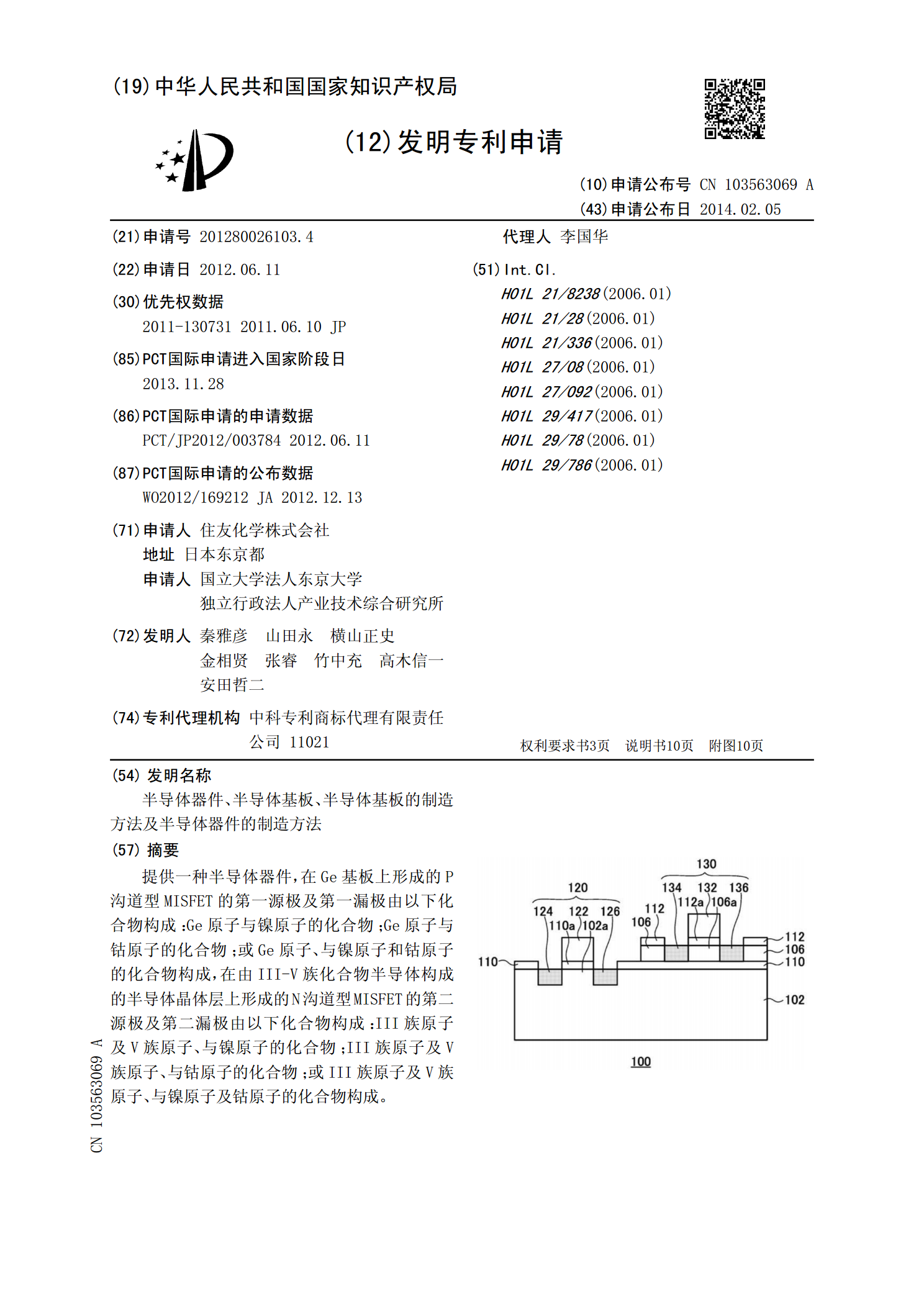

提供一种半导体器件,在Ge基板上形成的P沟道型MISFET的第一源极及第一漏极由以下化合物构成:Ge原子与镍原子的化合物;Ge原子与钴原子的化合物;或Ge原子、与镍原子和钴原子的化合物构成,在由III-V族化合物半导体构成的半导体晶体层上形成的N沟道型MISFET的第二源极及第二漏极由以下化合物构成:III族原子及V族原子、与镍原子的化合物;III族原子及V族原子、与钴原子的化合物;或III族原子及V族原子、与镍原子及钴原子的化合物构成。