形成具有栅极的电子器件的方法.pdf

韶敏****ab

亲,该文档总共15页,到这已经超出免费预览范围,如果喜欢就直接下载吧~

相关资料

形成具有栅极的电子器件的方法.pdf

本发明披露了一种形成电极器件中的栅极的方法。该方法包括以下步骤:在氮化物半导体层上沉积绝缘膜;在绝缘膜上形成具有开口的光刻胶,该开口对应于栅极;利用光刻胶作为蚀刻掩模,在绝缘膜中形成凹陷,该凹陷在绝缘膜中留下剩余部分;在氧等离子体中使光刻胶曝光;烘烤光刻胶以使其开口的边缘钝化;利用经过钝化的光刻胶作为蚀刻掩模,蚀刻绝缘膜的剩余部分;形成栅极以使其通过绝缘膜中的开口而与半导体层直接接触。

栅极的形成方法.pdf

一种栅极的形成方法,包括:提供衬底并设置第一区域以及第二区域;在衬底上分别形成第一栅极、蚀刻停止层以及层间介质层;进行第一平坦化处理,以露出第一区域的第一栅极,以及第二区域的蚀刻停止层;去除露出的蚀刻停止层直至露出第二区域的第一栅极;去除第一区域以及第二区域的第一栅极;在所述第一区域以及第二区域中第一栅极的位置处形成第二栅极。本发明具有以下优点:通过使残留在栅极上的蚀刻停止层暴露出,并选择性的去除所述蚀刻停止层,以将被残留的蚀刻停止层遮挡的栅极暴露出来,方便后续去除所述栅极的步骤的进行。

栅极的形成方法.pdf

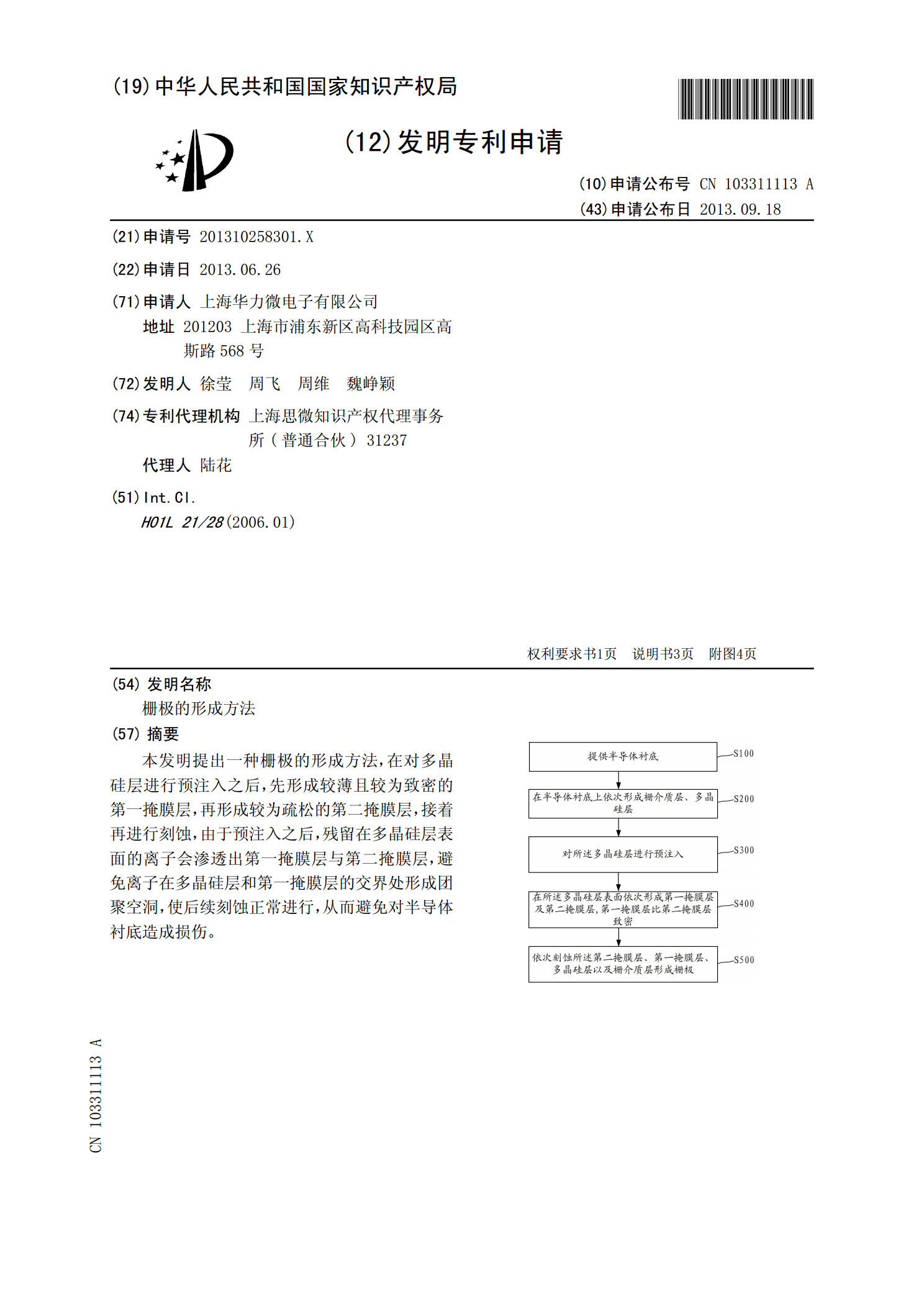

本发明提出一种栅极的形成方法,在对多晶硅层进行预注入之后,先形成较薄且较为致密的第一掩膜层,再形成较为疏松的第二掩膜层,接着再进行刻蚀,由于预注入之后,残留在多晶硅层表面的离子会渗透出第一掩膜层与第二掩膜层,避免离子在多晶硅层和第一掩膜层的交界处形成团聚空洞,使后续刻蚀正常进行,从而避免对半导体衬底造成损伤。

具有栅极切割特征的半导体器件及其形成方法.pdf

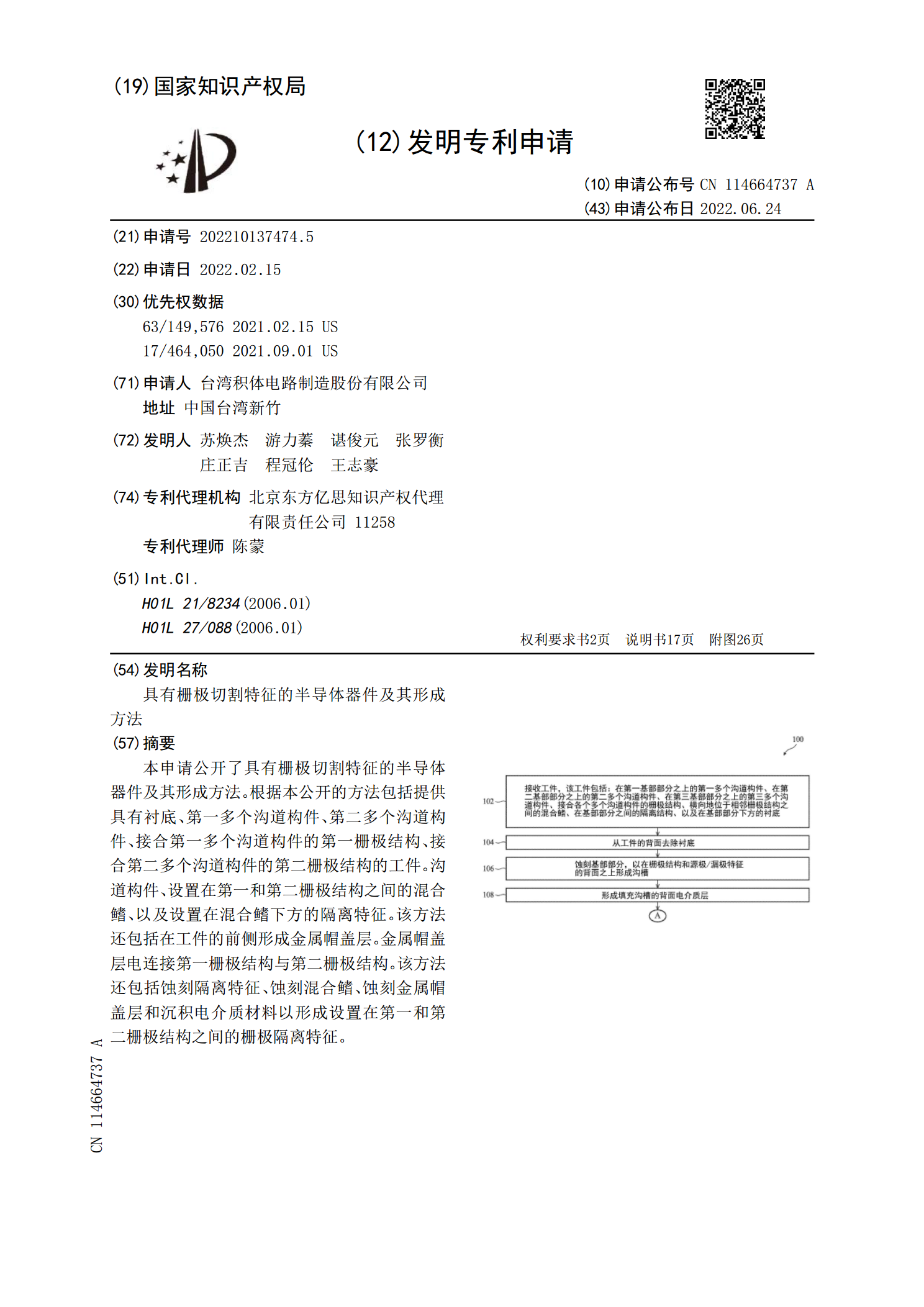

本申请公开了具有栅极切割特征的半导体器件及其形成方法。根据本公开的方法包括提供具有衬底、第一多个沟道构件、第二多个沟道构件、接合第一多个沟道构件的第一栅极结构、接合第二多个沟道构件的第二栅极结构的工件。沟道构件、设置在第一和第二栅极结构之间的混合鳍、以及设置在混合鳍下方的隔离特征。该方法还包括在工件的前侧形成金属帽盖层。金属帽盖层电连接第一栅极结构与第二栅极结构。该方法还包括蚀刻隔离特征、蚀刻混合鳍、蚀刻金属帽盖层和沉积电介质材料以形成设置在第一和第二栅极结构之间的栅极隔离特征。

金属栅极的形成方法.pdf

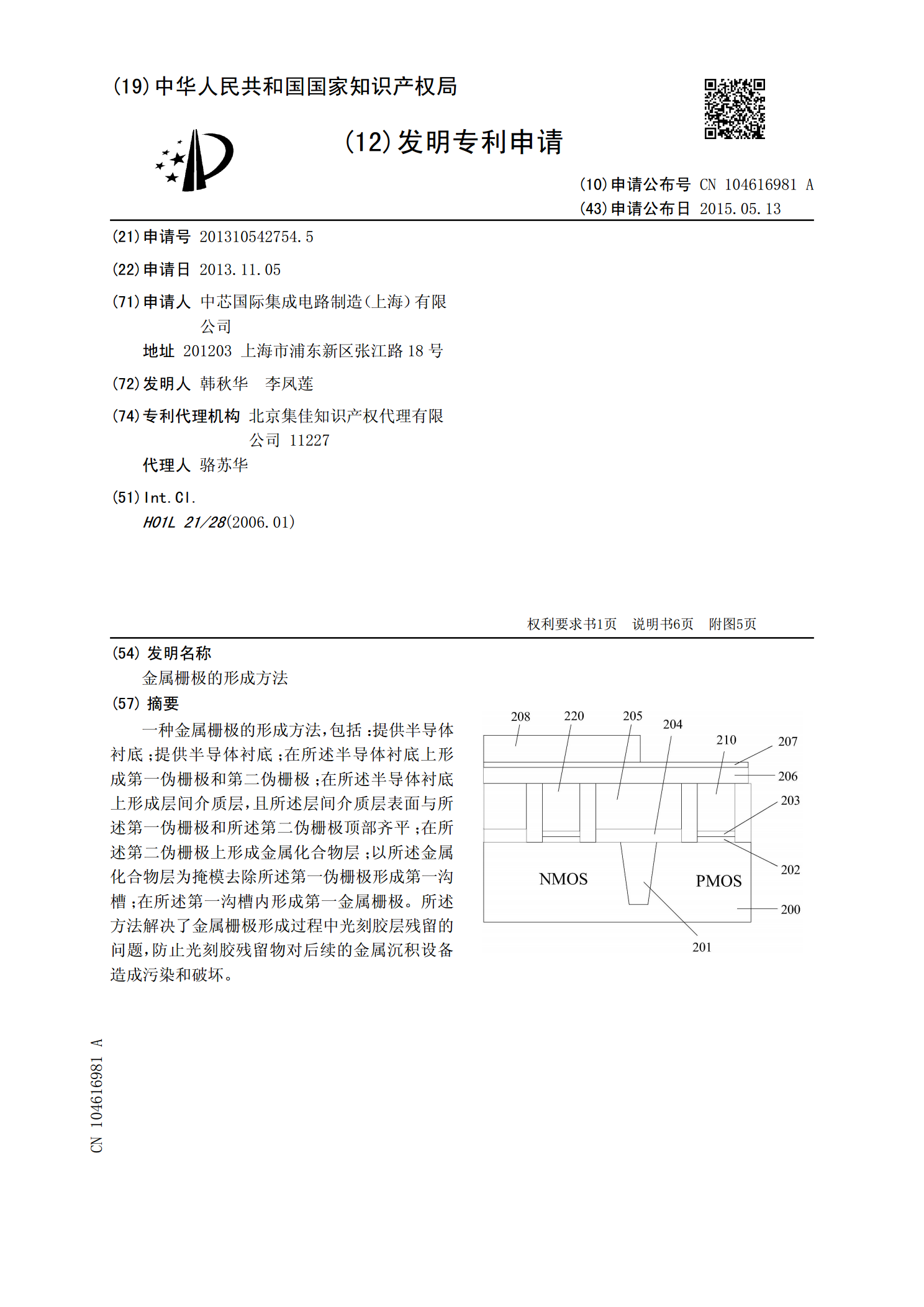

一种金属栅极的形成方法,包括:提供半导体衬底;提供半导体衬底;在所述半导体衬底上形成第一伪栅极和第二伪栅极;在所述半导体衬底上形成层间介质层,且所述层间介质层表面与所述第一伪栅极和所述第二伪栅极顶部齐平;在所述第二伪栅极上形成金属化合物层;以所述金属化合物层为掩模去除所述第一伪栅极形成第一沟槽;在所述第一沟槽内形成第一金属栅极。所述方法解决了金属栅极形成过程中光刻胶层残留的问题,防止光刻胶残留物对后续的金属沉积设备造成污染和破坏。