芯片版图设计规则检查方法.pdf

闪闪****魔王

在线预览结束,喜欢就下载吧,查找使用更方便

相关资料

芯片版图设计规则检查方法.pdf

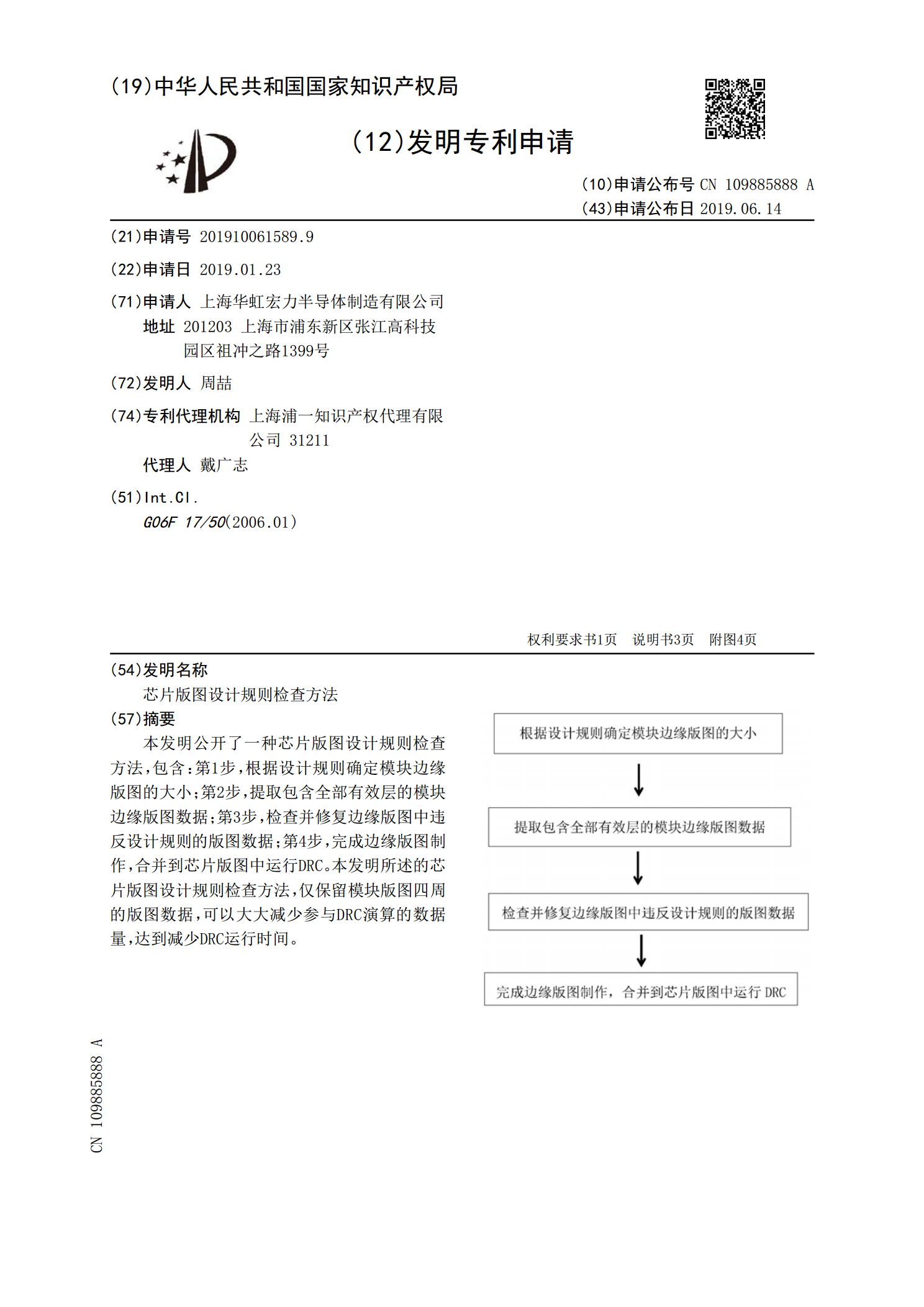

本发明公开了一种芯片版图设计规则检查方法,包含:第1步,根据设计规则确定模块边缘版图的大小;第2步,提取包含全部有效层的模块边缘版图数据;第3步,检查并修复边缘版图中违反设计规则的版图数据;第4步,完成边缘版图制作,合并到芯片版图中运行DRC。本发明所述的芯片版图设计规则检查方法,仅保留模块版图四周的版图数据,可以大大减少参与DRC演算的数据量,达到减少DRC运行时间。

版图设计规则 PPT.ppt

版图设计规则版图概述版图概述举例:工艺结构TSMC0.35umCMOS工艺定义的全部工艺层FeaturesizeL=0.18umVDD1.8V/2.5VDeepNWELLtoreducesubstratenoiseMIMcapacitor(1fF/um^2)6Metal1PolyPolycideresistor(7.5Ohm/sq)HighN/Pimplantresistor(59Ohm/sq,133Ohm/sq)M1-M5(78mOhm/sq)Thick-top-metal(18mOhm/sq)设计规则

硅栅CMOS电路版图设计规则检查全面性探讨.docx

硅栅CMOS电路版图设计规则检查全面性探讨标题:硅栅CMOS电路版图设计规则检查全面性探讨摘要:硅栅互补型金属氧化物半导体(CMOS)技术是现代集成电路设计中最常用的技术之一。作为CMOS设计的重要环节,电路版图设计规则检查具有关键性意义,对保证电路的可靠性、性能和制造工艺的一致性至关重要。本论文将探讨硅栅CMOS电路版图设计规则检查的全面性,并分析其对电路设计的影响。1.引言CMOS技术作为目前最广泛使用的集成电路制造技术之一,在计算机芯片、移动通信和数字电子等领域发挥了重要作用。电路版图设计规则检查是

检查规则设计支持方法,检查规则设计支持系统,和检查规则设计支持程序.pdf

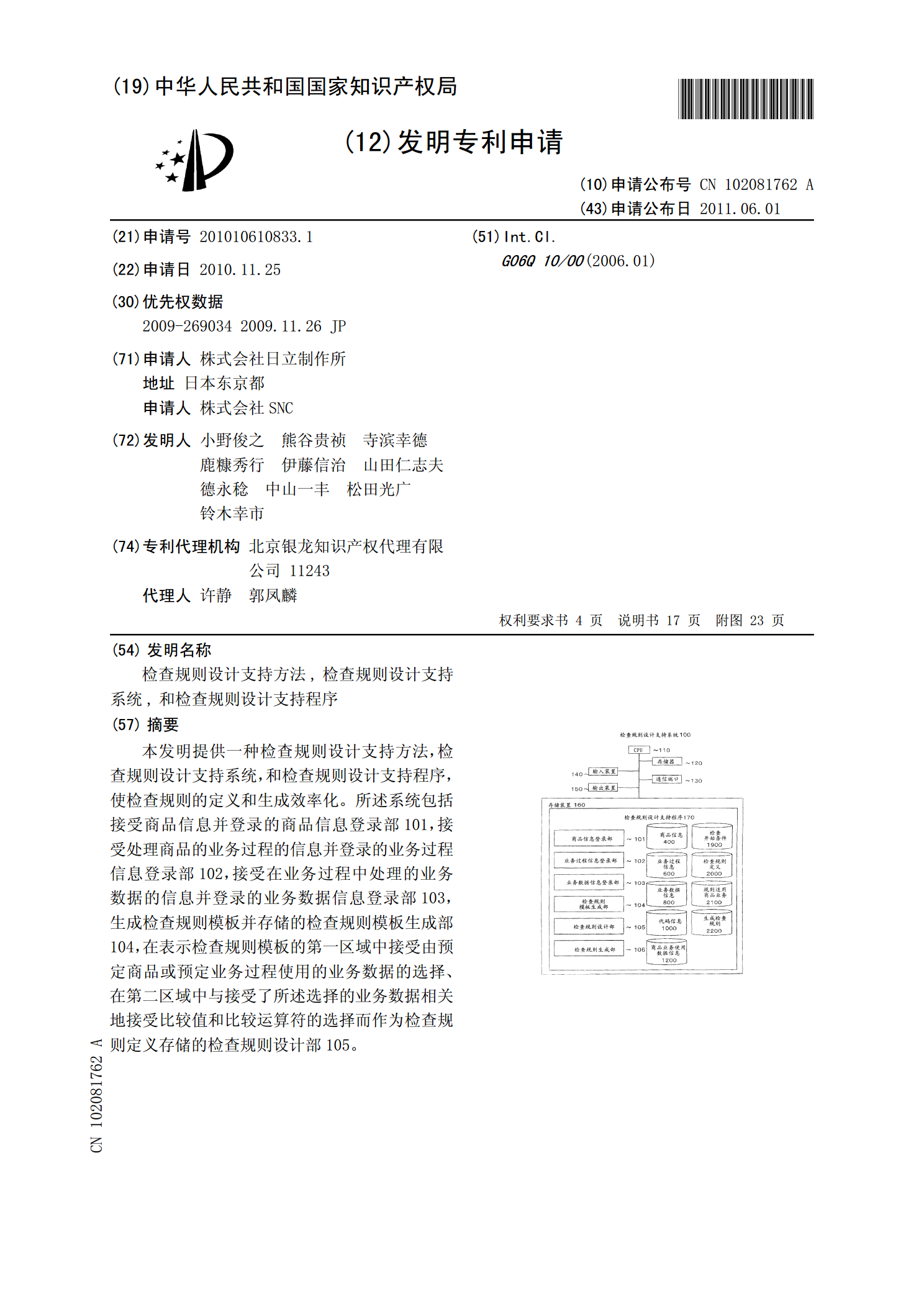

本发明提供一种检查规则设计支持方法,检查规则设计支持系统,和检查规则设计支持程序,使检查规则的定义和生成效率化。所述系统包括接受商品信息并登录的商品信息登录部101,接受处理商品的业务过程的信息并登录的业务过程信息登录部102,接受在业务过程中处理的业务数据的信息并登录的业务数据信息登录部103,生成检查规则模板并存储的检查规则模板生成部104,在表示检查规则模板的第一区域中接受由预定商品或预定业务过程使用的业务数据的选择、在第二区域中与接受了所述选择的业务数据相关地接受比较值和比较运算符的选择而作为检查

适用于引入定制芯片的切割版图设计方法及其制备的芯片.pdf

本发明公开了适用于引入定制芯片的切割版图设计方法及其制备的芯片,属于半导体技术领域,根据芯片外型参数进行芯片分类处理,得到常规芯片数据和定制芯片数据;根据常规芯片数据以及晶圆可操作面积上限值进行排版计算,输出所有具有贯穿划片槽的版图设计草图;根据定制芯片数据对版图设计草图中的预留位置进行二次设计,输出二次版图设计草图。本发明先对常规芯片进行排版设计,得到具有贯穿划片槽的版图设计草图,大大降低了二次切割风险;在预留面积的情况下,规划定制芯片的划片槽设计,将版图设计草图整体变化控制在最小范围,在不影响常规芯片