图像编码方法、装置、电子设备和计算机可读存储介质.pdf

Ma****57

亲,该文档总共19页,到这已经超出免费预览范围,如果喜欢就直接下载吧~

相关资料

图像编码方法、装置、电子设备和计算机可读存储介质.pdf

本发明公开了一种图像编码方法、装置、设备和计算机可读存储介质。该方法包括:获取待编码的原始图像;对原始图像中的像素块进行提取,得到至少两种类型的像素块;将目标类型的像素块传送到FPGA,以通过FPGA对目标类型的像素块执行编码处理,接收FPGA发送的第一编码结果;对其余类型的像素块执行编码处理,并得到第二编码结果;根据第一编码结果和第二编码结果,生成目标编码格式的图像。本发明通过将部分类型的像素块传送到FPGA执行编码处理,将部分类型的像素块保留在CPU执行编码处理,可以解决CPU编码目标图像时编码吞吐率

图像编码方法、装置、电子设备和计算机可读存储介质.pdf

本申请涉及一种图像编码方法、装置、电子设备和计算机可读存储介质。上述方法包括:获取参考图像中主体所在的主体区域;获取参考图像中包含的像素块,并采用多种编码模式对像素块进行编码处理,得到像素块在每一种编码模式下对应的编码数据;基于像素块与主体区域的位置关系确定像素块的目标代价参数;根据像素块的目标代价参数及在每一种编码模式下对应的编码数据,得到像素块在每一种编码模式下对应的编码代价;将编码代价最小的编码模式对应的编码数据作为像素块对应的目标编码数据。即可以动态调整像素块的失真权重值或码率权重值,从而偏向性地

图像编码方法、装置、NVR及可读存储介质.pdf

本发明实施例提供的图像编码方法、装置、NVR及可读存储介质,在存在感兴趣区域时,对所述感兴趣区域优先编码,在完成对所述感兴趣区域优先编码后对所述预处理图像中的其他区域进行编码,其中在编码过程中对所述感兴趣区域编码的压缩率小于对其他区域编码的压缩率;最后,对编码后的编码图像进行JPEG编码处理,得到JPEG格式的图像。上述编码过程中,对感兴趣区域采用较小的压缩率进行压缩,对于其他区域采用较大的压缩率进行压缩,从而可以确保在进行JPEG编码前的编码图像的大小不会太大,同时又保留了感兴趣区域的图像特征,再经过J

图像处理方法、装置、计算机可读存储介质和电子设备.pdf

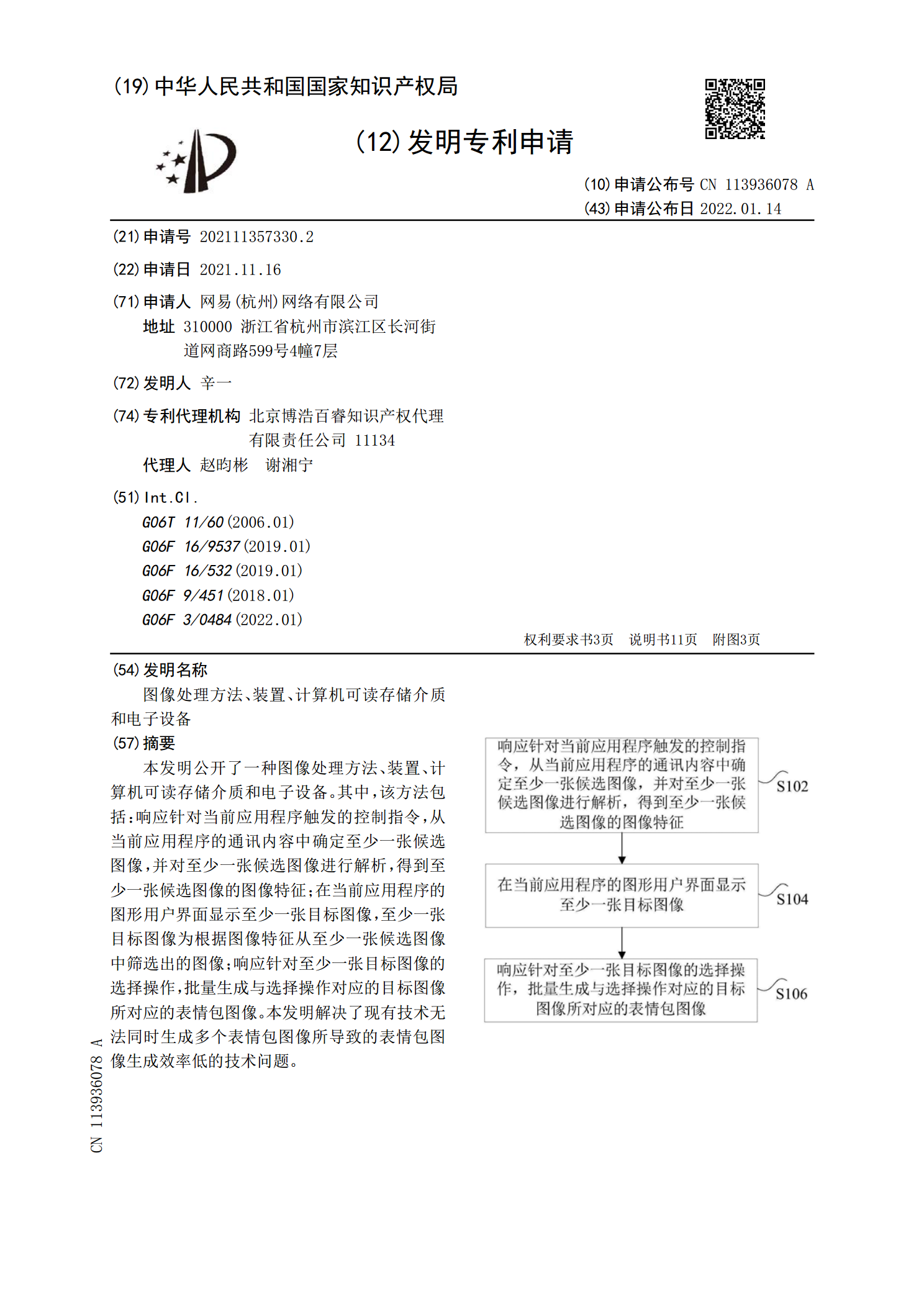

本发明公开了一种图像处理方法、装置、计算机可读存储介质和电子设备。其中,该方法包括:响应针对当前应用程序触发的控制指令,从当前应用程序的通讯内容中确定至少一张候选图像,并对至少一张候选图像进行解析,得到至少一张候选图像的图像特征;在当前应用程序的图形用户界面显示至少一张目标图像,至少一张目标图像为根据图像特征从至少一张候选图像中筛选出的图像;响应针对至少一张目标图像的选择操作,批量生成与选择操作对应的目标图像所对应的表情包图像。本发明解决了现有技术无法同时生成多个表情包图像所导致的表情包图像生成效率低的技

图像处理方法、装置、电子设备和计算机可读存储介质.pdf

本申请涉及一种图像处理方法、装置、电子设备和计算机可读存储介质。上述方法,包括:对待处理图像进行人脸识别,识别所述待处理图像中人脸图像;获取与所述人脸图像对应的第一正脸图像;根据预设规则从所述第一正脸图像上选取多个特征点,分别获取所述多个特征点与人脸轮廓的水平距离值;根据所述水平距离值之间的比值确定所述人脸图像对应的脸型;根据所述脸型调整所述人脸图像中五官和所述人脸图像的轮廓。上述方法,在待处理图像中识别出人脸图像后,可分析获取人脸图像的脸型,再根据人脸图像的脸型对应调整人脸图像中五官大小和人脸图像的轮廓