一种基于阵列天线抗干扰BDS/GPS接收机.pdf

英哲****公主

亲,该文档总共12页,到这已经超出免费预览范围,如果喜欢就直接下载吧~

相关资料

一种基于阵列天线抗干扰BDS/GPS接收机.pdf

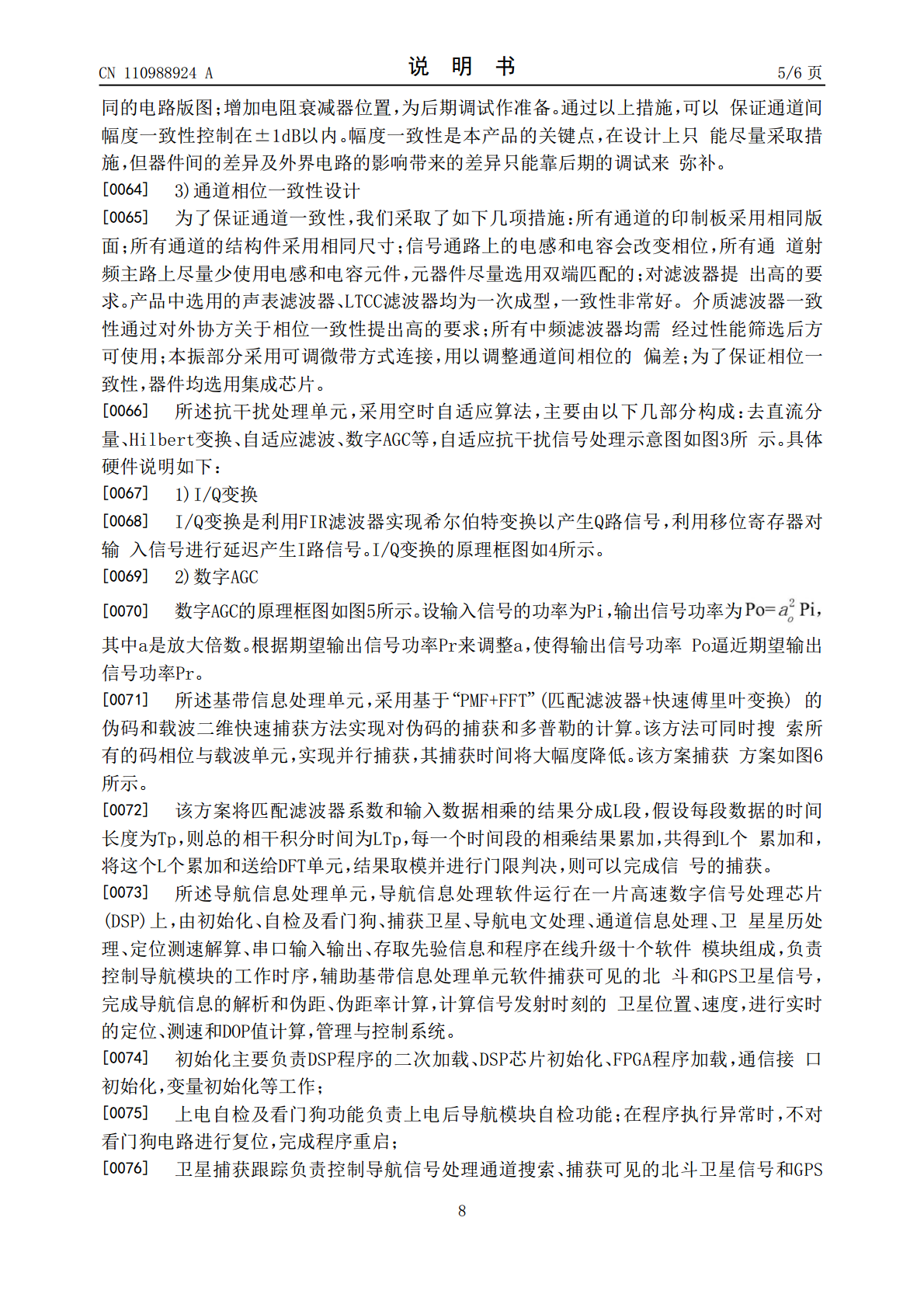

本发明公开了一种基于阵列天线抗干扰BDS/GPS接收机,以射频芯片、DSP和FPGA为主的硬件平台,包括:射频处理单元、抗干扰处理单元、基带信息处理单元、导航信息处理单元、电源单元;射频单元将天线端输入的BD射频信号和GPS射频信号放大、变频、滤波转换为模拟中频信号,BD中频信号经过A/D采样量化后进入抗干扰处理单元,GPS中频信号进入基带信息处理单元;抗干扰处理单元,对信号进行抗干扰处理,去除干扰信号,保留有用的卫星导航信号,将保留的卫星信号送至基带信息处理单元;基带信息处理单元,对BD中频信号和GPS

基于阵列天线的卫星导航接收机抗干扰技术研究与实现的任务书.docx

基于阵列天线的卫星导航接收机抗干扰技术研究与实现的任务书任务书一、任务背景随着现代科技的飞速发展,卫星导航技术如今已经广泛应用于全球定位、导航、授时、精密测量和遥感等领域,为人类的各个方面带来了便利和改善。目前全球卫星导航系统主要有美国的GPS系统、俄罗斯的GLONASS系统、欧洲的伽利略系统和中国的北斗系统。卫星导航技术的应用渐趋广泛,但是在卫星导航接收机的研究中,怎样有效地降低系统的信噪比,抗干扰,保证接收机的可靠性和稳定性,一直是制约卫星导航技术进一步发展的重要问题。因此,本次研究以阵列天线的卫星导

基于阵列天线处理的GPS信号抗干扰研究.docx

基于阵列天线处理的GPS信号抗干扰研究摘要全球定位系统(GPS)在今天的社会已经成为一项普遍使用的技术。然而,在实际应用中,GPS信号常常受到干扰和噪声的影响,进而影响到其定位和导航的精度。因此,如何提高GPS信号的抗干扰能力是目前的研究热点之一。本文介绍了一种基于阵列天线处理的GPS信号抗干扰研究方法。该方法将多个天线阵列组合在一起,通过信号的相位差和强度差来计算信号的角度和距离,并通过计算处理出具有更高抗干扰性能的GPS信号数据。研究表明,该方法可以有效地提高GPS信号的信号质量和抗干扰能力。本文还对

基于阵列天线结构优化的自适应抗干扰研究.docx

基于阵列天线结构优化的自适应抗干扰研究基于阵列天线结构优化的自适应抗干扰研究摘要:随着通信领域的不断发展,抗干扰技术的研究变得日益重要。阵列天线是一种能够提高通信系统性能的关键技术。本文通过对阵列天线结构的优化和自适应抗干扰算法的研究,提出了一种新的自适应抗干扰系统。实验结果表明,该系统在抗干扰性能和信号接收质量方面具有显著的优势。1.引言在现代通信系统中,干扰问题成为了一个严重的挑战。干扰会导致通信信号质量下降,甚至使通信系统无法正常工作。因此,研究如何优化阵列天线结构以提高抗干扰性能成为了一个重要的课

基于RLS算法的阵列天线抗干扰性能研究.docx

基于RLS算法的阵列天线抗干扰性能研究基于RLS算法的阵列天线抗干扰性能研究摘要:随着无线通信技术的迅猛发展,阵列天线系统作为一种重要的无线通信技术方案,被广泛应用于移动通信、雷达、无线局域网等领域。然而,由于无线信号传播环境的复杂性和多径效应的存在,阵列天线系统往往面临着严峻的干扰问题。针对这一问题,本文基于递归最小二乘(RLS)算法,对阵列天线的抗干扰性能进行研究,并通过模拟实验验证了算法在抑制干扰方面的有效性。研究结果表明,基于RLS算法的阵列天线系统能够显著提升抗干扰能力,具有良好的实用性和可行性