基带拉远传输装置、基站、拉远覆盖单元及无线覆盖系统.pdf

盼易****君a

亲,该文档总共12页,到这已经超出免费预览范围,如果喜欢就直接下载吧~

相关资料

基带拉远传输装置、基站、拉远覆盖单元及无线覆盖系统.pdf

本申请提供一种基带拉远传输装置、基站、拉远覆盖单元及无线覆盖系统;基带拉远传输装置包括连接基站的近端接口电路和通过导线连接的至少一个连接拉远覆盖单元的远端接口电路;近端接口电路用于将基站的下行基带IQ数据及控制量转换成以太网格式的下行数据包,并通过导线传输至远端接口电路,解析上行数据包得到上行通信数据;远端接口电路用于解析下行数据包得到下行通信数据传输至拉远覆盖单元进行覆盖发射,将拉远覆盖单元的上行基带IQ数据及状态量转换成以太网格式的上行数据包,并通过导线发送至近端接口电路;该技术在保留毫微基站原有优势

拉远传输覆盖方法、系统以及拉远单元.pdf

本公开涉及一种拉远传输覆盖方法、系统以及拉远单元,其中,方法包括:接收多个载波信号,基于多个载波信号进行处理,获取多路射频信号,将多路射频信号进行功率放大后输入拉远单元中的滤波一体化模块,以对多路射频信号进行滤波,基于多路射频信号的信号类型对滤波后的多路射频信号进行合并,生成目标带宽的射频信号发送给天线;其中,滤波一体化模块包括滤波器、环形器和电桥依次连接。由此,实现每根天线口大带宽信号发射,满足大带宽大功率信号覆盖需求,降低建网成本,提升建网便利度,同时提高通信质量。

噪声抑制方法、装置及LTE数字微波射频拉远覆盖系统.pdf

本发明公开了一种噪声抑制方法、装置及LTE数字微波射频拉远覆盖系统,用以解决现有技术中的LTE数字微波射频拉远覆盖系统存在的基站底噪被抬升的问题。所述方法包括:应用于LTE数字微波射频拉远覆盖系统的远端微波传输系统的上行基带处理器通过对模拟下变频器发送来的模拟中频信号执行模数A/D转换,得到多个数字子频带信号;通过分别对各数字子频带信号执行数字下变频处理,得到多个子频带基带信号;分别比较各子频带基带信号的载噪比与预定的载噪比阈值;对载噪比大于所述载噪比阈值的子频带基带信号执行数字上变频处理,得到相应的数字

数据传输方法、基带单元、射频拉远单元及网络系统.pdf

本发明提供一种数据传输方法、基带单元、射频拉远单元及网络系统。该方法包括:将蜂窝数据和IP业务数据进行组帧处理,获得CPRI帧,并将CPRI帧传输至射频拉远单元;和/或,接收射频拉远单元传输的CPRI帧,并将CPRI帧中承载的蜂窝数据传输至核心网,将CPRI帧中承载的IP业务数据传输至业务处理平台;CPRI帧的帧结构中的第一部分子信道对应的控制时隙承载蜂窝数据,CPRI帧的帧结构中的第二部分子信道对应的控制时隙承载IP业务数据。本申请复用传输蜂窝数据的CPRI帧结构中的预留控制时隙传输IP业务数据,实现蜂

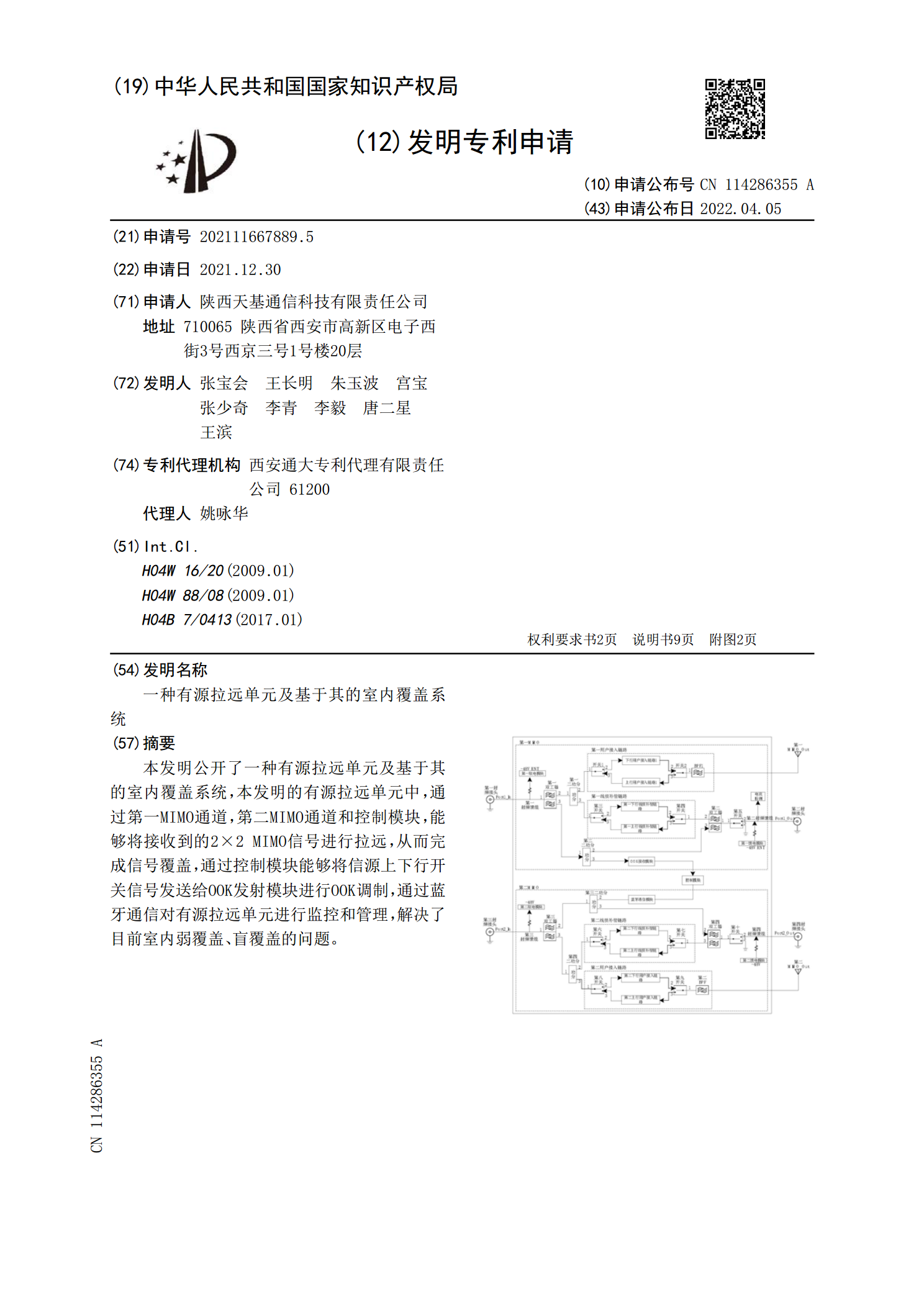

一种有源拉远单元及基于其的室内覆盖系统.pdf

本发明公开了一种有源拉远单元及基于其的室内覆盖系统,本发明的有源拉远单元中,通过第一MIMO通道,第二MIMO通道和控制模块,能够将接收到的2×2MIMO信号进行拉远,从而完成信号覆盖,通过控制模块能够将信源上下行开关信号发送给OOK发射模块进行OOK调制,通过蓝牙通信对有源拉远单元进行监控和管理,解决了目前室内弱覆盖、盲覆盖的问题。