显示面板、拼接屏.pdf

努力****妙风

亲,该文档总共13页,到这已经超出免费预览范围,如果喜欢就直接下载吧~

相关资料

显示面板、拼接屏.pdf

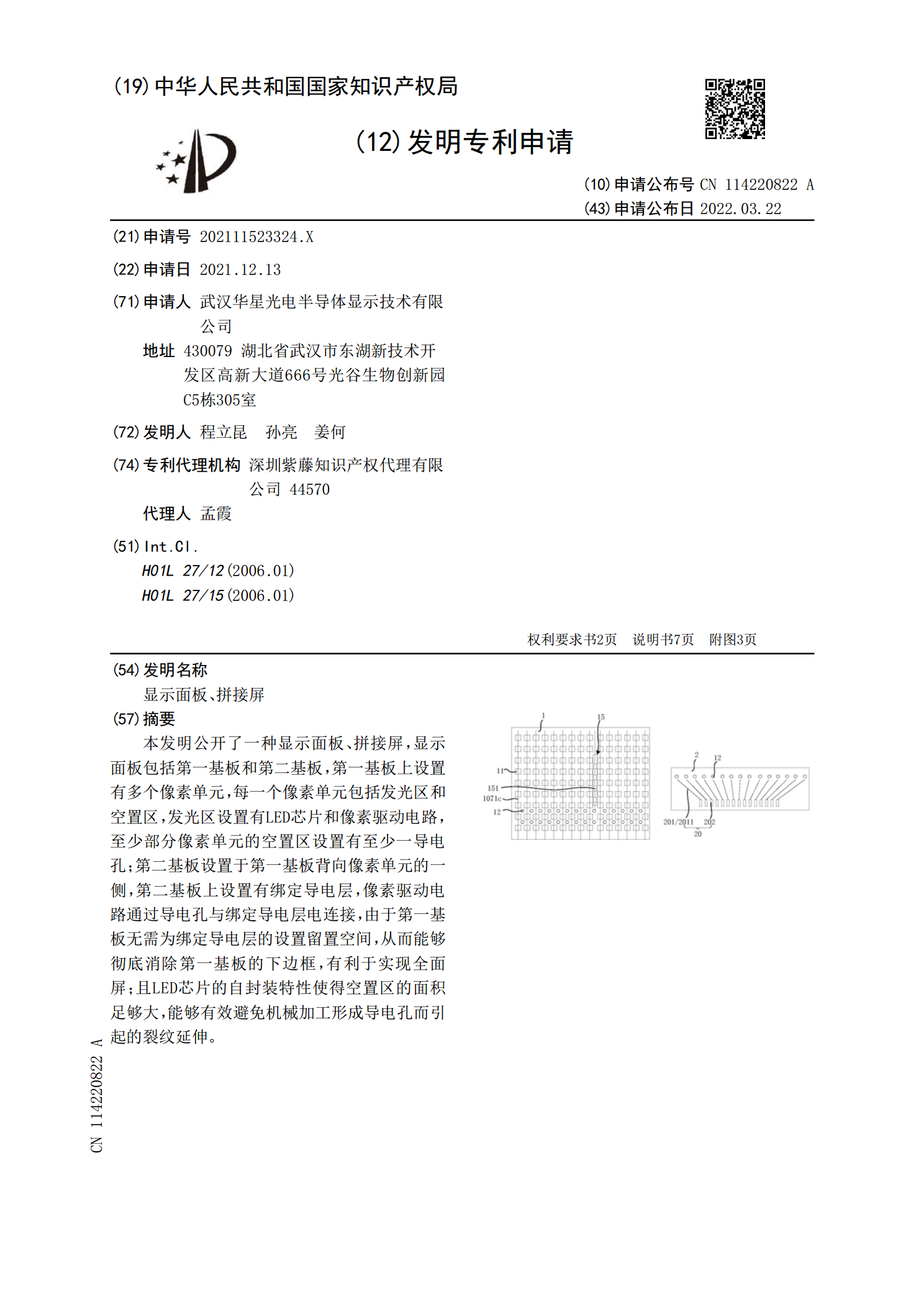

本发明公开了一种显示面板、拼接屏,显示面板包括第一基板和第二基板,第一基板上设置有多个像素单元,每一个像素单元包括发光区和空置区,发光区设置有LED芯片和像素驱动电路,至少部分像素单元的空置区设置有至少一导电孔;第二基板设置于第一基板背向像素单元的一侧,第二基板上设置有绑定导电层,像素驱动电路通过导电孔与绑定导电层电连接,由于第一基板无需为绑定导电层的设置留置空间,从而能够彻底消除第一基板的下边框,有利于实现全面屏;且LED芯片的自封装特性使得空置区的面积足够大,能够有效避免机械加工形成导电孔而引起的裂纹

显示面板、拼接屏和显示装置.pdf

本发明公开了一种显示面板、拼接屏和显示装置,显示面板包括:相对设置的第一面和第二面;显示面板的外边缘至少包括一段预留区,预留区包括多个由第一面向第二面凹陷的第一凹槽和多个由第二面向第一面凹陷的第二凹槽,沿垂直于显示面板的出光面所在平面的方向上,第一凹槽与第二凹槽至少部分无交叠,沿第一方向上,第一凹槽在显示面板的出光面所在平面的正投影与第二凹槽在显示面板的出光面所在平面的正投影相邻。显示面板既能单独地进行显示,同时在预留区设置第一凹槽、第一凸起、第二凹槽和第二凸起形成镂空结构,为多块显示面板的拼接预留位置。

拼接显示面板的制备方法、拼接显示面板及面板单元.pdf

一种拼接显示面板的制备方法、拼接显示面板及面板单元,拼接显示面板的制备方法,包括如下步骤:提供支撑板及多个面板单元,在每一所述面板单元上均形成有驱动线路;将多个所述面板单元在所述支撑板上对位拼接;在两个所述面板单元上对应的驱动线路之间制作连接线,通过连接线的设置,使得单个面板单元上的驱动线路在整个显示面板上形成完整的驱动线路;在多个所述面板单元的上表面设置盖板。该拼接显示面板的制备方法能够显著减少两个拼接屏之间缝隙的宽度,且通过一次拼接工艺就可以完成显示面板的拼接,制作方法简便,可靠率较高。

拼接显示面板及拼接显示装置.pdf

本申请公开了一种拼接显示面板及拼接显示装置,至少两个显示面板之间拼接设置形成有缝隙;发光二极管基板包括柔性电路板和多个发光二极管,柔性电路板包括承载部、第一弯折部、第二弯折部、第一支撑部和第二支撑部,发光二极管设置在承载部上,承载部的一侧连接于第一弯折部,第一弯折部连接于第一支撑部,承载部的另一侧连接于第二弯折部,第二弯折部连接于第二支撑部;第一支撑部和第二支撑部分别与承载部部分重叠设置。发光二极管基板布设于相邻的两个显示面板之间,第一支撑部设置在一显示面板上,第二支撑部设置在另一显示面板上,承载部设置在

拼接显示屏的制造方法及拼接显示屏.pdf

本公开提供一种拼接显示屏的制造方法及拼接显示屏,该方法包括:提供母板,对母板进行第一次切割,得到多个显示面板,显示面板包括位于显示区外围的第一边框区和位于第一边框区外围的预留切割边框区;提供保护盖板;将保护盖板与显示面板贴合一起,组成子显示模组,其中保护盖板包括位于显示区外围的第二边框区,第一边框区的边框宽度大于或等于第二边框区的边框宽度;对子显示模组进行第二次切割,第二次切割的切割线为第一边框区和预留切割边框区之间的边界线,除去预留切割边框区,得到子显示屏;将多个子显示屏进行拼接,得到拼接显示屏。本公开