一种硅通孔互联的空腔结构及其形成方法.pdf

黛娥****ak

亲,该文档总共12页,到这已经超出免费预览范围,如果喜欢就直接下载吧~

相关资料

一种硅通孔互联的空腔结构及其形成方法.pdf

本发明属于半导体三维集成技术领域,公开了一种硅通孔互联的空腔结构及其形成方法:提供第一硅晶圆,第一硅晶圆正面带有器件层;在第一硅晶圆的器件层上沉积第一介质层,并在第一介质层上刻蚀形成TDV;在TDV上沉积第二介质层,以使TDV开口封闭且内部中空;在封口后的第一硅晶圆正面进行RDL,形成布线层;将第一硅晶圆与第二硅晶圆键合并减薄,第二硅晶圆为也具有布线层的硅晶圆,第一硅晶圆的布线层与第二硅晶圆的布线层相对设置;在键合后的第一硅晶圆的背面进行刻蚀,使得TDV再次开口连通,且被刻蚀后的TDV底部停留在第一停留层

硅通孔布局结构、硅通孔互联结构的形成方法.pdf

一种硅通孔布局结构、硅通孔互联结构的形成方法,其中,硅通孔互联结构的形成方法包括:提供半导体衬底,所述半导体衬底具有第一区域和第二区域;刻蚀第一区域和第二区域的半导体衬底,在第一区域和第二区域的半导体衬底中形成若干分立的通孔,第一区域的通孔密度大于通孔的平均密度,且所述通孔的平均密度小于等于2%;在所述半导体衬底上形成金属层,金属层填充满所述通孔;采用化学机械研磨工艺平坦化所述金属层,形成硅通孔互联结构。通过优化第一区域的通孔密度与半导体衬底上通孔的平均密度的关系,防止研磨后的表面金属的残留。

一种硅通孔互连的制作工艺、由此形成的硅通孔互连结构及其应用.pdf

本发明涉及一种硅通孔互连的制作工艺,包括以下步骤:S1,在硅圆片的盲孔中形成多晶硅填充结构,在多晶硅填充结构的第一表面形成阻挡层结构;S2,减薄该硅圆片,使得该盲孔形成为硅通孔结构;S3,在多晶硅填充结构的与第一表面相对的第二表面形成金属电极结构;S4,在金属电极结构上形成金凸点;S5,加热硅圆片,使得金与多晶硅填充结构在硅通孔结构中形成金硅合金结构。本发明还涉及一种由此形成的硅通孔互连结构。本发明又涉及一种硅通孔互连结构的应用。根据本发明的硅通孔互连的制作工艺、由此形成的硅通孔互连结构及其应用,结合了多

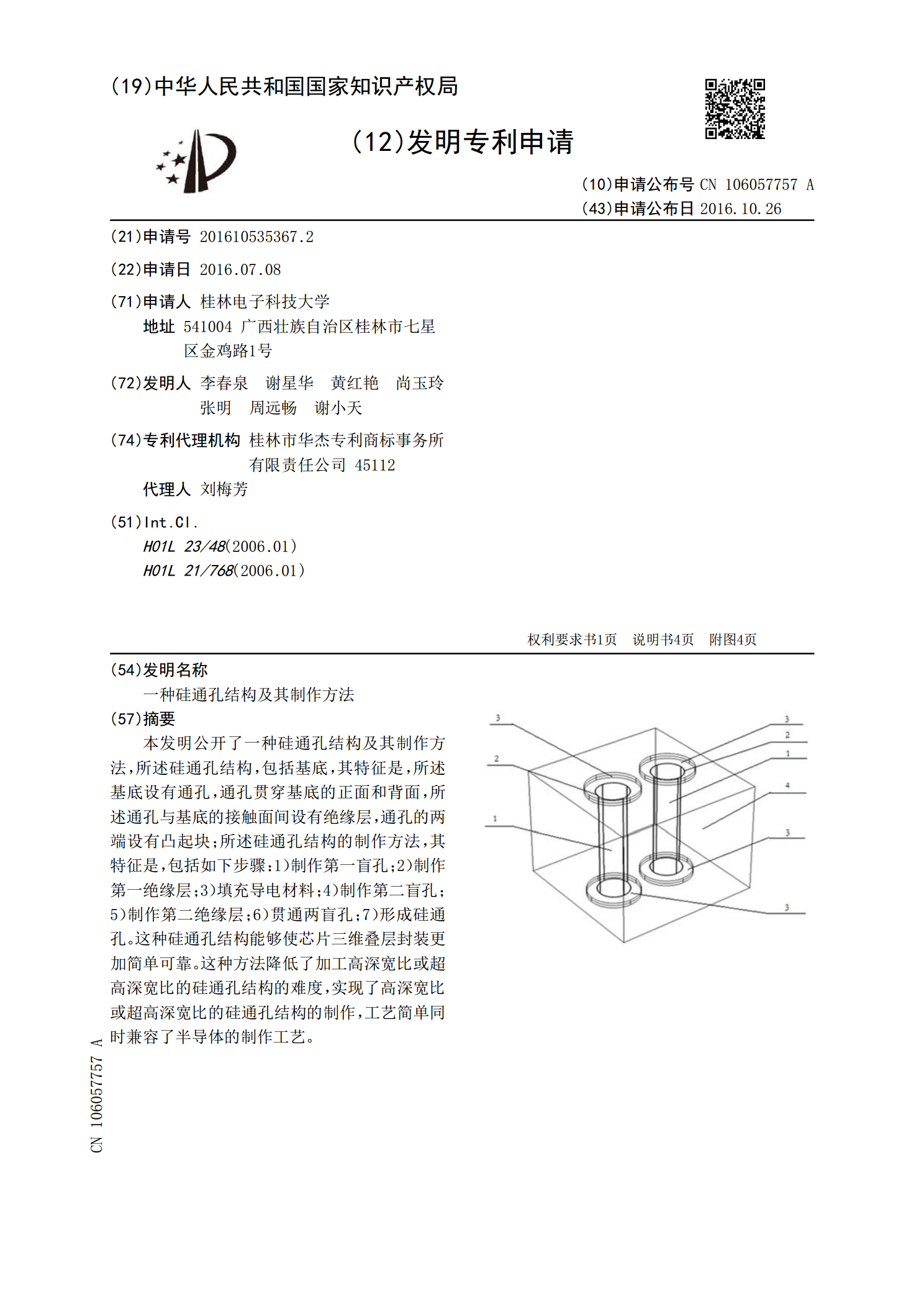

一种硅通孔结构及其制作方法.pdf

本发明公开了一种硅通孔结构及其制作方法,所述硅通孔结构,包括基底,其特征是,所述基底设有通孔,通孔贯穿基底的正面和背面,所述通孔与基底的接触面间设有绝缘层,通孔的两端设有凸起块;所述硅通孔结构的制作方法,其特征是,包括如下步骤:1)制作第一盲孔;2)制作第一绝缘层;3)填充导电材料;4)制作第二盲孔;5)制作第二绝缘层;6)贯通两盲孔;7)形成硅通孔。这种硅通孔结构能够使芯片三维叠层封装更加简单可靠。这种方法降低了加工高深宽比或超高深宽比的硅通孔结构的难度,实现了高深宽比或超高深宽比的硅通孔结构的制作,工

硅通孔的形成方法.pdf

本发明提供一种硅通孔的形成方法,包括:提供衬底;在所述衬底上形成通孔;在所述通孔中填充金属层;进行第一平坦化处理,去除衬底上方的金属层,保留通孔中的金属层;在所述衬底和金属层上覆盖应力层,所述应力层用于提供压应力;对所述金属层进行再结晶处理;进行第二平坦化处理,去除衬底上方的应力层。其中,在第一平坦化处理之后,对所述金属层进行再结晶处理之前,在所述衬底和金属层上覆盖应力层,所述应力层能够提供压应力,提高金属原子向金属层表面扩散所需要的能量,从而降低金属原子向金属层表面扩散的扩散率,进而降低金属层内的空洞率