基于FPGA的声学多普勒流速剖面仪信号处理系统.pdf

一吃****新冬

亲,该文档总共11页,到这已经超出免费预览范围,如果喜欢就直接下载吧~

相关资料

基于FPGA的声学多普勒流速剖面仪信号处理系统.pdf

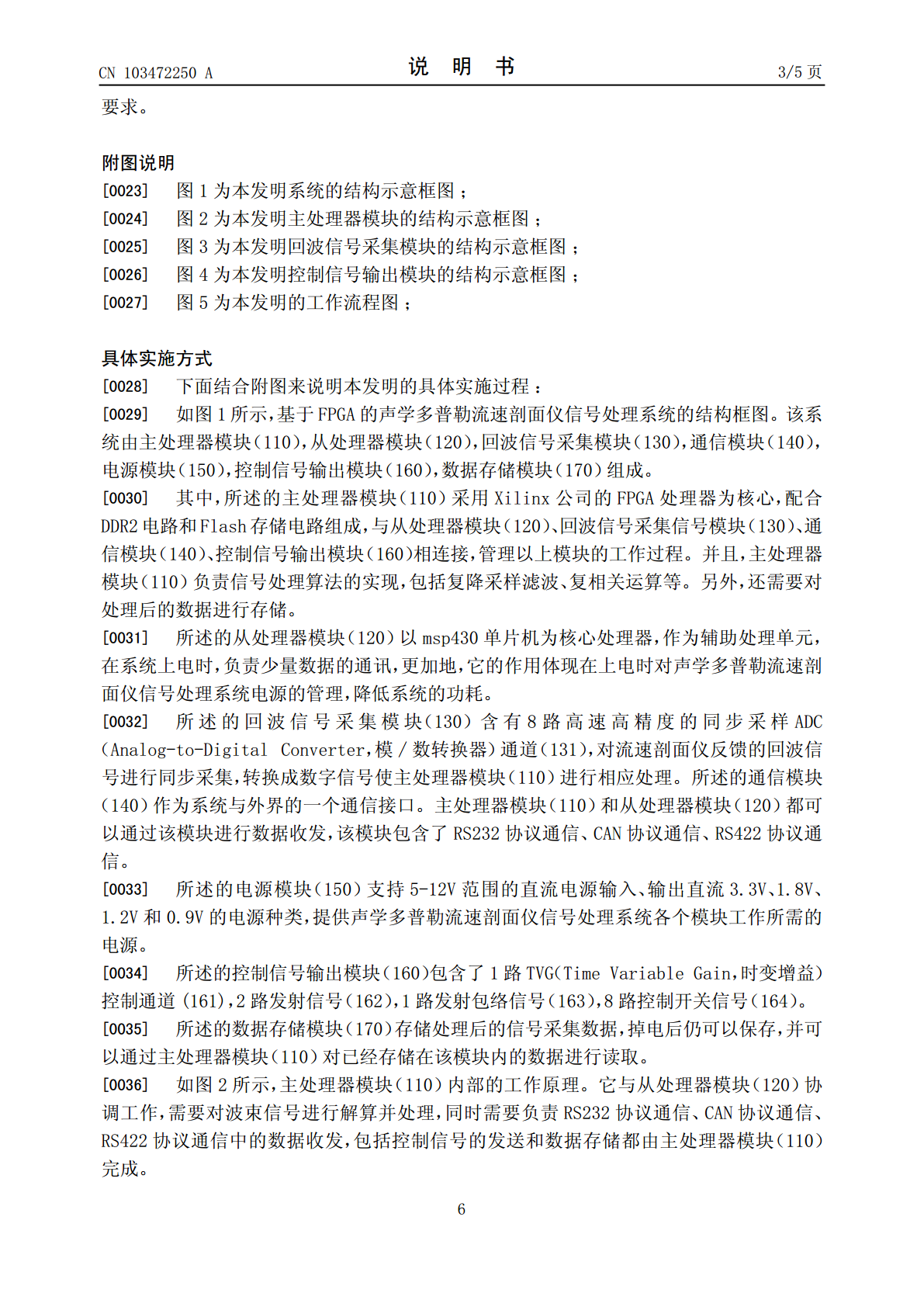

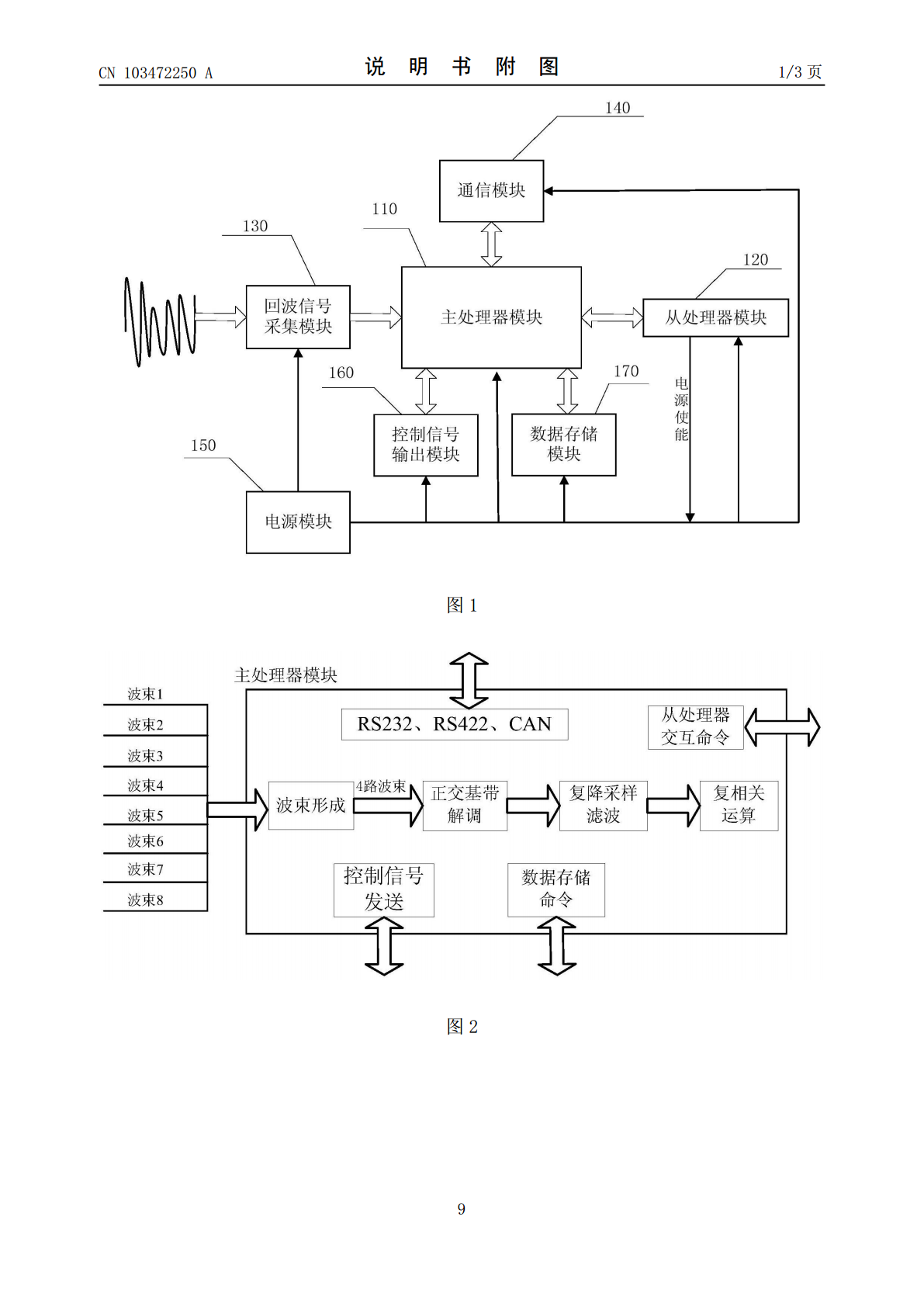

本发明公开了基于FPGA的声学多普勒流速剖面仪信号处理系统,包括:主处理器模块,从处理器模块,回波信号采集模块,通信模块,电源模块,控制信号输出模块,数据存储模块。回波信号采集模块对流速剖面仪反馈的回波信号进行同步采集,将采样后的信号送给主处理器模块。主处理器模块负责信号处理算法的实现,包括复降采样滤波、复相关运算等。另外,还需要对处理后的数据进行存储。处理后的数据存储在数据存储模块中。从处理器模块作为辅助处理单元,对系统功耗和部分数据通信管理。通信模块完成了与外部的数据收发。本发明针对流速剖面仪信号处理

基于FPGA的声学多普勒流速剖面仪信号处理方法及系统.pdf

一种基于FPGA的声学多普勒流速剖面仪信号处理方法,包括以下步骤:步骤一,系统初始化;步骤二,发射脉冲信号,结束后采集波束输出信号,将数字信号存入DDR2存储器;步骤三,从DDR2存储器中读取波束数字信号数据,做正交基带调制处理、复降采样滤波处理,将结果存入DDR2存储器中;步骤四,从DDR2存储器中读取复降采样滤波之后的数据进行复相关运算;步骤五,低速AD电路采集温度、压力等信号,计算出当前水体中的声速,然后读取复相关处理后的数据计算流速和回波能量;步骤六,将结果数据储存在TF卡中,并发送给上位机处理、

声学多普勒剖面流速仪.doc

声学多普勒流速剖面仪第一章说明谢谢您购买Nortek.Aquadopp剖面仪。这个剖面仪设计的思想是提供给你们多年的安全和可靠的服务。这个剖面仪在水中采用声学多普勒效应测量水流剖面。它的设计是为定位应用程序,并且可以配置在底部、钻塔停泊处、浮标上或其他任何固定结构。这是一个完整工具,包括所有部件,这些部件需要带有数据存储在内部数字记录仪的自包含的配置。典型的应用包括海岸研究、在线监视和在河流、湖泊、海峡的科学研究。Aquadopp剖面仪有多种多样的可靠的配置头。Aquadop是NortekAs中一个已经注

声学多普勒流速剖面仪.pptx

声学(shēngxué)多普勒流速剖面仪多种频率换能器的配置新结构外形采样单元大小、工作频率、采样频率、工作模式的自动转换(zhuǎnhuàn)和信号处理独有的垂直波束8G内存,内部计算流量,数据不会丢失RiverSurveyprLive!软件用于计算机手机高分辨率RTKGPS选项多种通讯蓝牙无线电台手机新的走航船体多种频率(pínlǜ)换能器的配置1自动转换(zhuǎnhuàn)功能2垂直(chuízhí)声波探头3垂直波束(bōshù)实测水深(红色轨迹)内部流量(liúliàng)计算4多版本(bǎ

声学多普勒剖面流速仪的检测方法.pdf

本发明公开了一种声学多普勒剖面流速仪的检测方法,包括以下步骤:在水池底部布设有微纳米气泡曝气头;通过微纳米气泡发生装置在水池内产生微纳米气泡;持续产生微纳米气泡一段时间后停止微纳米气泡产生,并等待一段时间;牵引检定车沿轨道匀速行进,检定车上的流速仪采集数据。本发明通过在水池底部均匀设置的微纳米气泡曝气头能够在静水池中产生均匀的微纳米气泡,令水体中具备足够浓度的反射物质,这些反射物质浓度均匀,显著提高了静水的反射强度,满足声学多普勒剖面流速仪检定对水体的要求。因此,声学多普勒剖面流速仪能够获得仪器检定需要的