一种LFMCW雷达目标回波信号模拟方法.pdf

觅松****哥哥

亲,该文档总共16页,到这已经超出免费预览范围,如果喜欢就直接下载吧~

相关资料

一种LFMCW雷达目标回波信号模拟方法.pdf

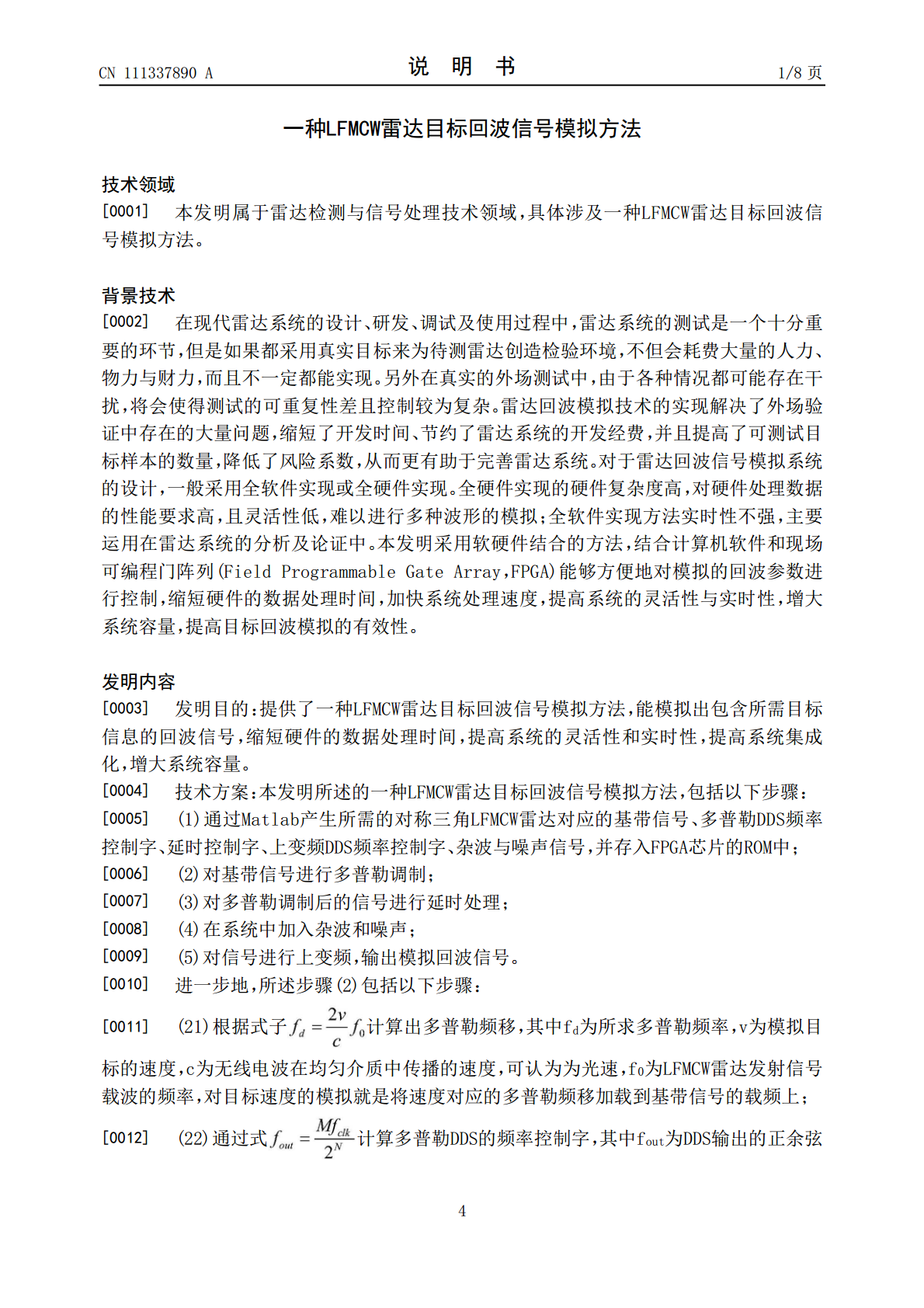

本发明公开了一种LFMCW雷达目标回波信号模拟方法,首先,通过Matlab产生所需的对称三角LFMCW雷达对应的基带信号、多普勒DDS频率控制字、延时控制字、上变频DDS频率控制字、杂波与噪声信号,并存入FPGA芯片的ROM中;其次,对基带信号进行多普勒调制;然后,对多普勒调制后的信号进行延时处理;在系统中加入杂波和噪声;最后,对信号进行上变频,输出模拟回波信号。本发明采用软硬结合的方法,使得控制更加灵活,系统更加集成化,能更方便地产生符合要求的回波信号。

一种相控阵雷达目标回波信号的实时模拟方法.docx

一种相控阵雷达目标回波信号的实时模拟方法标题:一种相控阵雷达目标回波信号的实时模拟方法摘要:相控阵雷达是一种重要的无源探测技术,其能够通过调控阵列单元之间的相位差来实现波束的扫描和指向,实现目标的快速探测和跟踪。在相控阵雷达的研究和应用过程中,需要对目标回波信号进行实时模拟,以评估和验证算法的性能和效果。本文提出一种基于数学模型的相控阵雷达目标回波信号实时模拟方法,包括回波信号生成、信道模拟和数据处理三个步骤。实验结果表明,该方法能够有效模拟相控阵雷达的目标回波信号,并且具有良好的实时性能。关键词:相控阵

一种相控阵雷达目标回波信号模拟系统.pdf

本发明公开了一种相控阵雷达目标回波信号模拟系统,模拟系统包括射频信号下变频单、射频信号上变频单元、中频信号处理单元等。系统工作时,如果接收到雷达发射信号,则采集雷达中频信号,进行信号测量,存储雷达信号并叠加延时、多普勒信息,生成相参导引的目标回波信号和高度回波信号;如果主动产生信号,则根据生成信号类型,将基带SAR回波数据数字上变频为SAR中频回波信号,或主动产生线性调频信号,或主动产生中频点频连续被信号。本发明能够在单台设备中综合一体化地模拟SAR回波、相参导引信号等多种目标回波信号形式,监测并显示雷达

宽带雷达目标回波信号检测方法研究.pptx

添加副标题目录PART01PART02宽带雷达概述目标回波信号检测的意义论文研究目的和意义PART03宽带雷达信号特性目标回波信号特性干扰和噪声特性PART04常规检测方法基于滤波器组的目标回波信号检测方法基于压缩感知的目标回波信号检测方法PART05实验设置和数据来源实验结果展示结果分析和讨论PART06研究结论研究不足与展望PART07感谢您的观看

雷达目标及背景回波信号模拟的开题报告.docx

雷达目标及背景回波信号模拟的开题报告一、研究背景随着现代科技的飞速发展,雷达技术在国民经济和国防建设中的应用越来越广泛。雷达的作用是利用电磁波探测目标并获得有关目标的信息,因而在侦察、火力打击、伴随、导航、航空管制等领域中有广泛而重要的应用。在雷达技术中,目标及背景回波信号模拟是非常重要的一环。二、研究目的本项目旨在探究如何通过仿真方法模拟雷达目标及背景回波信号,为雷达技术的发展和应用提供更好的支持和保障。三、研究内容1.理论研究通过分析雷达目标及背景回波信号的特征,对雷达目标及背景回波信号进行建模和仿真