多晶硅叠层、双栅以及半导体材料叠层刻蚀方法.pdf

安双****文章

亲,该文档总共13页,到这已经超出免费预览范围,如果喜欢就直接下载吧~

相关资料

多晶硅叠层、双栅以及半导体材料叠层刻蚀方法.pdf

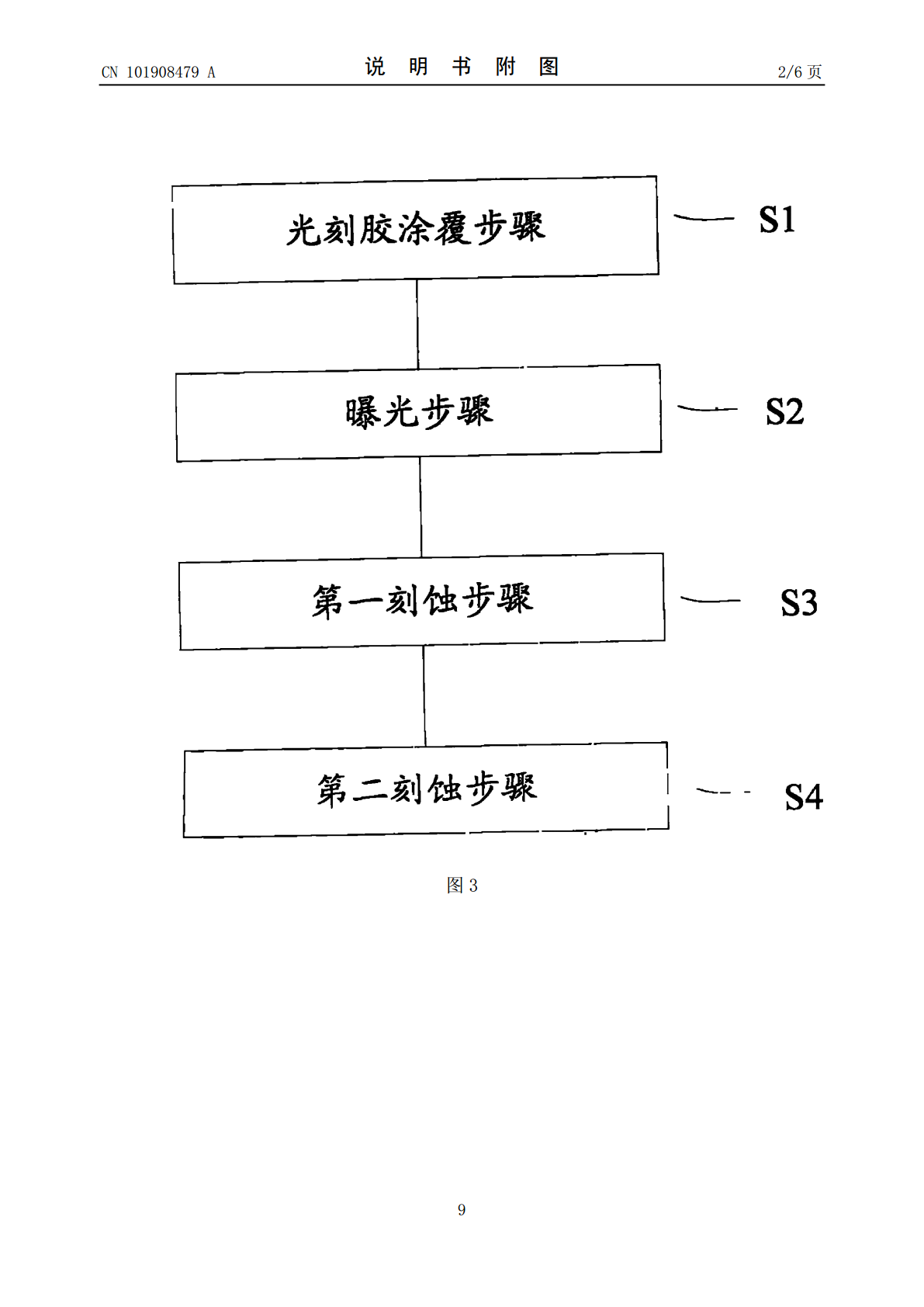

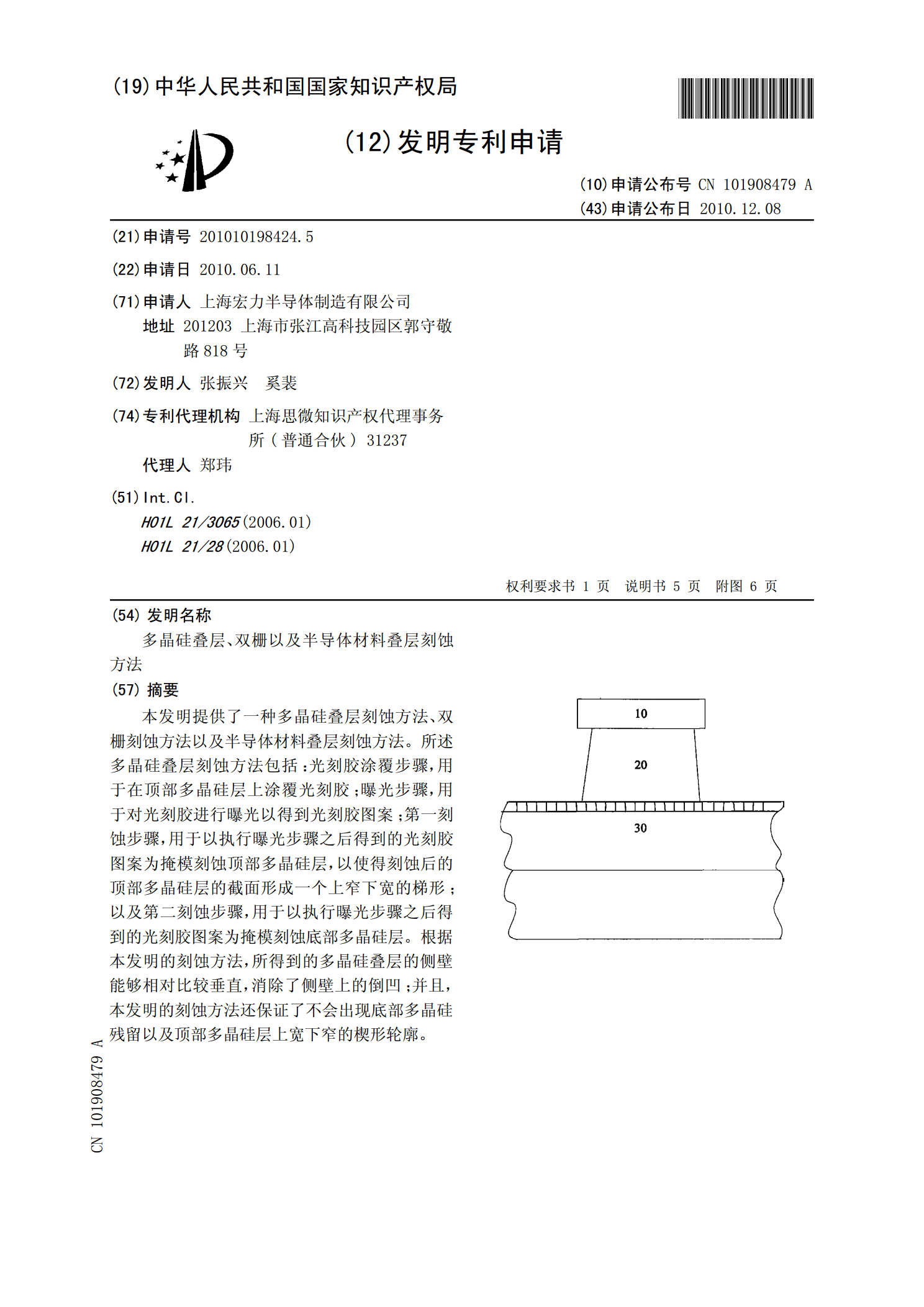

本发明提供了一种多晶硅叠层刻蚀方法、双栅刻蚀方法以及半导体材料叠层刻蚀方法。所述多晶硅叠层刻蚀方法包括:光刻胶涂覆步骤,用于在顶部多晶硅层上涂覆光刻胶;曝光步骤,用于对光刻胶进行曝光以得到光刻胶图案;第一刻蚀步骤,用于以执行曝光步骤之后得到的光刻胶图案为掩模刻蚀顶部多晶硅层,以使得刻蚀后的顶部多晶硅层的截面形成一个上窄下宽的梯形;以及第二刻蚀步骤,用于以执行曝光步骤之后得到的光刻胶图案为掩模刻蚀底部多晶硅层。根据本发明的刻蚀方法,所得到的多晶硅叠层的侧壁能够相对比较垂直,消除了侧壁上的倒凹;并且,本发明的

金属栅层/高K栅介质层的叠层结构刻蚀后的清洗方法.pdf

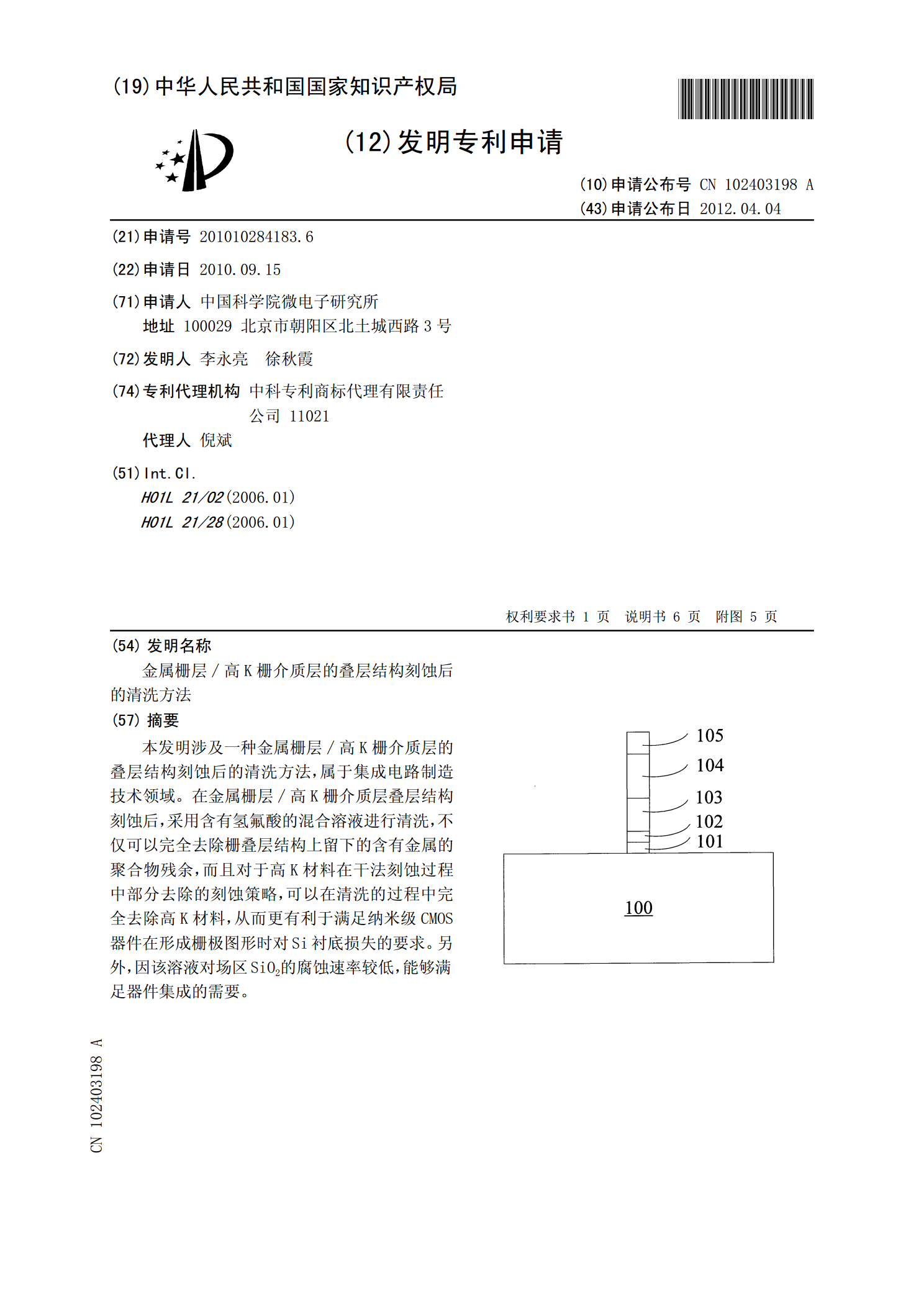

本发明涉及一种金属栅层/高K栅介质层的叠层结构刻蚀后的清洗方法,属于集成电路制造技术领域。在金属栅层/高K栅介质层叠层结构刻蚀后,采用含有氢氟酸的混合溶液进行清洗,不仅可以完全去除栅叠层结构上留下的含有金属的聚合物残余,而且对于高K材料在干法刻蚀过程中部分去除的刻蚀策略,可以在清洗的过程中完全去除高K材料,从而更有利于满足纳米级CMOS器件在形成栅极图形时对Si衬底损失的要求。另外,因该溶液对场区SiO2的腐蚀速率较低,能够满足器件集成的需要。

磁性材料、使用其的叠层磁性材料、叠层组件和叠层磁芯以及磁性材料的制造方法.pdf

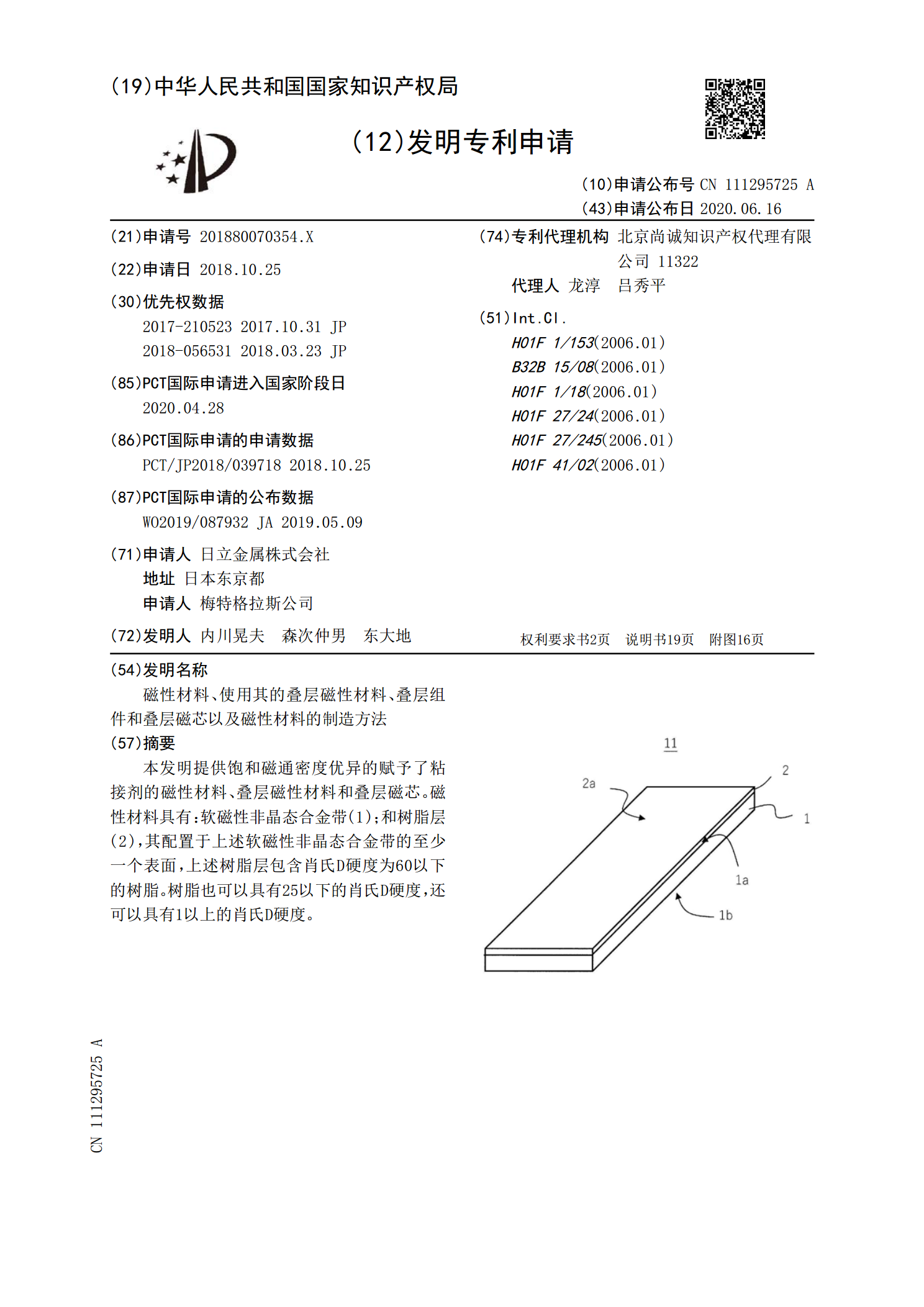

本发明提供饱和磁通密度优异的赋予了粘接剂的磁性材料、叠层磁性材料和叠层磁芯。磁性材料具有:软磁性非晶态合金带(1);和树脂层(2),其配置于上述软磁性非晶态合金带的至少一个表面,上述树脂层包含肖氏D硬度为60以下的树脂。树脂也可以具有25以下的肖氏D硬度,还可以具有1以上的肖氏D硬度。

叠层电池及叠层电池制备方法.pdf

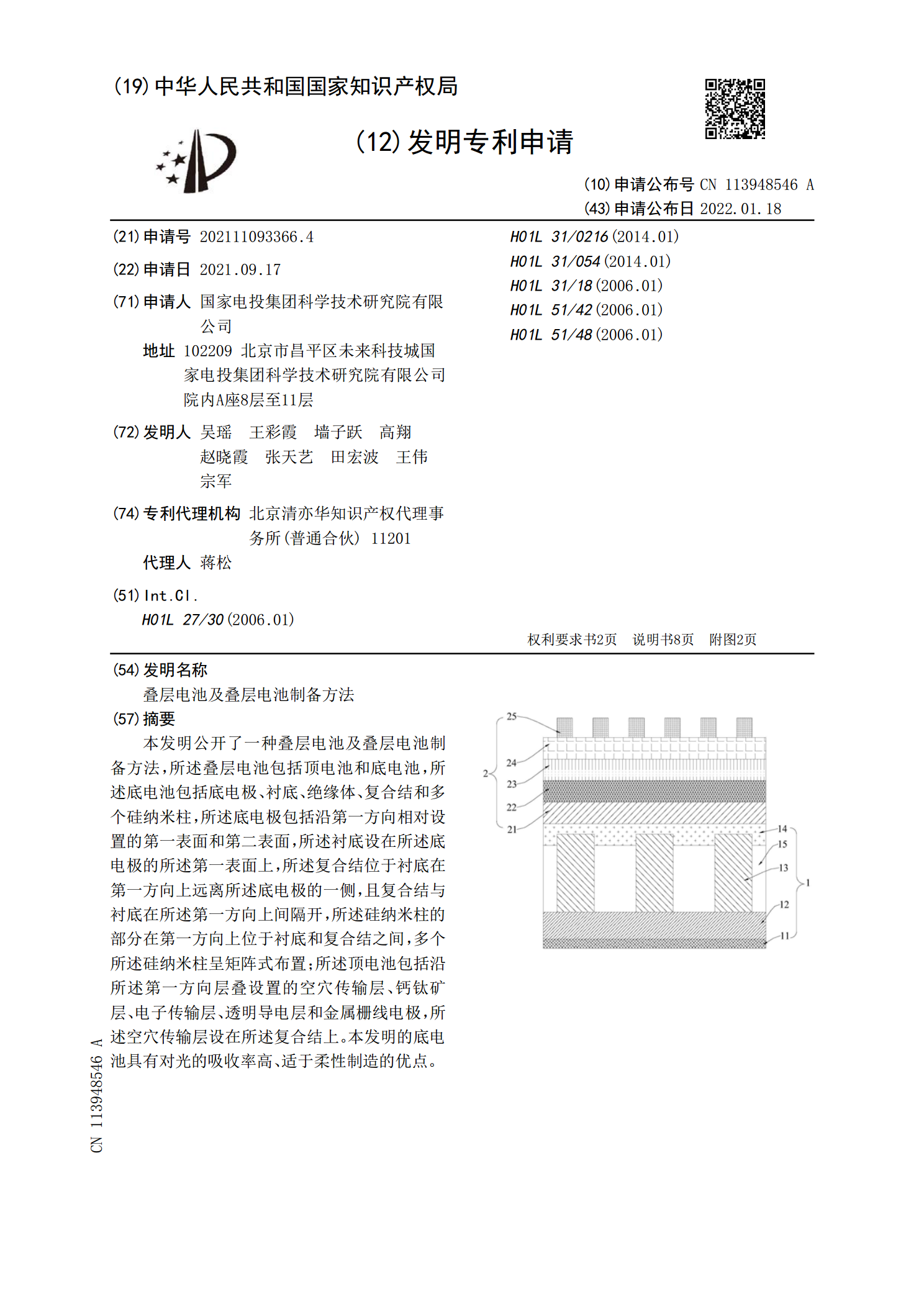

本发明公开了一种叠层电池及叠层电池制备方法,所述叠层电池包括顶电池和底电池,所述底电池包括底电极、衬底、绝缘体、复合结和多个硅纳米柱,所述底电极包括沿第一方向相对设置的第一表面和第二表面,所述衬底设在所述底电极的所述第一表面上,所述复合结位于衬底在第一方向上远离所述底电极的一侧,且复合结与衬底在所述第一方向上间隔开,所述硅纳米柱的部分在第一方向上位于衬底和复合结之间,多个所述硅纳米柱呈矩阵式布置;所述顶电池包括沿所述第一方向层叠设置的空穴传输层、钙钛矿层、电子传输层、透明导电层和金属栅线电极,所述空穴传输

高K栅介质/金属栅叠层栅结构刻蚀后聚合物去除方法.pdf

一种高K栅介质/金属栅叠层栅结构刻蚀后聚合物去除方法,主要步骤如下:1)在器件隔离形成后,在硅衬底上依次形成界面SiO2/高K栅介质/金属栅/多晶硅/硬掩膜叠层栅结构;2)光刻形成胶图形;3)刻蚀叠层栅结构;4)将步骤3的产品浸没于腐蚀溶液中去除聚合物,腐蚀溶液配比为氢氟酸0.2~1%,盐酸5~15%,其余为水。本发明采用氢氟酸(HF)/盐酸(HCl)混合的水溶液化学湿法腐蚀,在室温下就能去净叠栅两侧及硅衬底表面残留的聚合物,不仅保持陡直的叠栅刻蚀剖面,并对硅衬底不造成损伤,与CMOS工艺兼容性好,成本低