一种分组密码加解密方法.pdf

子璇****君淑

亲,该文档总共17页,到这已经超出免费预览范围,如果喜欢就直接下载吧~

相关资料

一种分组密码加解密方法.pdf

本发明提供了一种分组密码加解密方法,属于数据加密解密领域。本发明算法设计了一种对称的加密结构,尤其是本发明的S盒设计能配置加密需要的S变换和解密需要的S逆变换而无需增加额外的电路资源,利于加解密一体的硬件电路实现,比AES加解密一体的电路需要更少的面积资源。本发明算法复杂的S盒构造可以抵抗现有已知的攻击方法。在较少轮数(3轮)加密情况下可以提供很高的加密速度,并且利用相同的加解密硬件可以用同样的速度进行解密。该算法特别适合专用ASIC实现,可以实现加解密专用算法的专用集成电路芯片。也可用于FPGA上的IP

一种分组加解密方法和装置.pdf

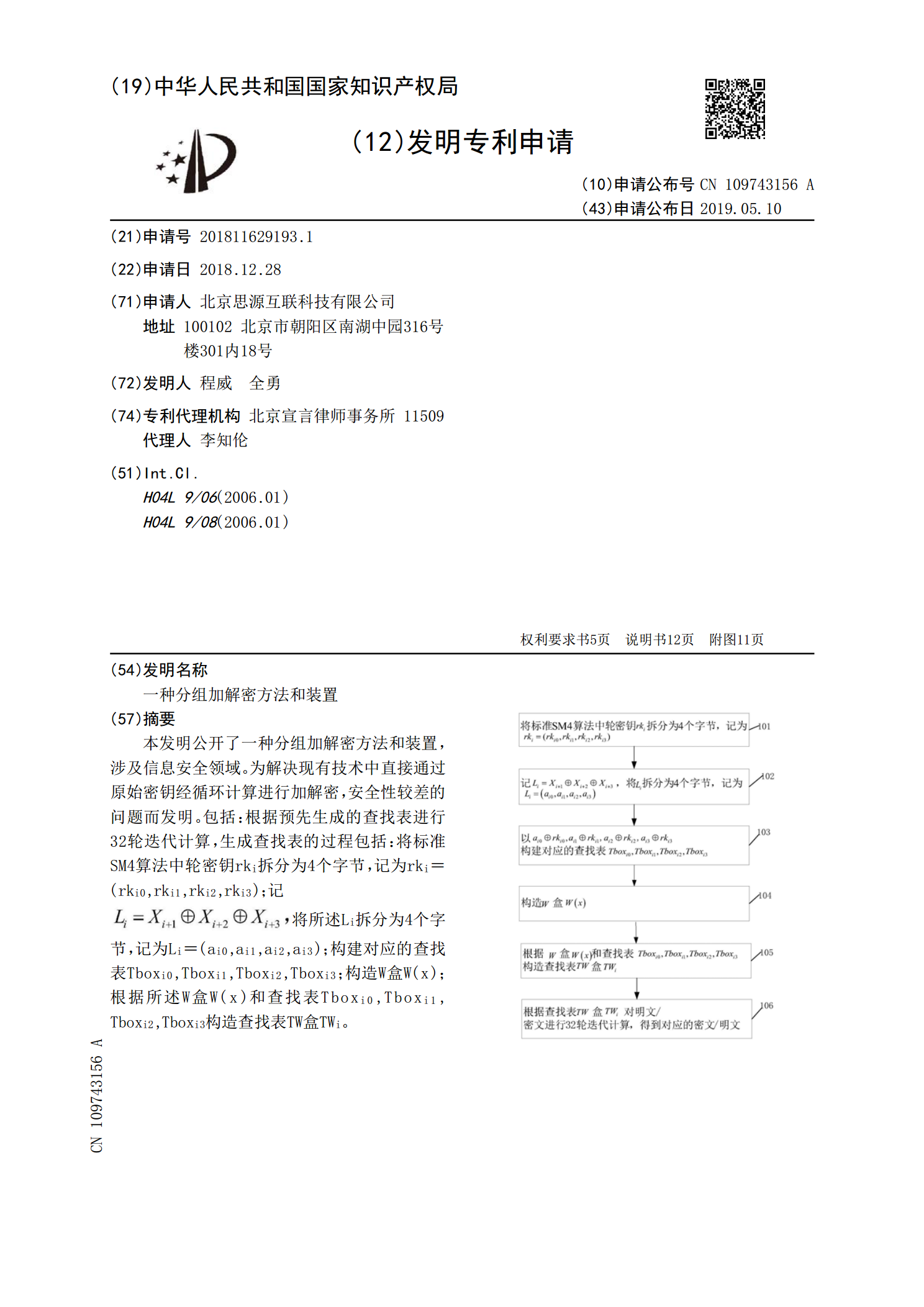

本发明公开了一种分组加解密方法和装置,涉及信息安全领域。为解决现有技术中直接通过原始密钥经循环计算进行加解密,安全性较差的问题而发明。包括:根据预先生成的查找表进行32轮迭代计算,生成查找表的过程包括:将标准SM4算法中轮密钥rk

一种实现分组密码加密的密钥扩展方法.pdf

本发明提供了一种分组密码算法的密钥扩展方法,用于生成分组密码算法的各轮子密钥。本发明提供的方法主要是通过迭代函数计算生成子密钥,该迭代函数由非线性运算,常数运算和循环一位运算构成。通过本发明提供的方法,可以高效便利地生成子密钥,有效减少存储空间,具有较一般商用分组密码算法更高的实现速度,可以满足实时加密和解密的要求,同时,该算法具有比较高的安全性。

一种分组密码FBC的实现方法及装置.pdf

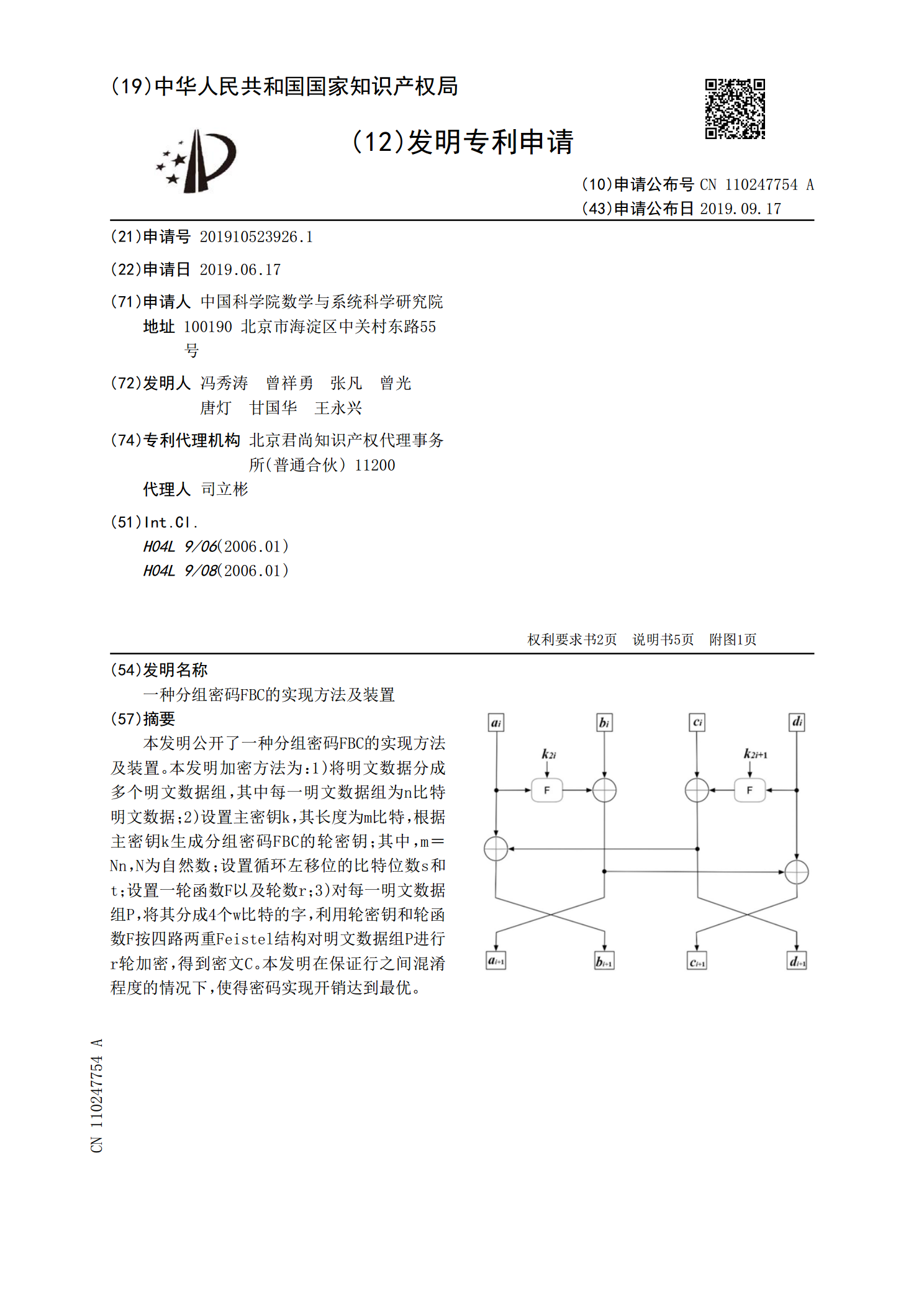

本发明公开了一种分组密码FBC的实现方法及装置。本发明加密方法为:1)将明文数据分成多个明文数据组,其中每一明文数据组为n比特明文数据;2)设置主密钥k,其长度为m比特,根据主密钥k生成分组密码FBC的轮密钥;其中,m=Nn,N为自然数;设置循环左移位的比特位数s和t;设置一轮函数F以及轮数r;3)对每一明文数据组P,将其分成4个w比特的字,利用轮密钥和轮函数F按四路两重Feistel结构对明文数据组P进行r轮加密,得到密文C。本发明在保证行之间混淆程度的情况下,使得密码实现开销达到最优。

一种新型轻量级分组密码CORL的实现方法.pdf

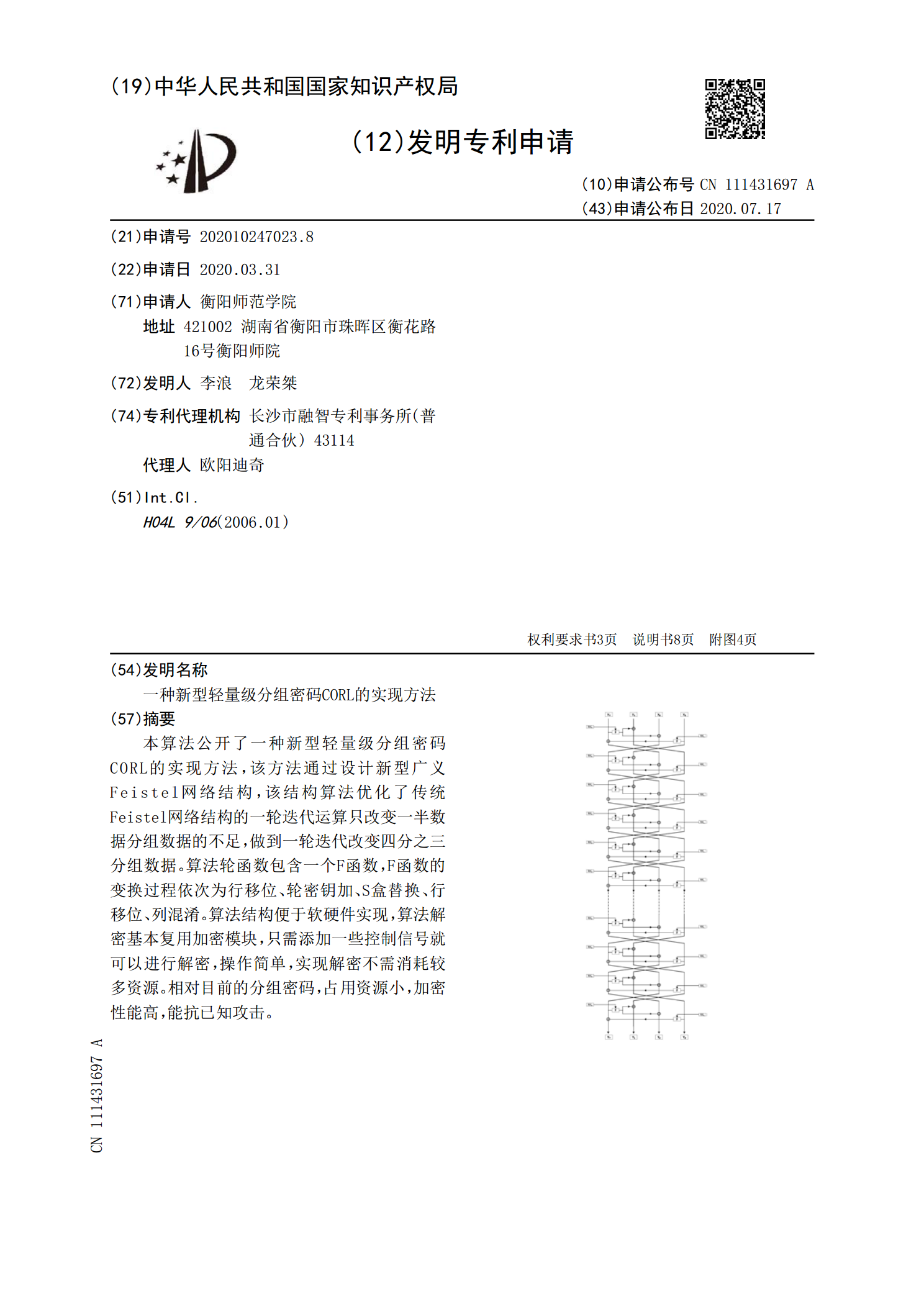

本算法公开了一种新型轻量级分组密码CORL的实现方法,该方法通过设计新型广义Feistel网络结构,该结构算法优化了传统Feistel网络结构的一轮迭代运算只改变一半数据分组数据的不足,做到一轮迭代改变四分之三分组数据。算法轮函数包含一个F函数,F函数的变换过程依次为行移位、轮密钥加、S盒替换、行移位、列混淆。算法结构便于软硬件实现,算法解密基本复用加密模块,只需添加一些控制信号就可以进行解密,操作简单,实现解密不需消耗较多资源。相对目前的分组密码,占用资源小,加密性能高,能抗已知攻击。