单片机输入输出口.ppt

YY****。。

亲,该文档总共19页,到这已经超出免费预览范围,如果喜欢就直接下载吧~

相关资料

单片机实验 IO口的输入输出实验.doc

实验二I/O口输入、输出实验一、实验目的1.学习I/O口的使用方法。2.学习延时子程序、查表程序的编写和使用。二、参考程序框图开始读入P1口值置计数初值=0P1口置1将读入的值输出到P0P1=0FFH?YN输入值右移1位到CyCy=0?N计数值+1Y以计数值查段码表段码输出到P2开始延时设置初始值数据输出左移一位三、程序设计1、P0口循环点亮程序ORG0030HSTART:MOVP2,#00H;//消影MOVA,#01H;//LOOP:MOVP2,A;//点亮一个led灯ACALLDELAY;//延时50

单片机P1口输入输出实验.pptx

单片机I/O口输入输出试验(或单片机数字量输入输出试验)单片机P1口输入输出试验2、试验要求(1)、2)为必做,3)为选做)3)P1口作输出口,接8只发光二极管LED1-LED8(其输出端为低电平时发光二极管点亮),编写程序。状态1:控制系统通电或复位后,8个LED发光二极管依次从左到右开始逐一点亮;状态2:8个LED发光二极管全亮后,从右向左LED发光二极管再逐一熄灭;状态3:8个LED发光二极管全灭后,从左右两边开始同步点亮LED发光二极管,全亮后,8个LED发光二极管再明暗一起闪烁2次?单片机P1口

单片机输入输出实验.pptx

会计学实验要求:实验目的:实验说明:原理图:modeequ082h;方式0,PA,PC输出,PB输入PortAequ8000h;PortAPortBequ8001h;PortBPortCequ8002h;PortCCAddrequ8003h;控制字地址codesegmentassumecs:codestartprocnearStart:moval,modemovdx,CAddroutdx,al;输出控制字;实验1:PortA输出实验2:PortB输入PortA输出;movdx,PortBinal,dx;读

单片机输入输出端口.pptx

会计学2.1单片机时序简介2.1单片机时序简介2.1单片机时序简介单机器周期指令的时序双机器周期指令的时序2.2单片机外部引脚简介(以40引脚为例)2.2单片机外部引脚简介ALE/PROG(30脚):地址锁存信号输出端当外接存储器(ROM或RAM)时,ALE的输出用于锁存地址的低8位,一般ALE接锁存器的EN端当没有外部存储器时,ALE端可用于脉冲信号输出,且频率是石英振荡频率的1/6。在烧写EPROM时,该引脚用作编程脉冲PROG的输入端P0口(39~32脚):P0.0~P0.7统称为P0口。P0口的每

单片机输入输出口.ppt

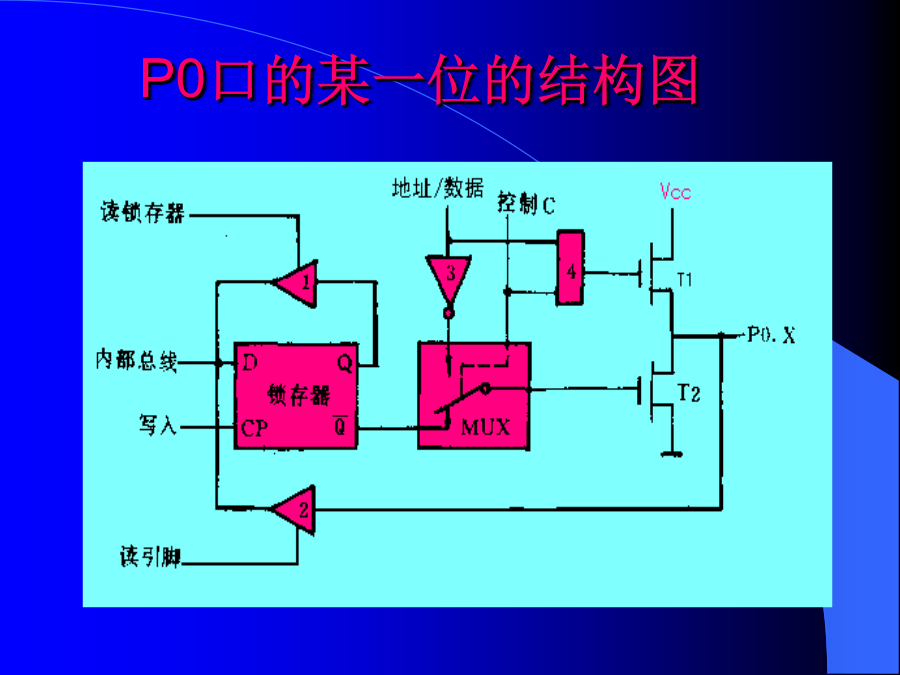

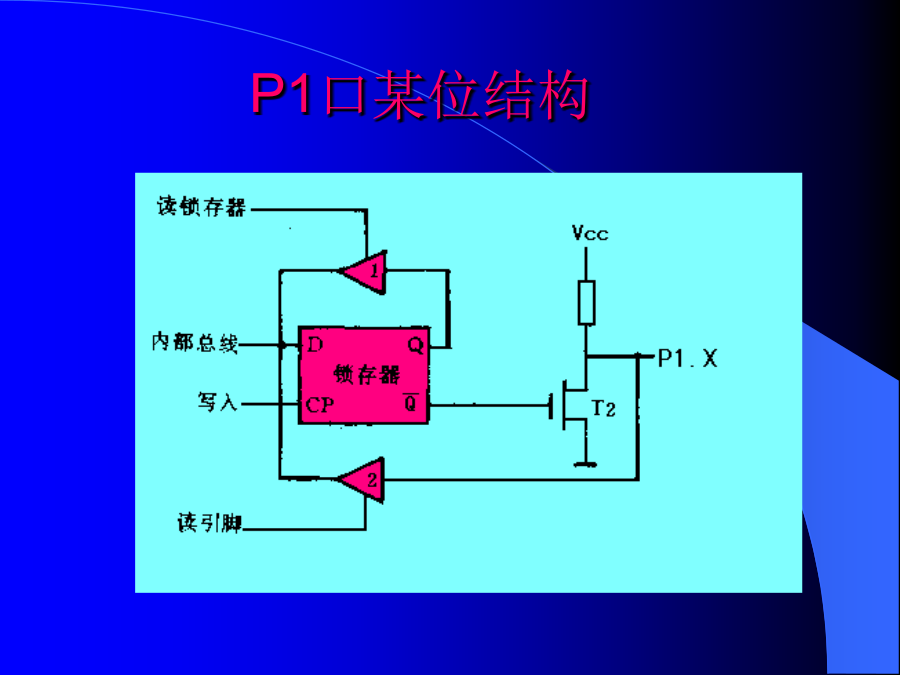

8051输入/输出端口结构(慨述)一、P0口的结构:P0口的某一位的结构图(一)P0口作为一般I/O口使用1、P0口用作输出口2.P0口作输入口(二)P0口作为地址/数据总线使用总结:二、P1口P1口某位结构三、P2口某位结构四、P3口的结构P3各口线的第二功能表P3口的位结构编程时,不必事先由软件设置P3门为第一功能(通用I/O口)还是第二功能。●当CPU对P3口进行SFR寻址(位或字节)访问时,由内部硬件自动将第二功能输出线W置1,这时P3口为通用I/O口;●当CPU不把P3口作为SFR寻址(位或字节