半导体器件物理 chapter4 集成电路制造工艺.ppt

YY****。。

亲,该文档总共34页,到这已经超出免费预览范围,如果喜欢就直接下载吧~

相关资料

半导体器件物理 Chapter4 集成电路制造工艺.ppt

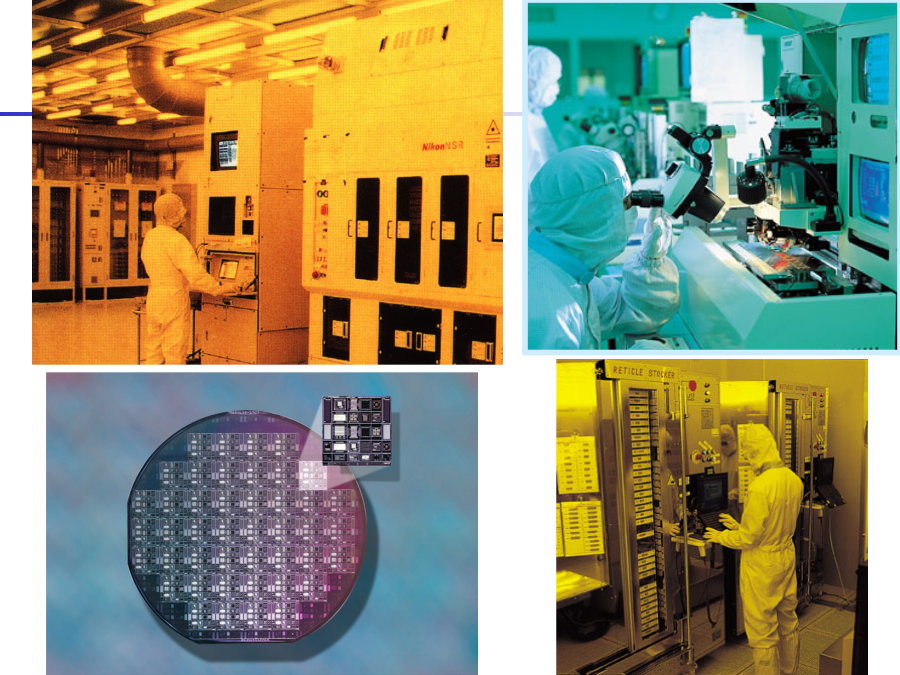

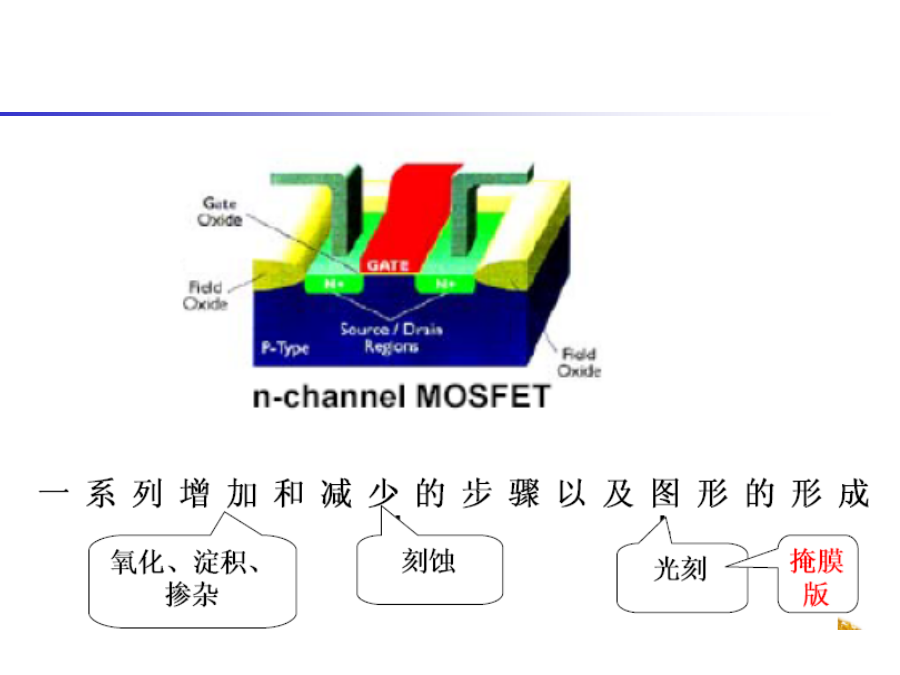

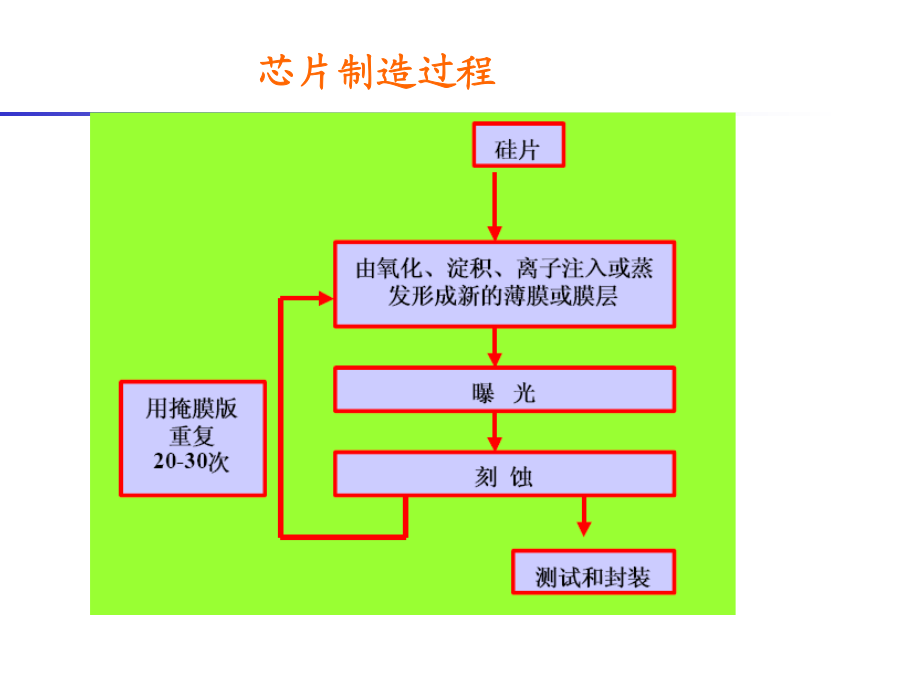

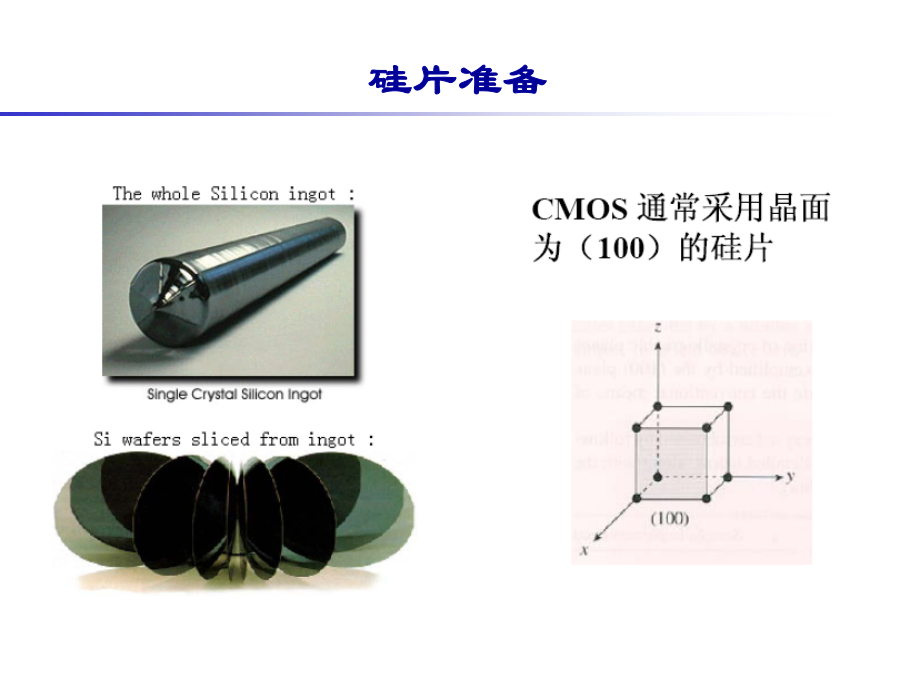

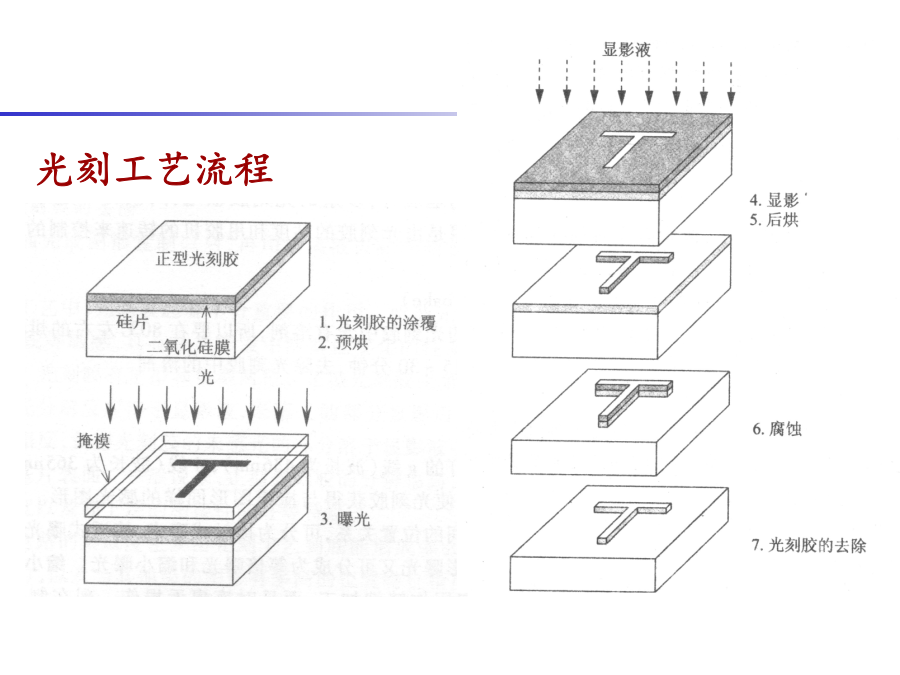

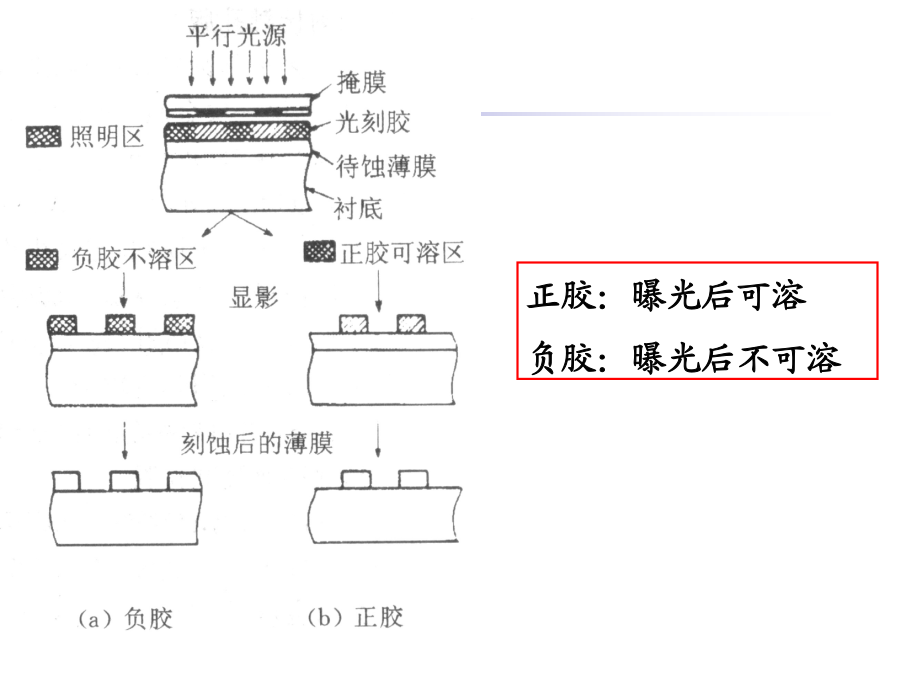

第四章集成电路制造工艺芯片制造过程图形转换:将设计在掩膜版(类似于照相底片)上的图形转移到衬底上。掺杂:根据设计的需要,将各种杂质掺杂在需要的位置上,形成晶体管、接触等。制膜:制作各种材料的薄膜。硅片准备光刻(Lithography)光刻工艺流程光刻三要素:光刻胶、掩膜版和光刻机–光刻胶又叫光致抗蚀剂,它是由光敏化合物、基体树脂和有机溶剂等混合而成的胶状液体。–光刻胶受到特定波长光线的作用后,导致其化学结构发生变化,使光刻胶在某种特定溶液中的溶解特性改变。正胶(曝光后可溶):分辨率高,在超大规模集成电路工

半导体器件物理 Chapter4 集成电路制造工艺.pptx

第四章集成电路制造工艺芯片制造过程图形转换:将设计在掩膜版(类似于照相底片)上的图形转移到衬底上。掺杂:根据设计的需要,将各种杂质掺杂在需要的位置上,形成晶体管、接触等。制膜:制作各种材料的薄膜。硅片准备光刻(Lithography)光刻工艺流程光刻三要素:光刻胶、掩膜版和光刻机–光刻胶又叫光致抗蚀剂,它是由光敏化合物、基体树脂和有机溶剂等混合而成的胶状液体。–光刻胶受到特定波长光线的作用后,导致其化学结构发生变化,使光刻胶在某种特定溶液中的溶解特性改变。正胶(曝光后可溶):分辨率高,在超大规模集成电路工

半导体器件物理 Chapter4 集成电路制造工艺.ppt

第四章集成电路制造工艺芯片制造过程图形转换:将设计在掩膜版(类似于照相底片)上的图形转移到衬底上。掺杂:根据设计的需要将各种杂质掺杂在需要的位置上形成晶体管、接触等。制膜:制作各种材料的薄膜。硅片准备光刻(Lithography)光刻工艺流程光刻三要素:光刻胶、掩膜版和光刻机–光刻胶又叫光致抗蚀剂它是由光敏化合物、基体树脂和有机溶剂等混合而成的胶状液体。–光刻胶受到特定波长光线的作用后导致其化学结构发生变化使光刻胶在某种特定溶液中的溶解特性改变。正胶(曝光后可溶):分辨率高在超大规模集

半导体器件物理 chapter4 集成电路制造工艺.ppt

第四章集成电路制造工艺芯片制造过程图形转换:将设计在掩膜版(类似于照相底片)上的图形转移到衬底上。掺杂:根据设计的需要,将各种杂质掺杂在需要的位置上,形成晶体管、接触等。制膜:制作各种材料的薄膜。硅片准备光刻(Lithography)光刻工艺流程光刻三要素:光刻胶、掩膜版和光刻机–光刻胶又叫光致抗蚀剂,它是由光敏化合物、基体树脂和有机溶剂等混合而成的胶状液体。–光刻胶受到特定波长光线的作用后,导致其化学结构发生变化,使光刻胶在某种特定溶液中的溶解特性改变。正胶(曝光后可溶):分辨率高,在超大规模集成电路工

半导体器件物理 Chapter4 集成电路制造工艺.ppt

第四章集成电路制造工艺芯片制造过程图形转换:将设计在掩膜版(类似于照相底片)上的图形转移到衬底上。掺杂:根据设计的需要,将各种杂质掺杂在需要的位置上,形成晶体管、接触等。制膜:制作各种材料的薄膜。硅片准备光刻(Lithography)光刻工艺流程光刻三要素:光刻胶、掩膜版和光刻机–光刻胶又叫光致抗蚀剂,它是由光敏化合物、基体树脂和有机溶剂等混合而成的胶状液体。–光刻胶受到特定波长光线的作用后,导致其化学结构发生变化,使光刻胶在某种特定溶液中的溶解特性改变。正胶(曝光后可溶):分辨率高,在超大规模集成电路工