半导体中的杂质和缺陷能级.ppt

YY****。。

亲,该文档总共34页,到这已经超出免费预览范围,如果喜欢就直接下载吧~

相关资料

半导体中的杂质和缺陷能级.docx

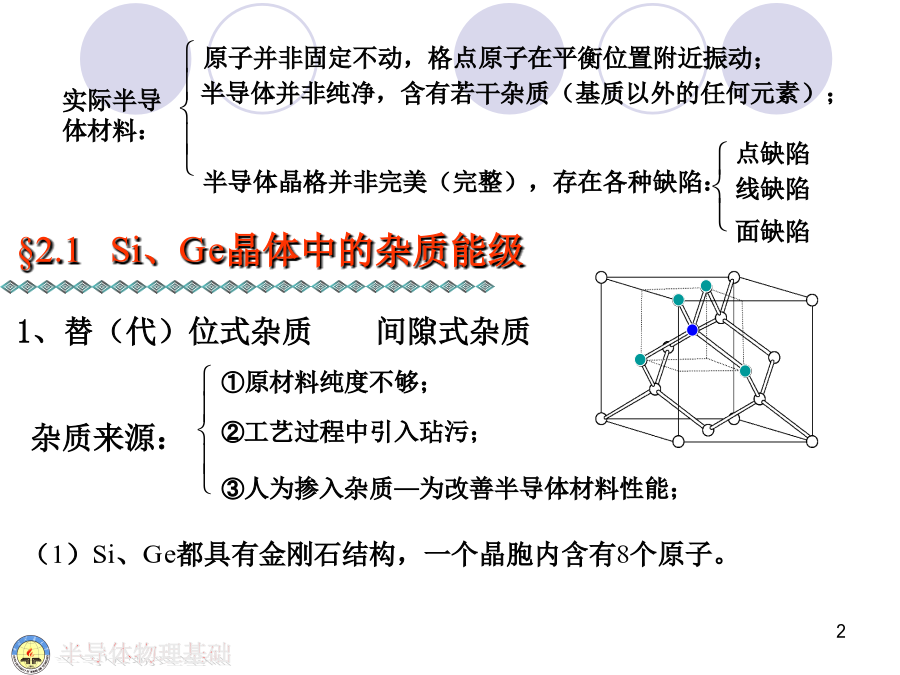

第二章半导体中杂质和缺陷能级引言1.实际半导体和理想半导体的区别理想半导体实际半导体原子不是静止在具有严格周期性的晶格的格点上,而在其平衡位置附近振动原子静止在具有严格周期性的晶格的格点上半导体不是纯净的,含有若干杂质半导体是纯净的,不含杂质晶格结构不是完整的,含若干缺陷晶格结构是完整的,不含缺陷2.杂质的种类根据杂质能级在禁带中的位置将杂质分为两种浅能级杂质:能级接近导电底Ec或价带顶Ev;深能级杂质:能级远离导带底Ec或价带顶Ev;3.缺陷的种类点缺陷,如空位、间隙原子;线缺陷,如位错;面缺陷,如层错

半导体中杂质和缺陷能级.ppt

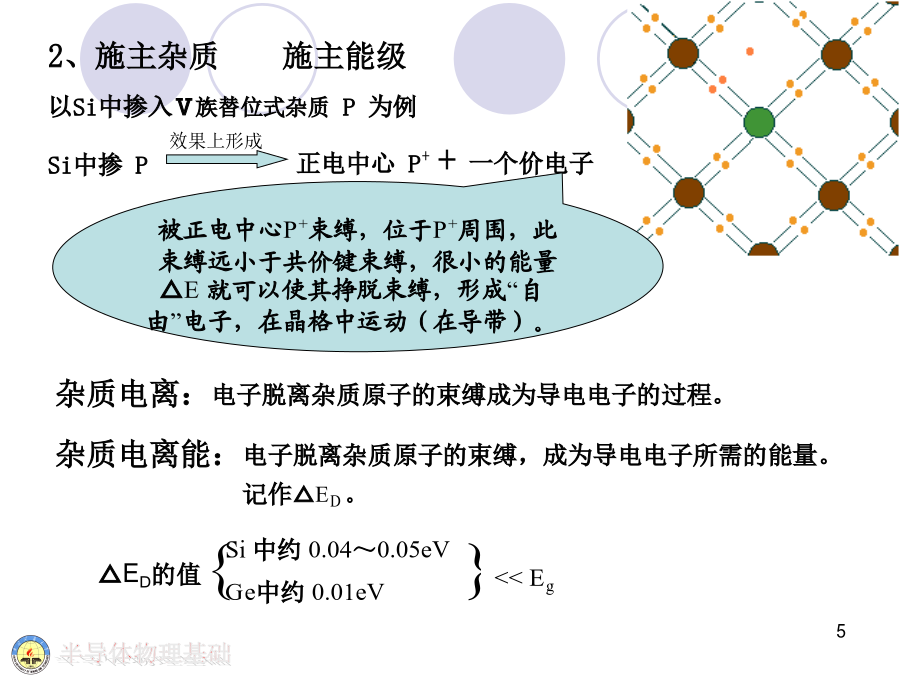

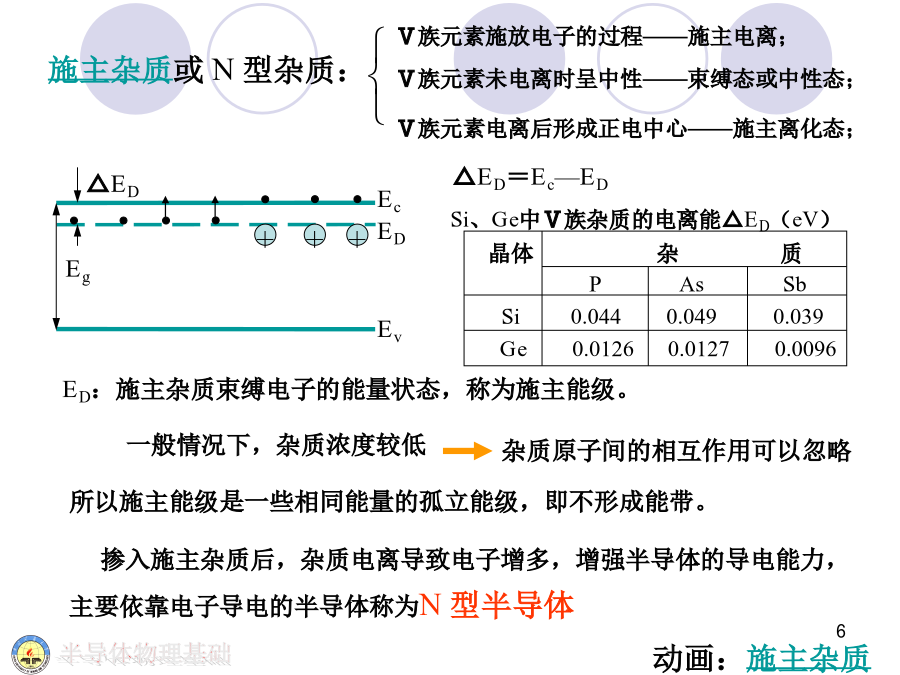

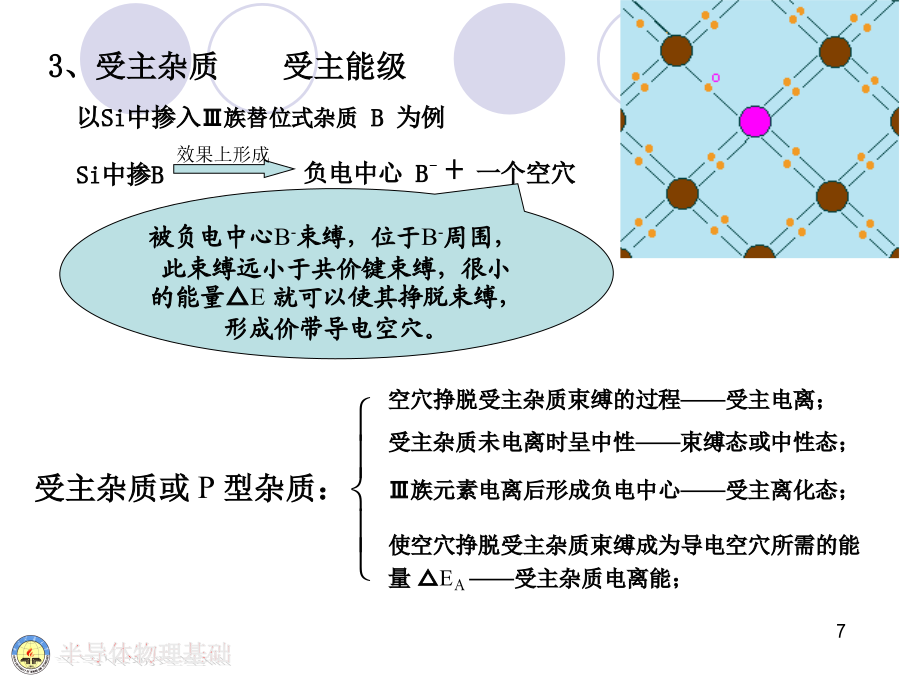

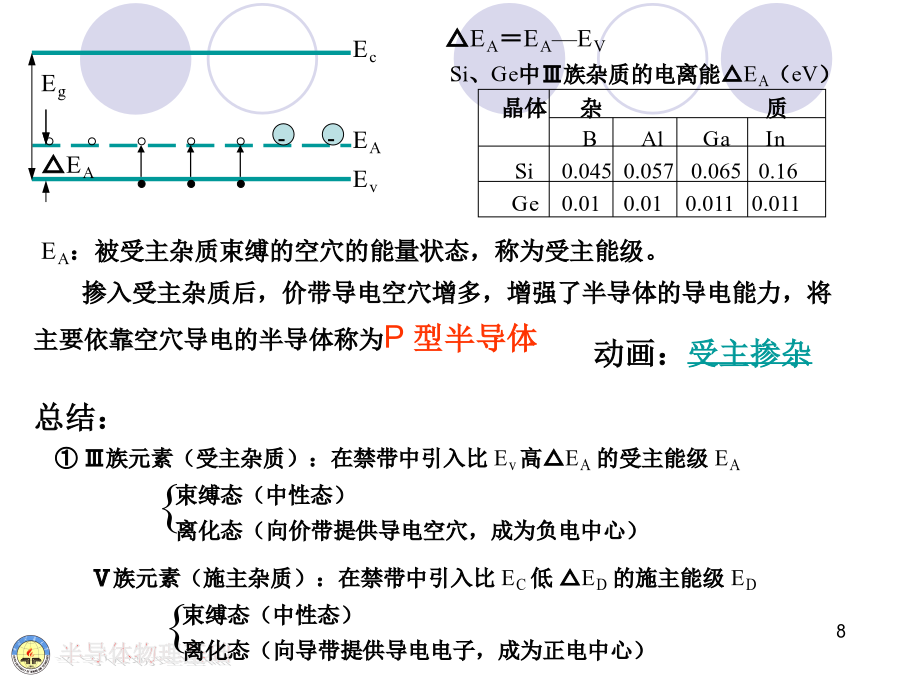

2.1硅、锗晶体中的杂质能级2.1硅、锗晶体中的杂质能级2.1硅、锗晶体中的杂质能级+42.1硅、锗晶体中的杂质能级2.1硅、锗晶体中的杂质能级被施主杂质束缚的电子的能量状态称为施主能级ED。施主能级位于离导带低很近的禁带中杂质原子间的相互作用可忽略,某一种杂质的施主能级是一些具有相同能量的孤立能级。2.1.3受主杂质受主能级空穴2.1硅、锗晶体中的杂质能级2.1硅、锗晶体中的杂质能级被受主杂质束缚的空穴的能量状态称为受主能级EA。施主能级位于离价带顶很近的禁带中杂质原子间的相互作用可忽略,某一种杂质的受

半导体中的杂质和缺陷能级.ppt

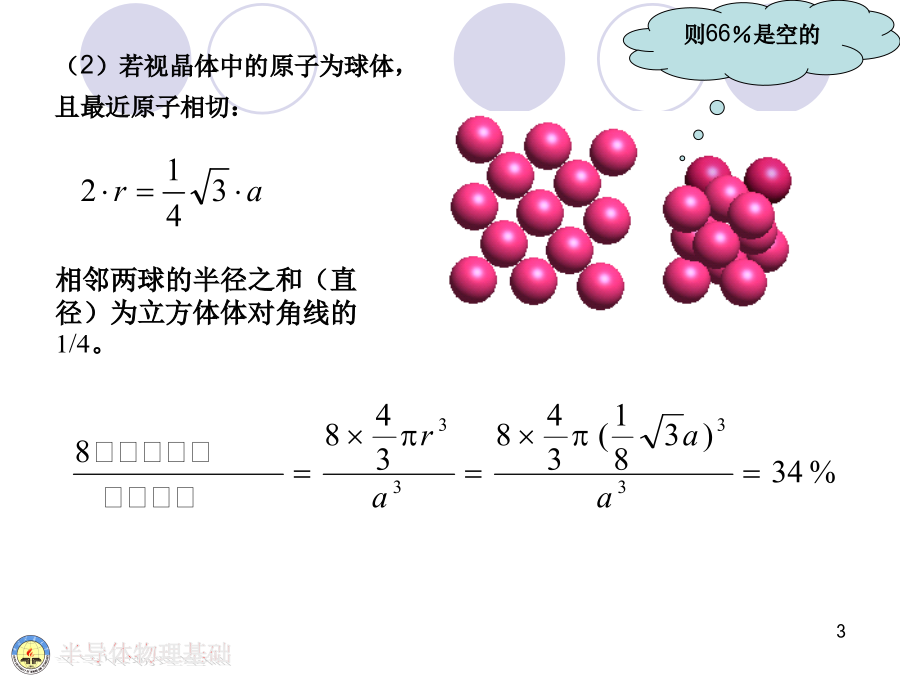

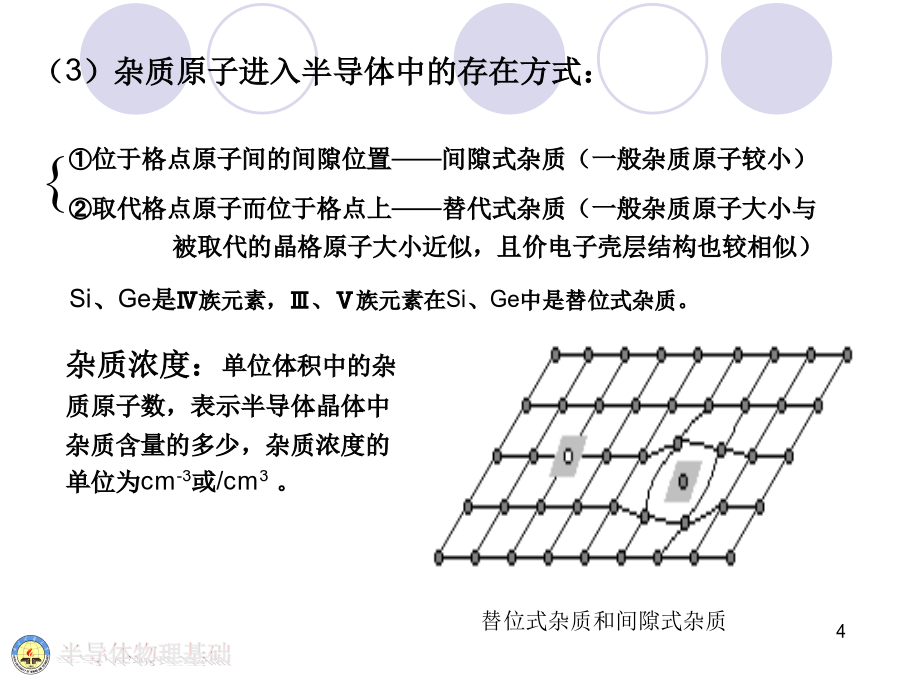

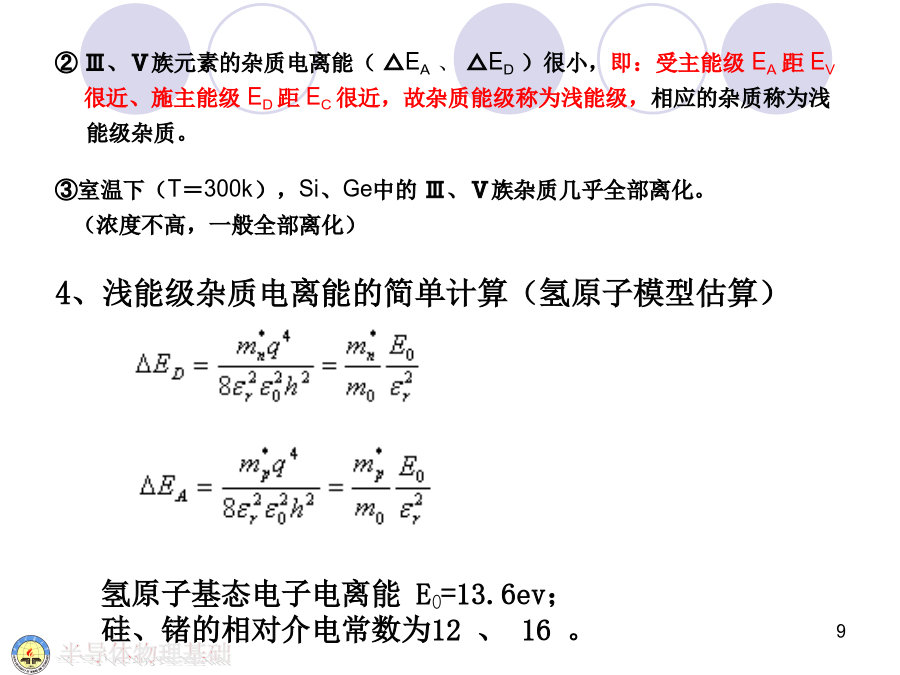

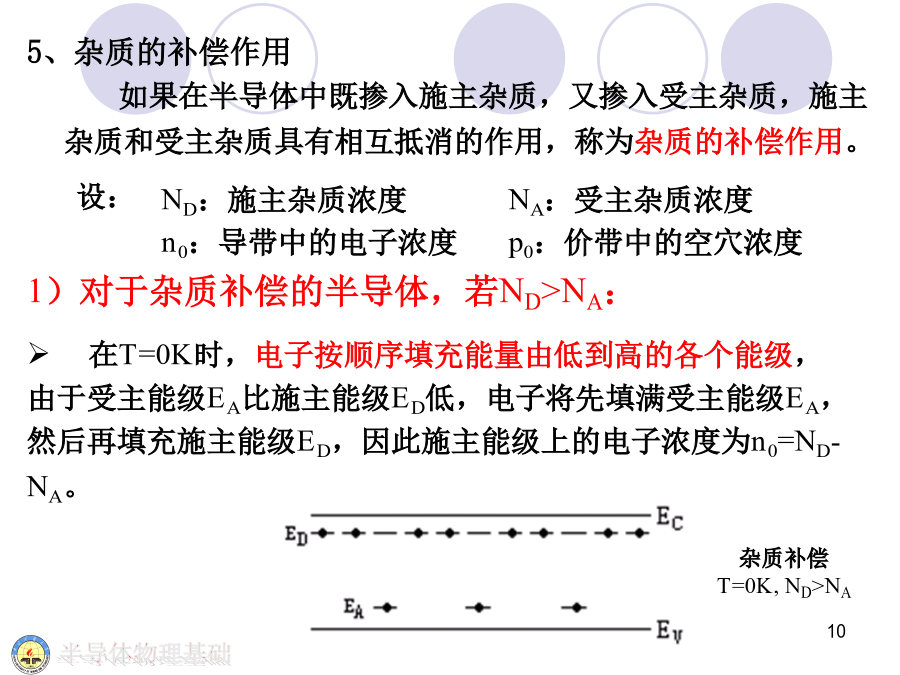

第二章半导体中的杂质和缺陷能级原子并非固定不动,格点原子在平衡位置附近振动;(2)若视晶体中的原子为球体,且最近原子相切:(3)杂质原子进入半导体中的存在方式:2、施主杂质施主能级施主杂质或N型杂质:3、受主杂质受主能级Ec②Ⅲ、Ⅴ族元素的杂质电离能(△EA、△ED)很小,即:受主能级EA距EV很近、施主能级ED距EC很近,故杂质能级称为浅能级,相应的杂质称为浅能级杂质。5、杂质的补偿作用通常当温度达到大约100K以上时,施主能级上的ND-NA个电子就全部被激发到导带,这时导带中的电子浓度n0=ND-NA

半导体中杂质和缺陷能级.ppt

22.1.1、杂质的类型举例:Si中掺磷P(Si:P)2.1.2施主杂质、施主能级杂质电离能:是使被俘获的电子摆脱束缚,从而可以成为导电电子所需的能量△ED=EC-ED2.1.3受主杂质、受主能级在Si单晶中,Ⅲ族受主替位杂质两种荷电状态的价键图(a)电离态(b)中性受主态△EA=EA-EV杂质半导体杂质能级位于禁带之中上述杂质的特点:施主电离能△ED《Eg受主电离能△EA《Eg2.1.4浅能级杂质电离能的简单计算(2)氢原子基态电子的电离能正、负电荷所处介质:估算结果与实际测量值有相同数量级2.1.5、

半导体中杂质和缺陷能级.ppt

22.1.1、杂质的类型举例:Si中掺磷P(Si:P)2.1.2施主杂质、施主能级杂质电离能:是使被俘获的电子摆脱束缚,从而可以成为导电电子所需的能量△ED=EC-ED2.1.3受主杂质、受主能级在Si单晶中,Ⅲ族受主替位杂质两种荷电状态的价键图(a)电离态(b)中性受主态△EA=EA-EV杂质半导体杂质能级位于禁带之中上述杂质的特点:施主电离能△ED《Eg受主电离能△EA《Eg2.1.4浅能级杂质电离能的简单计算(2)氢原子基态电子的电离能正、负电荷所处介质:估算结果与实际测量值有相同数量级2.1.5、