基于AES的192比特位密钥扩展系统及方法.pdf

邻家****ng

亲,该文档总共17页,到这已经超出免费预览范围,如果喜欢就直接下载吧~

相关资料

基于AES的192比特位密钥扩展系统及方法.pdf

本发明公开了一种基于高级加密标准AES的192比特位密钥扩展系统及方法,主要解决现有192比特AES加密算法中密钥扩展过程的低效率以及高功耗问题。其实现过程是:在密钥扩展的第一轮对初始密钥进行存储,取前4列作为该轮密钥扩展的轮密钥,并进行字循环、字节替换、按位异或操作;将所得结果作为轮密钥同时存储在本地寄存器和外部存储单元中,供加密流程读取使用;之后每轮都对前一轮所得轮密钥重复上述操作,直到得到所有12个轮密钥,结束密钥扩展。本发明能够兼顾密钥扩展的实时性以及轮密钥的可重用性,实现高效率和低功耗的密钥扩展

基于高级加密标准AES的128比特位密钥扩展方法.pdf

本发明公开了一种基于高级加密标准AES的128比特位密钥扩展系统及方法,主要解决现有AES加密算法中的128比特密钥扩展过程的低效率和高功耗问题。其实现过程是:在密钥扩展的第一轮对初始密钥进行存储,作为该轮的轮密钥,对轮密钥进行字循环、字节替换、按位异或操作并将所得轮密钥同时存储在本地寄存器和外部存储单元中,供加密流程读取使用;之后每轮都对前一轮所得轮密钥重复上述操作,直到得到所有10个轮密钥,则结束密钥扩展。本发明能保证密钥扩展的实时性以及轮密钥的可重用性,实现密钥扩展的高效率和低功耗,可用于AES加密

256比特位密钥扩展系统及方法.pdf

本发明公开了一种基于高级加密标准AES的256比特位密钥扩展系统及方法,主要解决现有256比特AES加密算法中密钥扩展过程的低效率以及高功耗问题。其实现过程是:在密钥扩展的第一轮对初始密钥进行存储,取前4列作为该轮密钥扩展的轮密钥,并进行字循环、字节替换、按位异或操作;根据序号n执行新一次字节替换和二次按位异或操作;将两次按位异或操作结果作为轮密钥存储在本地寄存器和外部存储单元中,供加密流程读取使用;之后每轮都对前一轮所得轮密钥重复上述操作,直到得到所有14个轮密钥,结束密钥扩展。本发明能够兼顾密钥扩展的

AES密钥扩展的方法.pdf

本发明公开了一种AES密钥扩展的方法,不再是基于前一轮密钥的简单迭代,而是通过密钥间的运算,在通过一定的迭代实现,降低了单一密钥迭代对前轮输入的关联性,增加了破译难度,同时由于前后关联性减小,使得整个电路的时序得到了有效地改善。

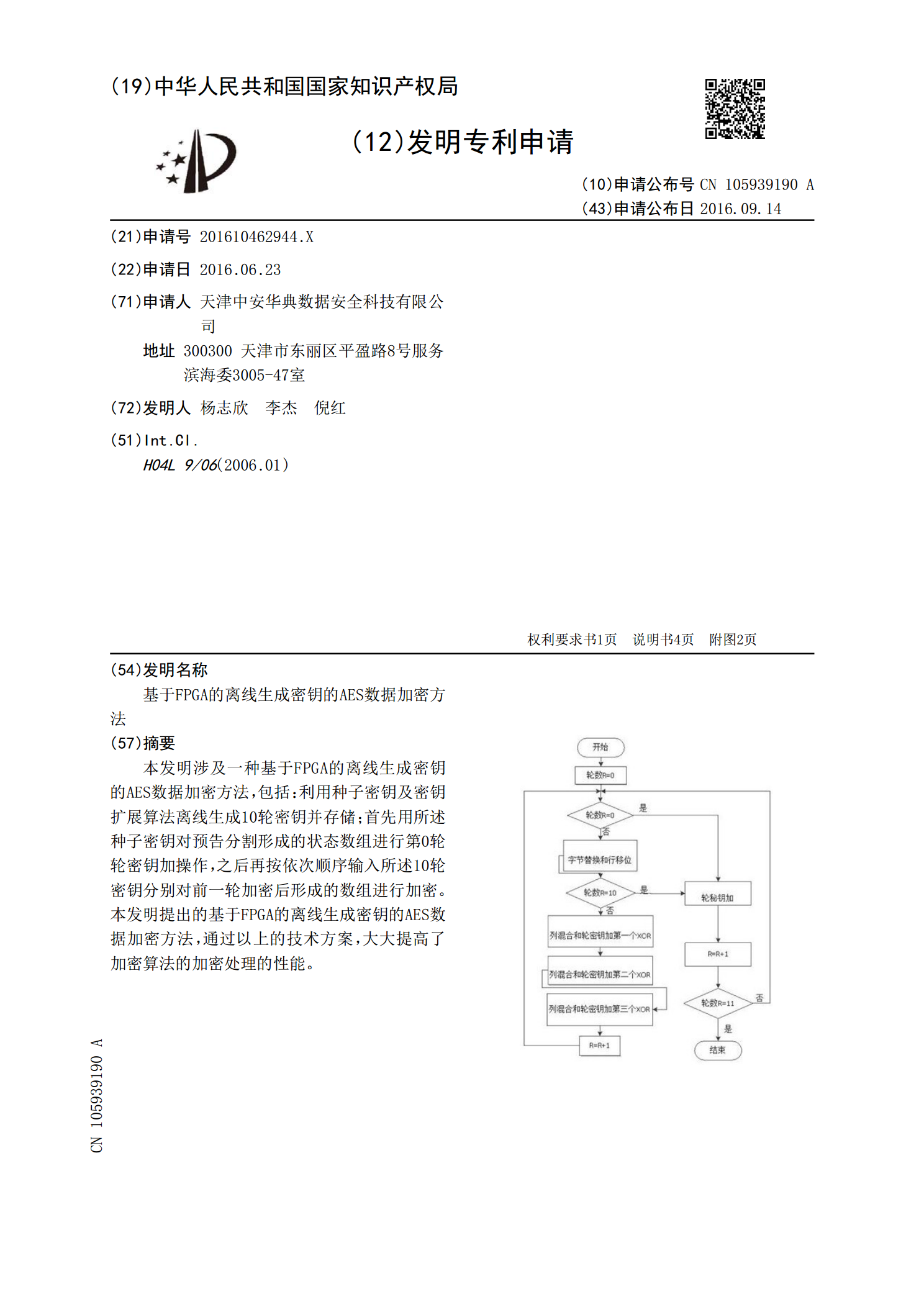

基于FPGA的离线生成密钥的AES数据加密方法.pdf

本发明涉及一种基于FPGA的离线生成密钥的AES数据加密方法,包括:利用种子密钥及密钥扩展算法离线生成10轮密钥并存储;首先用所述种子密钥对预告分割形成的状态数组进行第0轮轮密钥加操作,之后再按依次顺序输入所述10轮密钥分别对前一轮加密后形成的数组进行加密。本发明提出的基于FPGA的离线生成密钥的AES数据加密方法,通过以上的技术方案,大大提高了加密算法的加密处理的性能。