逻辑代数基础通用.ppt

YY****。。

亲,该文档总共83页,到这已经超出免费预览范围,如果喜欢就直接下载吧~

相关资料

逻辑代数基础通用.ppt

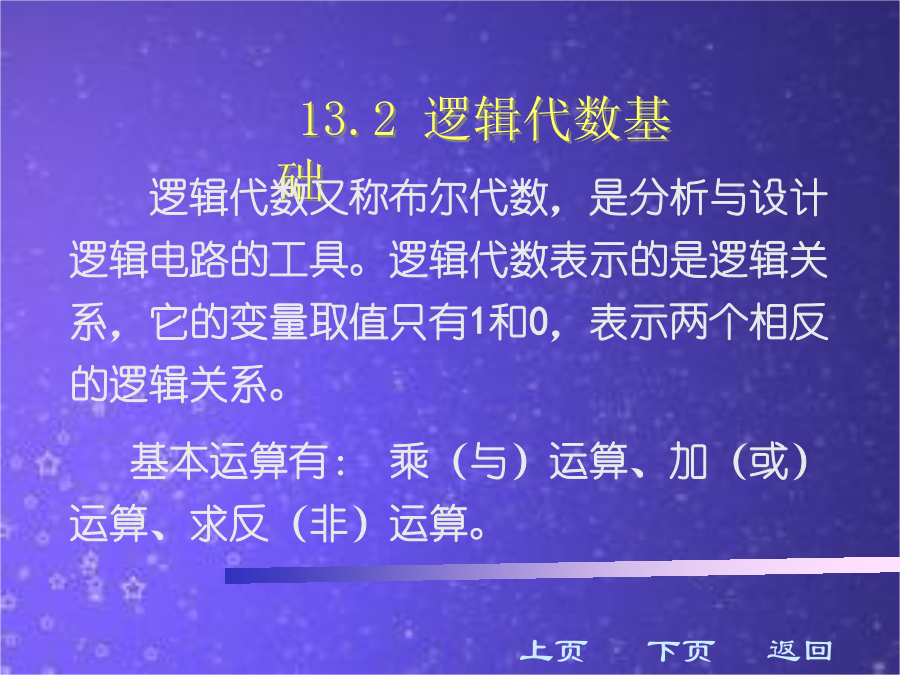

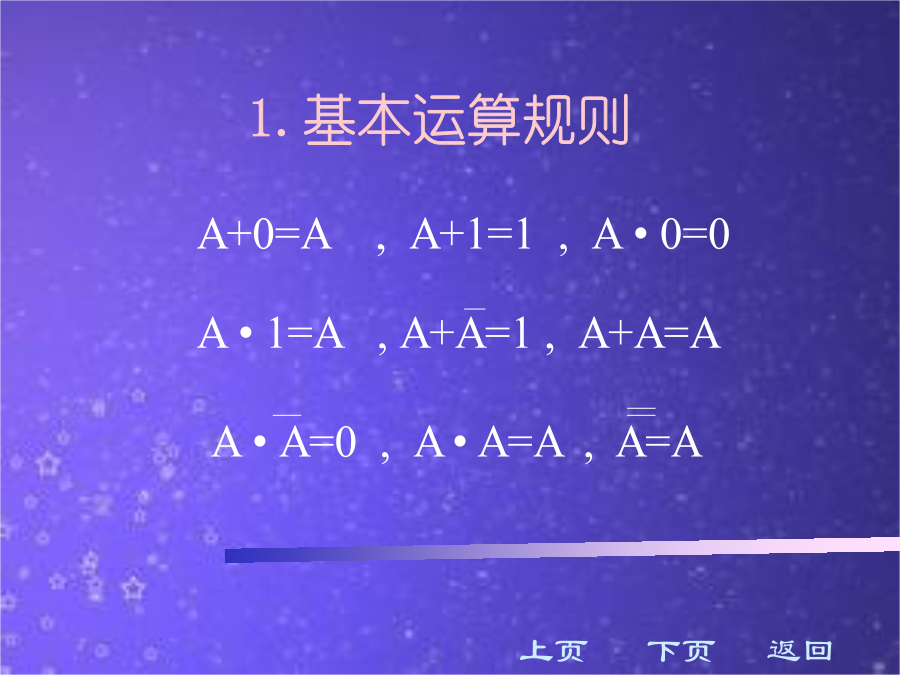

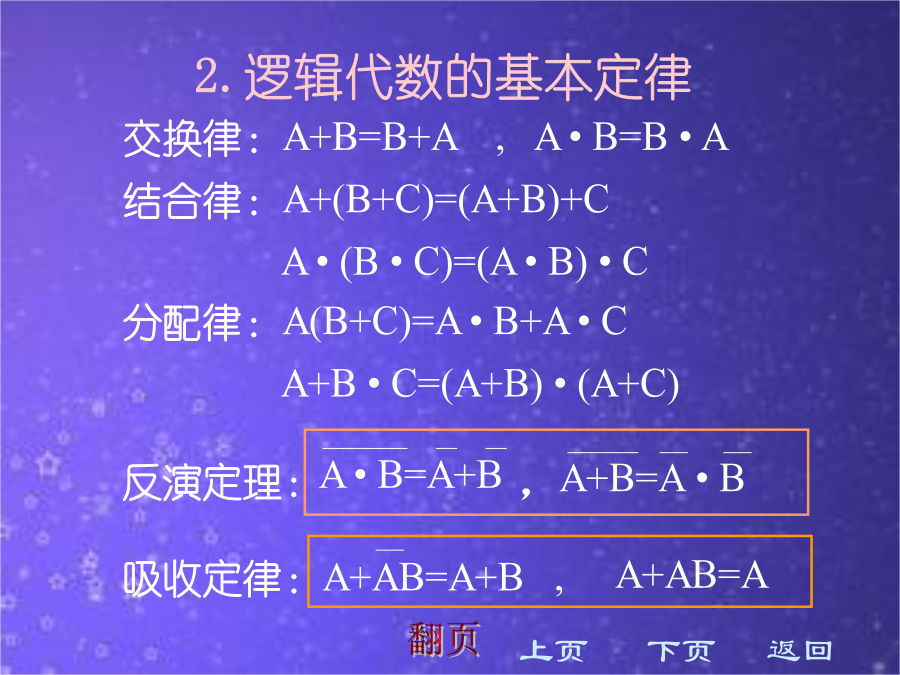

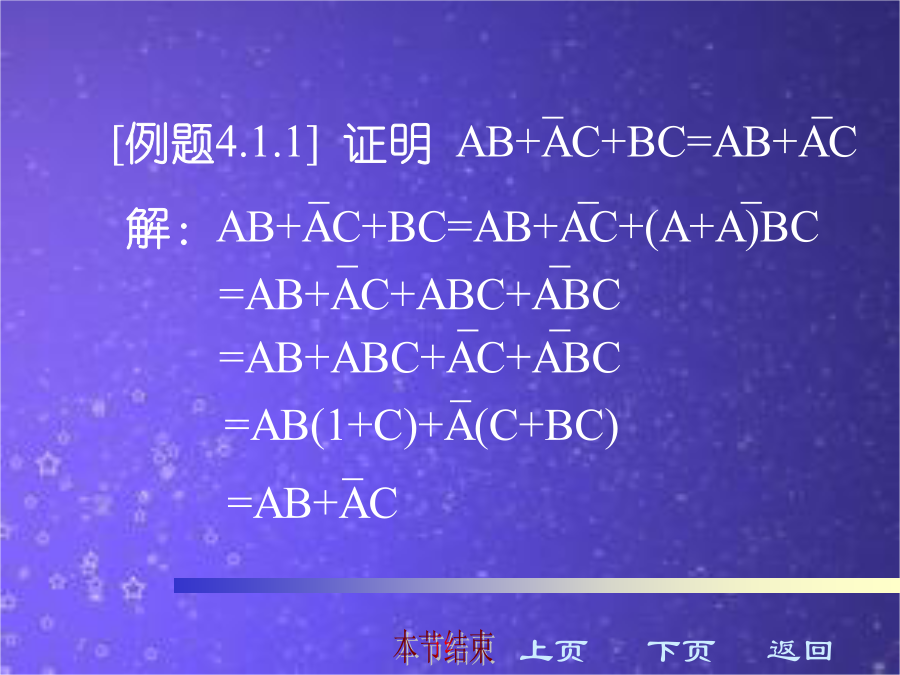

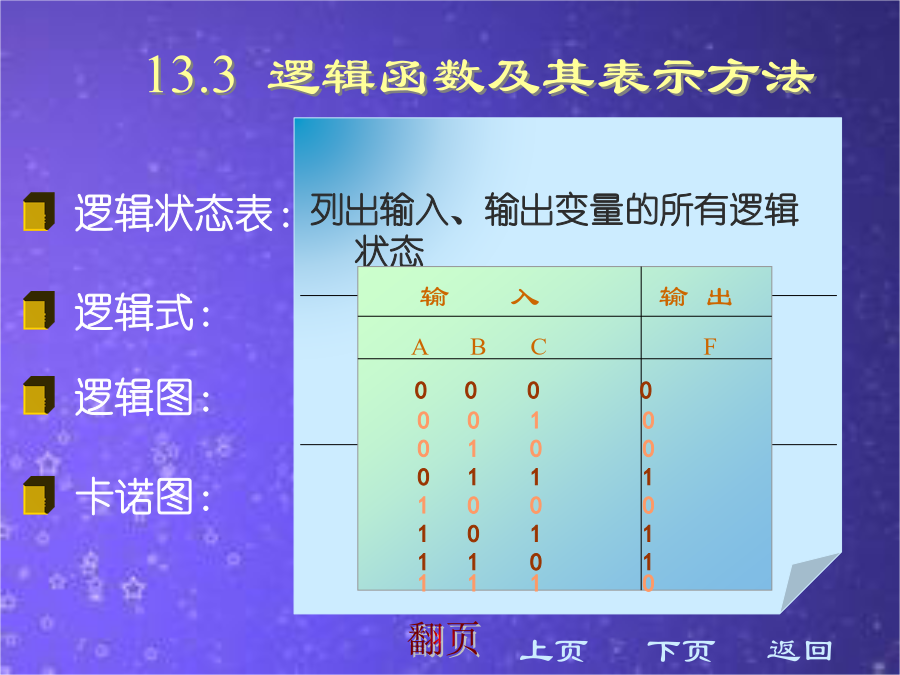

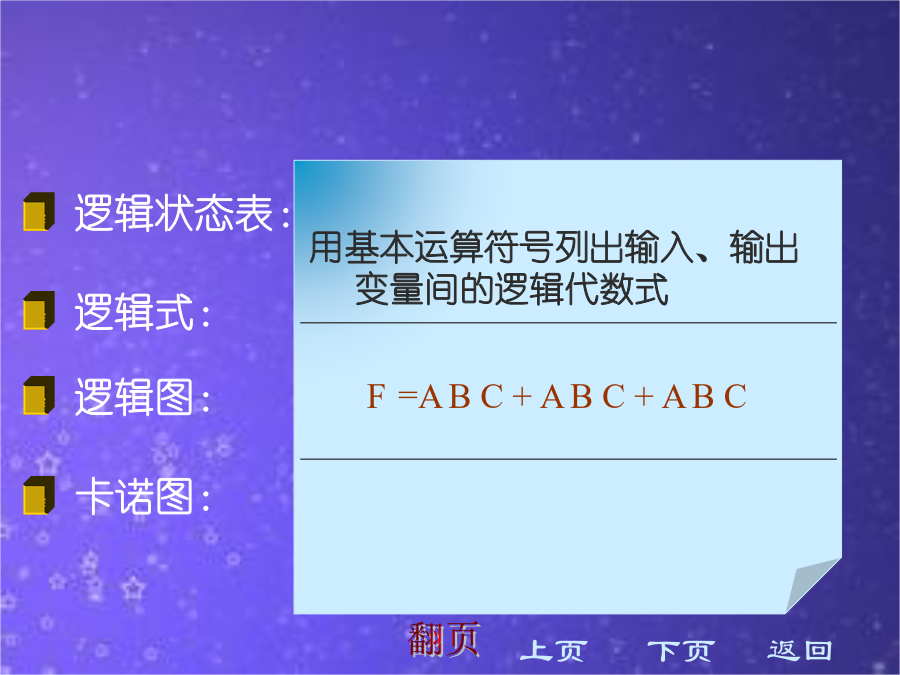

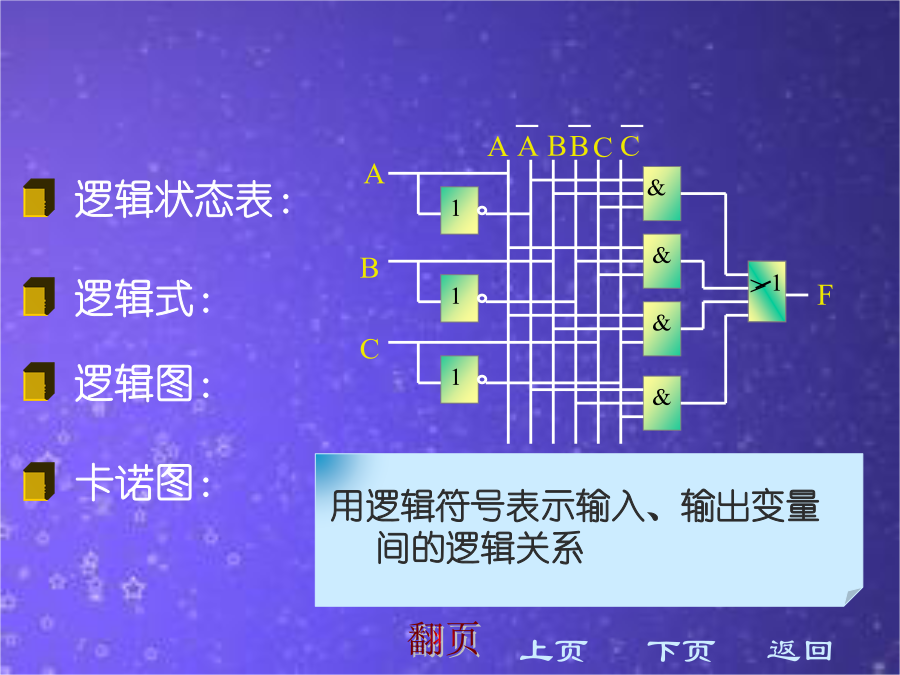

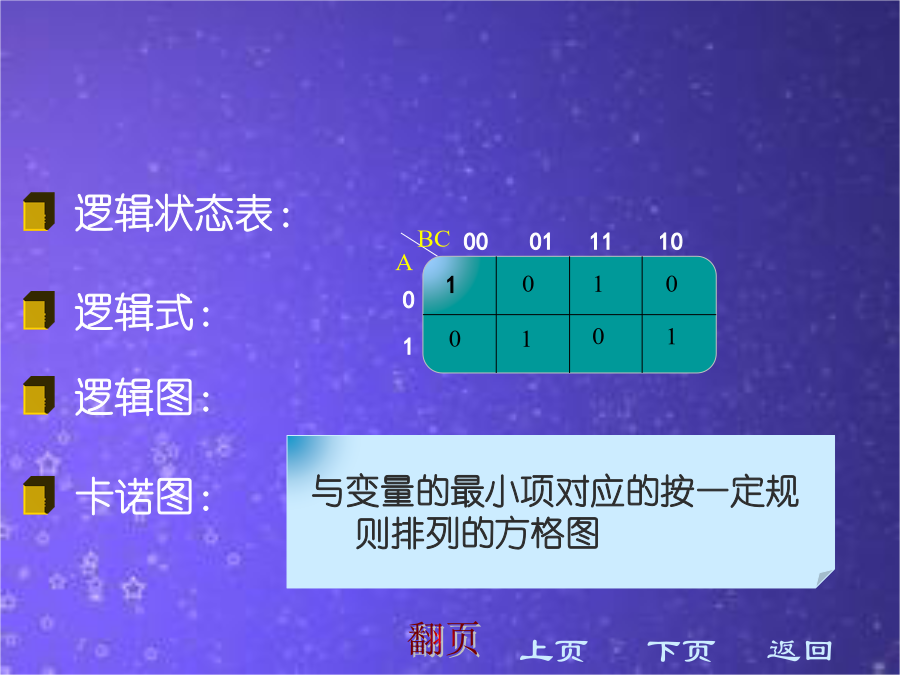

逻辑代数基础13.2逻辑代数基础1.基本运算规则2.逻辑代数的基本定律上页13.3基本逻辑运算与基本逻辑门上页上页上页上页上页上页上页逻辑函数的化简通常有以下两种方法:1.应用运算法则化简解:Y=AB(1+C+D+E)*2.卡诺图的表示及其化简化简步骤:解:●画出函数Y的卡诺图13.5组合逻辑电路的分析与设计一.组合逻辑电路的分析分析图示逻辑电路的功能1二.组合逻辑电路的设计设计一逻辑电路供三人(ABC)表决使用。每人有一电键,如果他赞成,就按电键,表示1;如果不赞成,不按电键,表示0。表决结果用指示灯来

逻辑代数基础.pptx

2024/2/82024/2/82024/2/82024/2/82024/2/82024/2/82024/2/82024/2/82024/2/82024/2/82024/2/82024/2/82024/2/82024/2/82024/2/82024/2/82024/2/82024/2/82024/2/82024/2/82024/2/82024/2/82024/2/82024/2/82024/2/82024/2/82024/2/82024/2/82024/2/82024/2/82024/2/82024/2/

逻辑代数基础.doc

第8章逻辑代数基础一、填空题1.二进制数10111111对应的八进制为277,十进制数为191。2.两输入与非门的输入为01时,输出为1;两输入或非门的输入为01时,输出为0。3.由与非门构成的基本R-S触发器,其约束方程为RS=0。4.逻辑代数有与、或和非三种基本运算。二、选择题1.下列物理量中,属于数字量的有(A,D)A.开关状态B.温度C.交流电流D.指示灯状态2.表示最大3位十进制数,需要(C)位二进制数。A.8B.9C.10D.123.逻辑函数可表示成(A)A.B.C.D.4.用于数字电路的三极

逻辑代数基本公式及定律通用.ppt

(1)(2)(3)(4)(5)(6)(7)(8)(9)(10)(11)(12)(13)(14)(15)(16)(17)(18)(19)(20)(21)(22)(23)(24)(25)(26)

逻辑代数基础1.pptx

模拟与数字电路AnalogandDigitalCircuits2024/2/82024/2/82024/2/82024/2/82024/2/82024/2/82024/2/82024/2/82024/2/82024/2/82024/2/82024/2/82024/2/82024/2/82024/2/82024/2/82024/2/82024/2/82024/2/82024/2/82024/2/82024/2/82024/2/82024/2/8