高k栅介质金属栅结构CMOS器件的等效氧化层厚度控制技术.docx

快乐****蜜蜂

在线预览结束,喜欢就下载吧,查找使用更方便

相关资料

高k栅介质金属栅结构CMOS器件的等效氧化层厚度控制技术.docx

高k栅介质金属栅结构CMOS器件的等效氧化层厚度控制技术摘要高k栅介质金属栅结构CMOS器件的等效氧化层厚度控制技术是当前研究的焦点。本文重点探讨了等效氧化层厚度的控制技术,包括工艺优化、材料设计等方面,具体介绍了PVD、CVD制备高k栅材料的工艺步骤和控制方法,以及在高k栅介质金属栅结构中等效氧化层厚度的控制手段和实现效果等。最后,本文总结了等效氧化层厚度控制技术现状,展望了未来的发展方向。关键词:高k栅介质金属栅,等效氧化层厚度,制备工艺,控制技术引言随着半导体工艺逐步向纳米级别发展,CMOS器件尺寸

高K金属栅结构CMOS器件栅工程工艺研究的任务书.docx

高K金属栅结构CMOS器件栅工程工艺研究的任务书任务书一、任务背景随着VLSI技术的不断发展,CMOS工艺逐渐成为VLSI芯片制造过程中的主流工艺之一。其中,CMOS器件的可靠性和性能表现,主要取决于其栅工程的工艺控制。当前,随着半导体工艺的不断进步,高K金属栅结构CMOS器件的出现,极大地改善了器件的性能,但其栅工程技术亟需深入研究。因此,本项目旨在研究高K金属栅结构CMOS器件的栅工程工艺,建立相应的工艺流程和优化方法,以实现CMOS器件性能的稳定和提升。二、任务目标本项目的主要任务是研究高K金属栅结

CMOS器件栅氧化层的制造方法.pdf

本发明公开了一种CMOS器件栅氧化层的制造方法,包括在硅衬底上制备浅沟道隔离区、衬垫氧化层和硬掩膜,通过刻蚀两个浅沟道隔离区之间的场区以露出有源区及有源区边缘的部分浅沟道隔离区;通过炉管工艺,在有源区表面生长一层氧化层,使得有源区的边缘圆化;通过湿法刻蚀,去除有源区表面的氧化层;通过炉管工艺,在有源区表面生长栅氧化层。本发明利用炉管工艺在有源区表面生成一层氧化层,随后利用湿法刻蚀将其去除,通过这两步工艺可以改善有源区的边缘尖角,改善栅氧化层的形貌,从而提高器件的性能。

金属栅层/高K栅介质层的叠层结构刻蚀后的清洗方法.pdf

本发明涉及一种金属栅层/高K栅介质层的叠层结构刻蚀后的清洗方法,属于集成电路制造技术领域。在金属栅层/高K栅介质层叠层结构刻蚀后,采用含有氢氟酸的混合溶液进行清洗,不仅可以完全去除栅叠层结构上留下的含有金属的聚合物残余,而且对于高K材料在干法刻蚀过程中部分去除的刻蚀策略,可以在清洗的过程中完全去除高K材料,从而更有利于满足纳米级CMOS器件在形成栅极图形时对Si衬底损失的要求。另外,因该溶液对场区SiO2的腐蚀速率较低,能够满足器件集成的需要。

高K栅介质/金属栅叠层栅结构刻蚀后聚合物去除方法.pdf

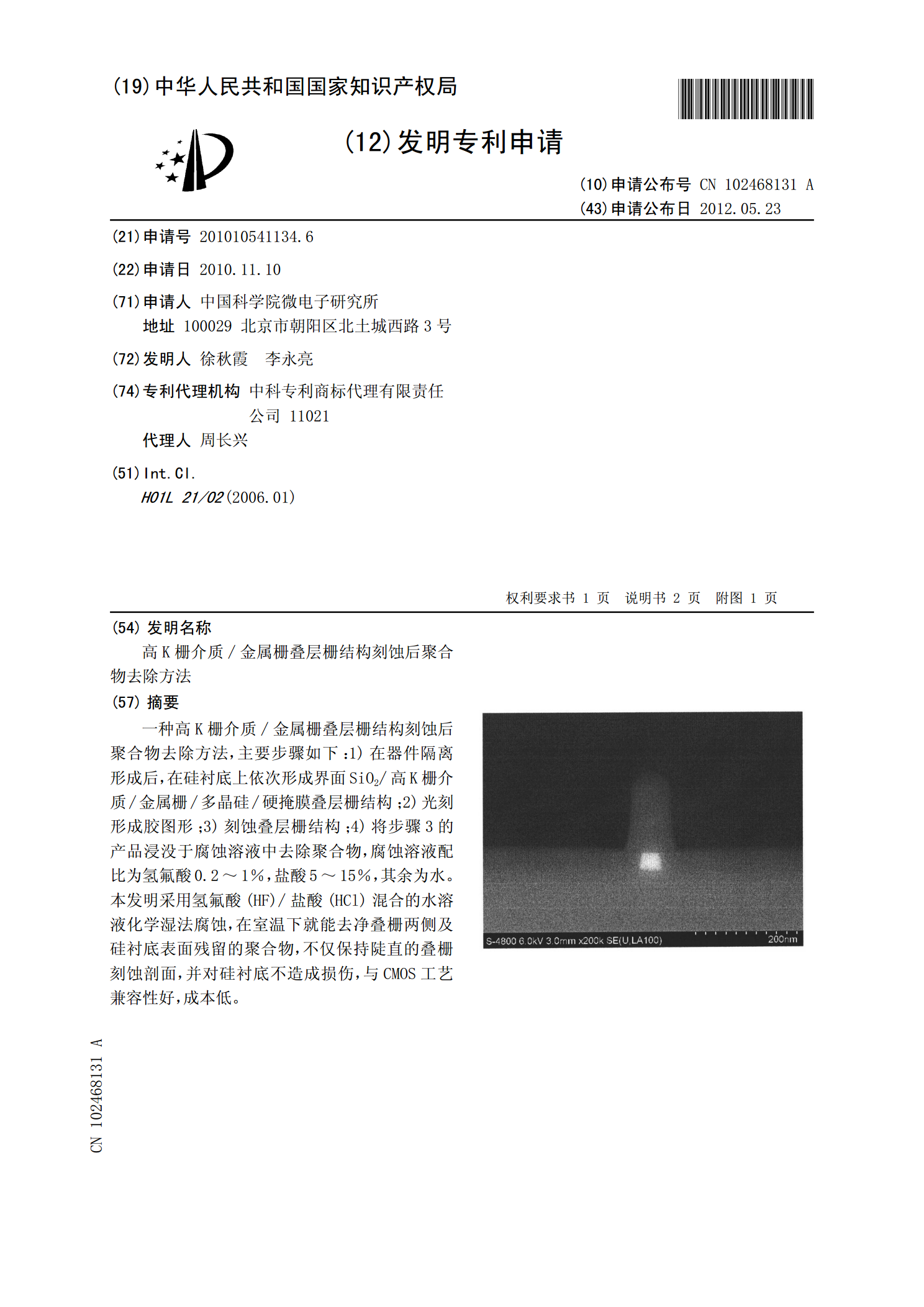

一种高K栅介质/金属栅叠层栅结构刻蚀后聚合物去除方法,主要步骤如下:1)在器件隔离形成后,在硅衬底上依次形成界面SiO2/高K栅介质/金属栅/多晶硅/硬掩膜叠层栅结构;2)光刻形成胶图形;3)刻蚀叠层栅结构;4)将步骤3的产品浸没于腐蚀溶液中去除聚合物,腐蚀溶液配比为氢氟酸0.2~1%,盐酸5~15%,其余为水。本发明采用氢氟酸(HF)/盐酸(HCl)混合的水溶液化学湿法腐蚀,在室温下就能去净叠栅两侧及硅衬底表面残留的聚合物,不仅保持陡直的叠栅刻蚀剖面,并对硅衬底不造成损伤,与CMOS工艺兼容性好,成本低