时序逻辑电路分析与设计方法.ppt

ca****ng

亲,该文档总共20页,到这已经超出免费预览范围,如果喜欢就直接下载吧~

相关资料

时序逻辑电路分析与设计方法.ppt

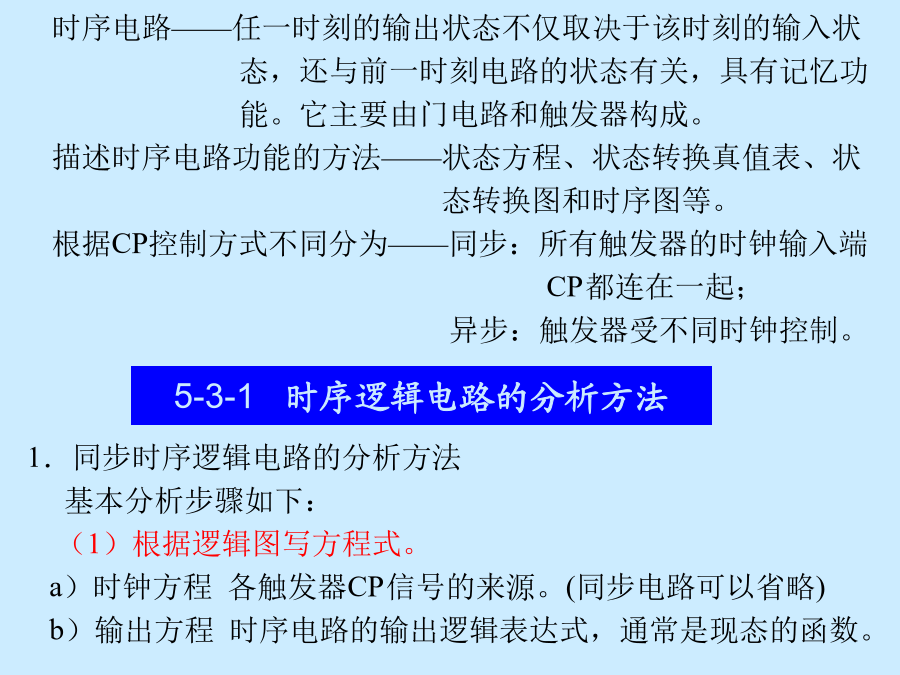

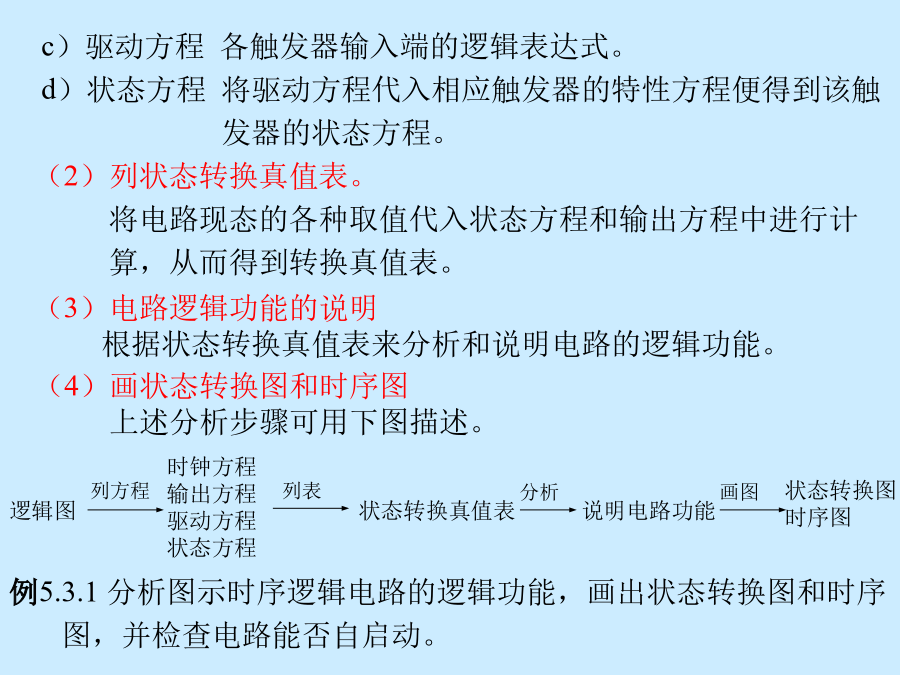

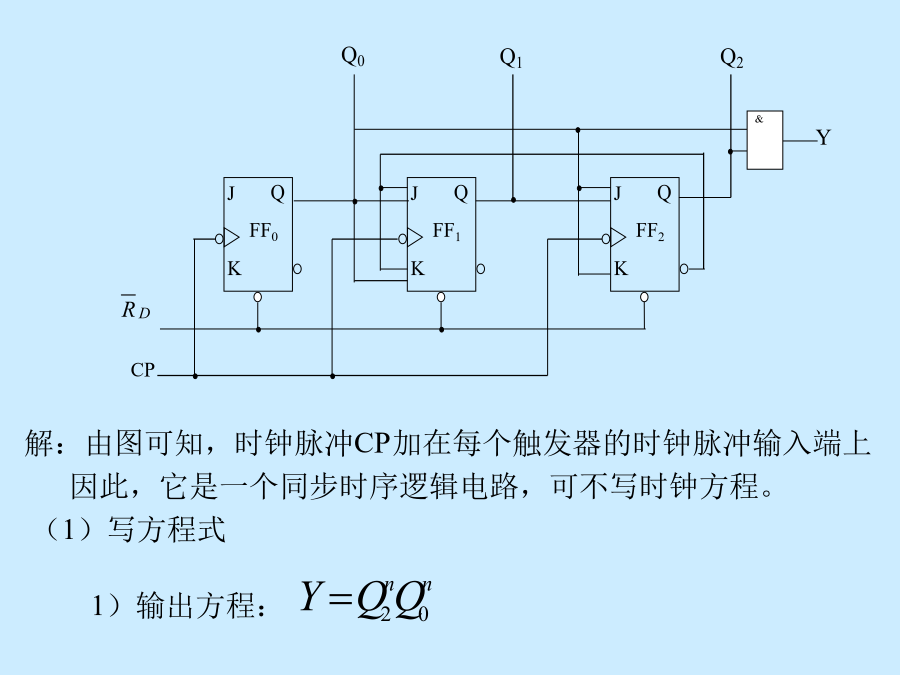

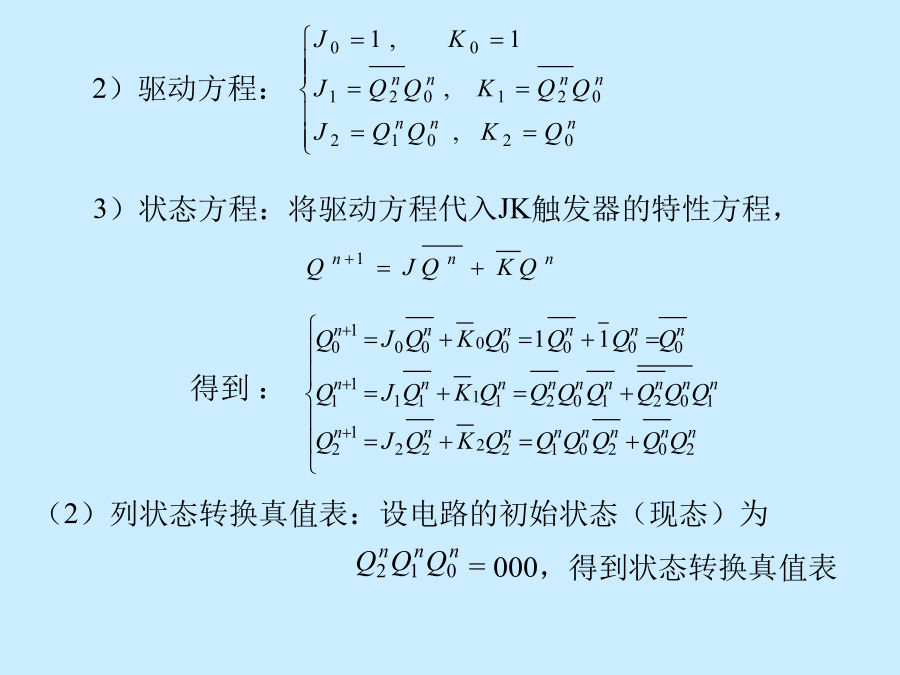

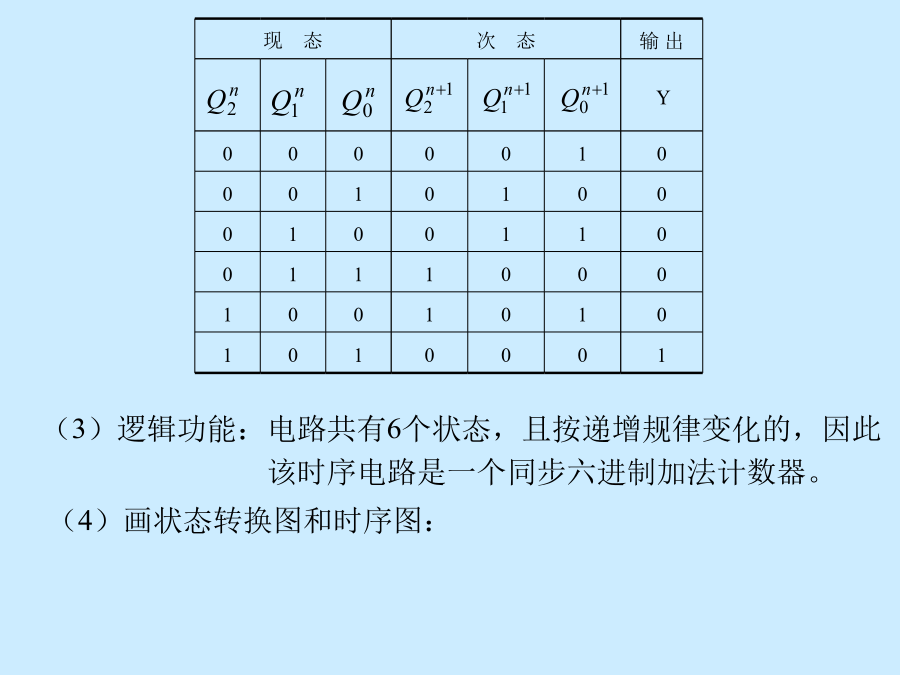

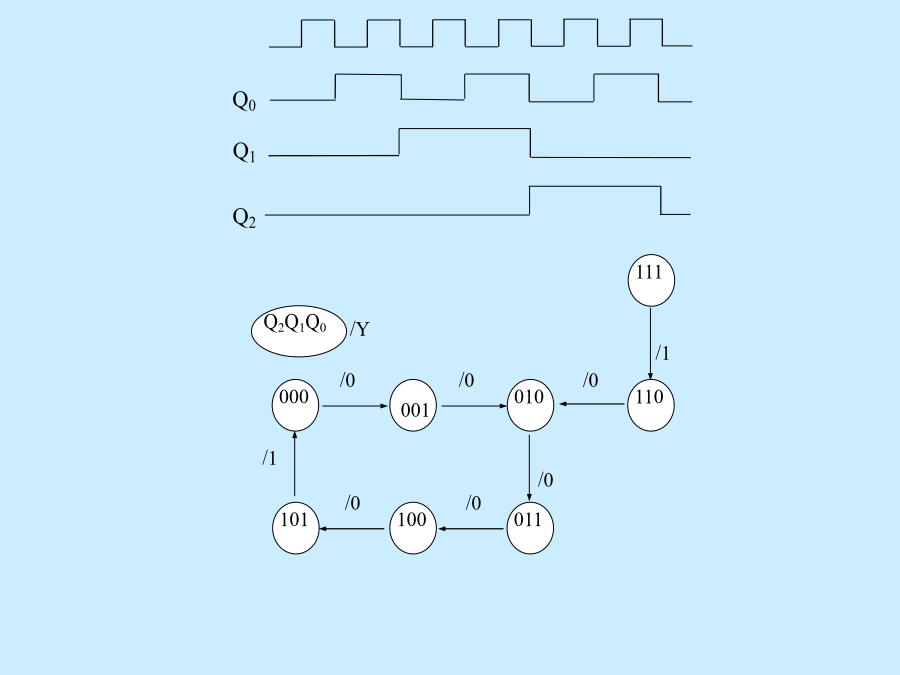

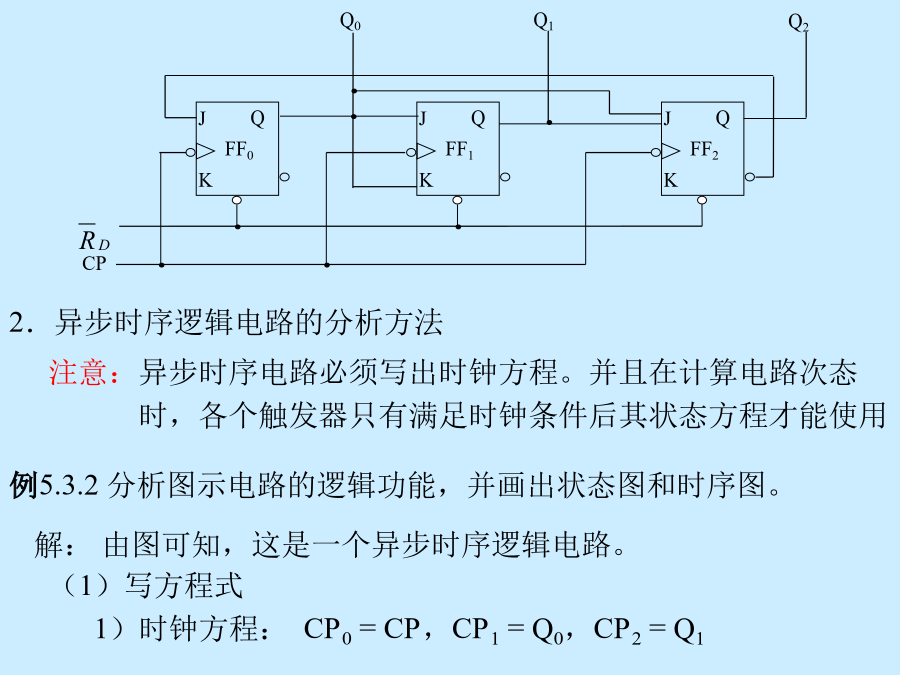

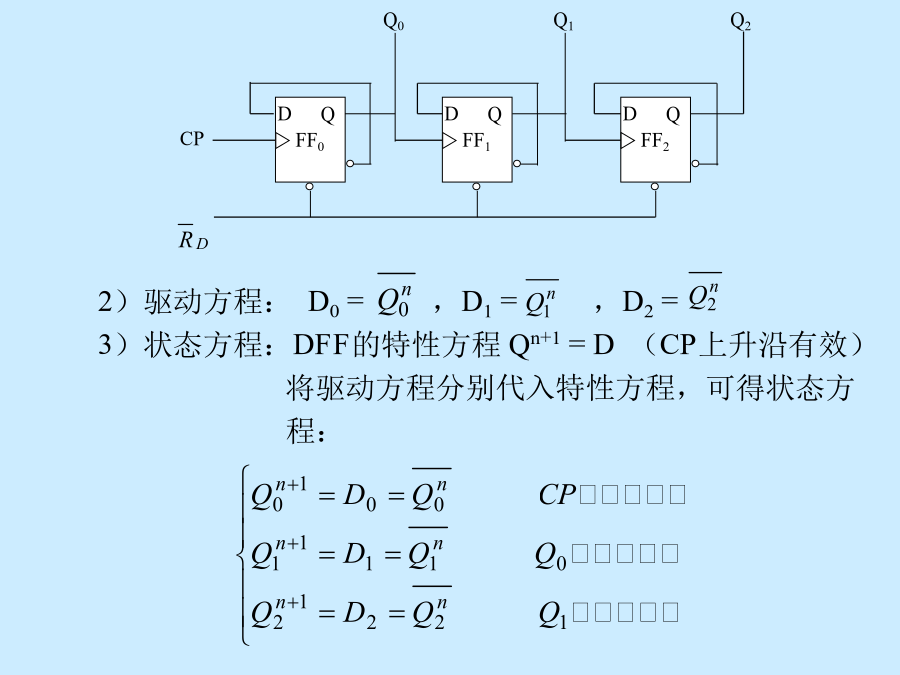

时序逻辑电路分析与设计方法解:由图可知,时钟脉冲CP加在每个触发器的时钟脉冲输入端上因此,它是一个同步时序逻辑电路,可不写时钟方程。(1)写方程式2)驱动方程:(5)检查电路能否自启动:110和111两个状态称为“无效状态”。如果由于某种原因而进入无效状态,只要继续输入CP,电路便会自动返回有效状态,则该电路能够自启动。否则不能自启动。由以上分析知,图示电路为能自启动同步六进制加法计数器5-3-2时序逻辑电路的设计方法(5)画逻辑图:根据选用的触发器和求得的输出方程和驱动方程,即可画出逻辑电路图。(6)检

时序逻辑电路的分析与设计.ppt

第六章时序逻辑电路的分析与设计教学要求时序电路必然具有记忆功能,因而组成时序电路的基本单元是触发器。二、时序电路的分类三、时序电路的描述3.状态图§6.2时序逻辑电路的分析电路图例2345例2试分析如图所示时序电路的逻辑功能。J2=K2=XQ13.列出其状态转换表,画出状态转换图和波形图状态图根据状态转换表,画出波形图。X=0时例234教学要求§6.3时序逻辑电路的设计方法设计要求例4状态方程比较,得驱动方程:检查电路能否自启动设计一个串行数据检测电路,当连续输入3个或3个以上1时,电路的输出为1,其它

时序逻辑电路分析与设计.ppt

第4章时序逻辑电路分析与设计4.1同步时序电路分析【例4-1】分析图4-1所示同步时序电路的功能,并画出电路的工作波形。解输出方程组表4-1例4-1状态表图4-2例4-1的状态图图4-3例4-3的电路工作波形由状态图可见,当输入X=0时,电路始终处于保持状态;当输入X=1时,电路呈现出来一个CP脉冲状态加1的特点,且当电路处于状态11(3)时,下一个CP脉冲到来后状态变为00且产生Z=1输出,为四进制加法计数。因此,本电路为一个可控同步四进制加法计数器,X为控制端,Z为进位输出。当控制端X=0时,维持原态

时序逻辑电路的分析与设计:.ppt

时序逻辑电路的分析与设计:解:1.驱动方程:3.状态转换真值表:§7.3时序逻辑电路的设计:例2:设计一个同步七进制计数器,要求它按自然态序变化且用维阻D触发器构成。2.填写状态转换真值表4a:状态方程5.画电路图6.检验自启动作业:税收征收管理工作的基本内容与基本规定冯鸣一、税收征管工作的基本内容税收征收管理工作的七项基本的工作内容(一)税收征收管理工作的内容(一)税收征收管理工作的内容(一)税收征收管理工作的内容(一)税收征收管理工作的内容(二)税务登记的概念与内容(二)税务登记的概念与内容(二)税务

同步时序逻辑电路的分析方法异步时序逻辑电路的分析方法逻辑功能、(1).ppt

同步时序逻辑电路的分析方法异步时序逻辑电路的分析方法逻辑功能、自启动功能任意进制计数器的设计方法例1:试用一片二进制计数器74LS293构成一个十二进制计数器。例2:试用十进制计数器74LS90构成二十三进制计数器。反馈归零法的有关问题反馈置数法例4:使用74LS163构成一个计数状态为二进制0111~1111的计数器。寄存器移位寄存器四位左移寄存器双向移位寄存器寄存器应用举例作业:P.156.5-75-12