微处理器的引脚.ppt

xf****65

亲,该文档总共32页,到这已经超出免费预览范围,如果喜欢就直接下载吧~

相关资料

微处理器的引脚.ppt

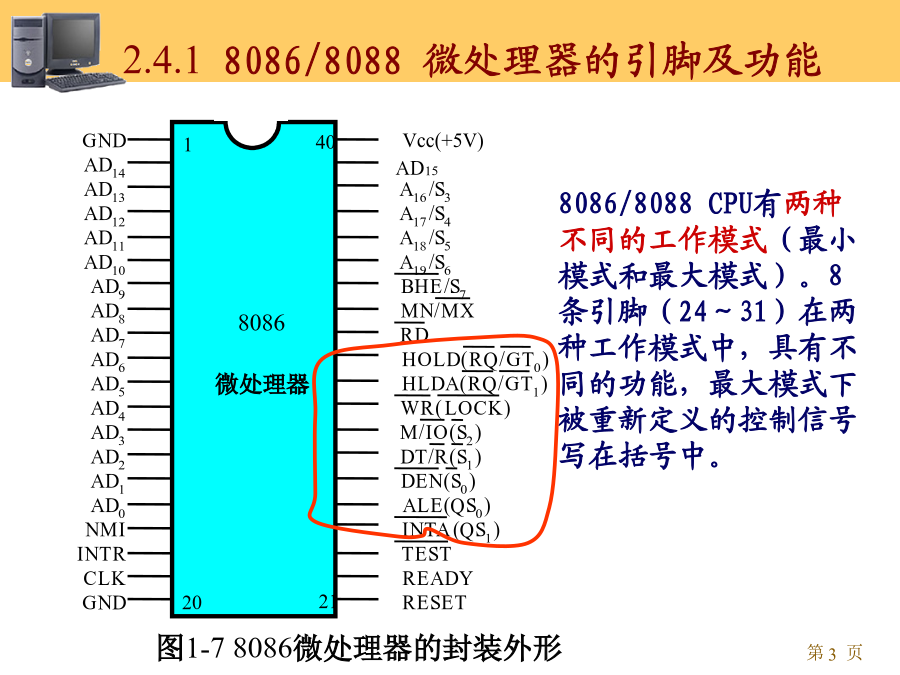

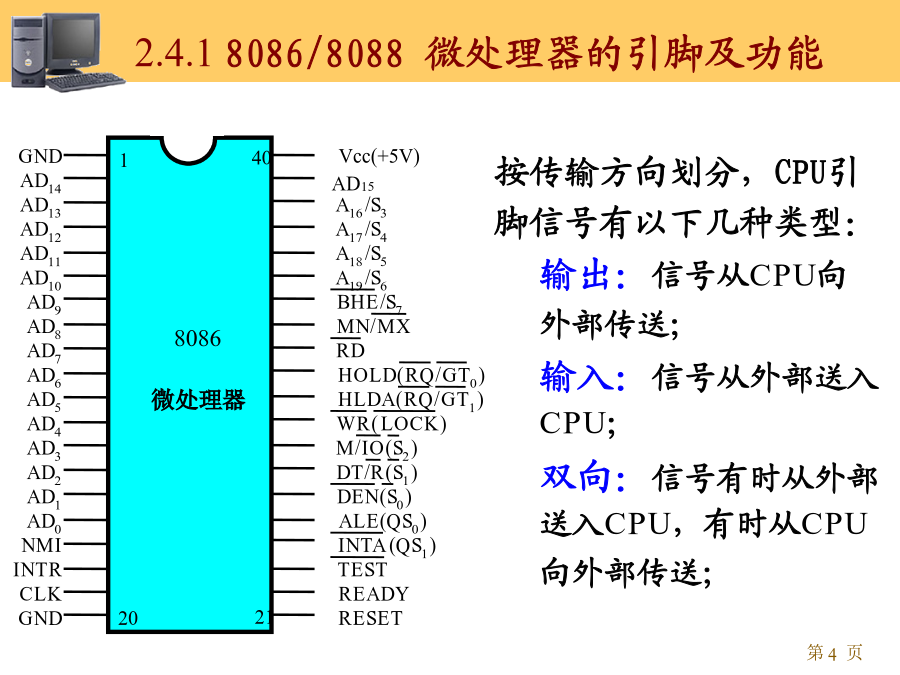

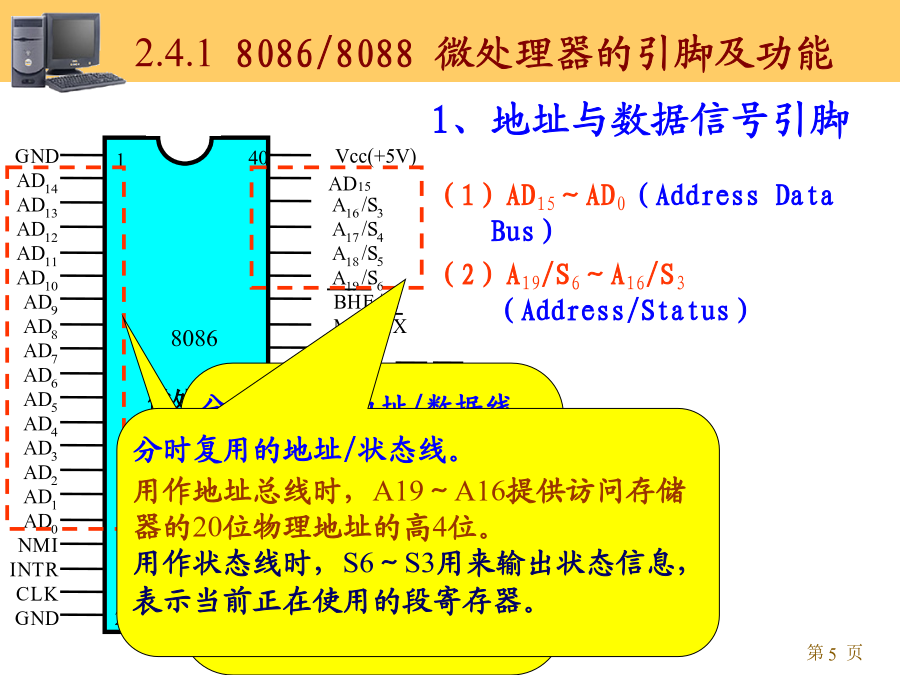

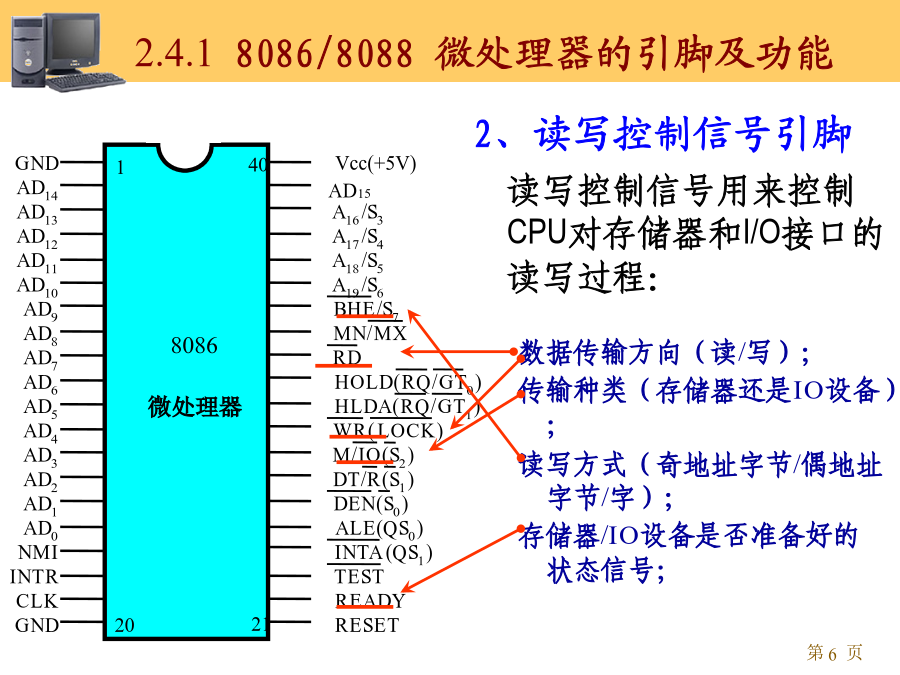

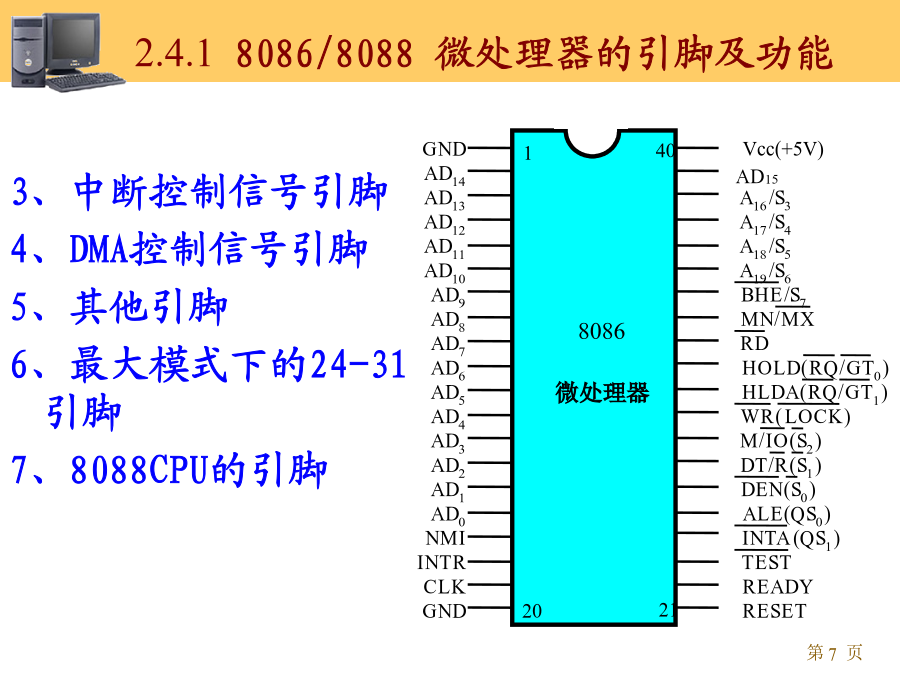

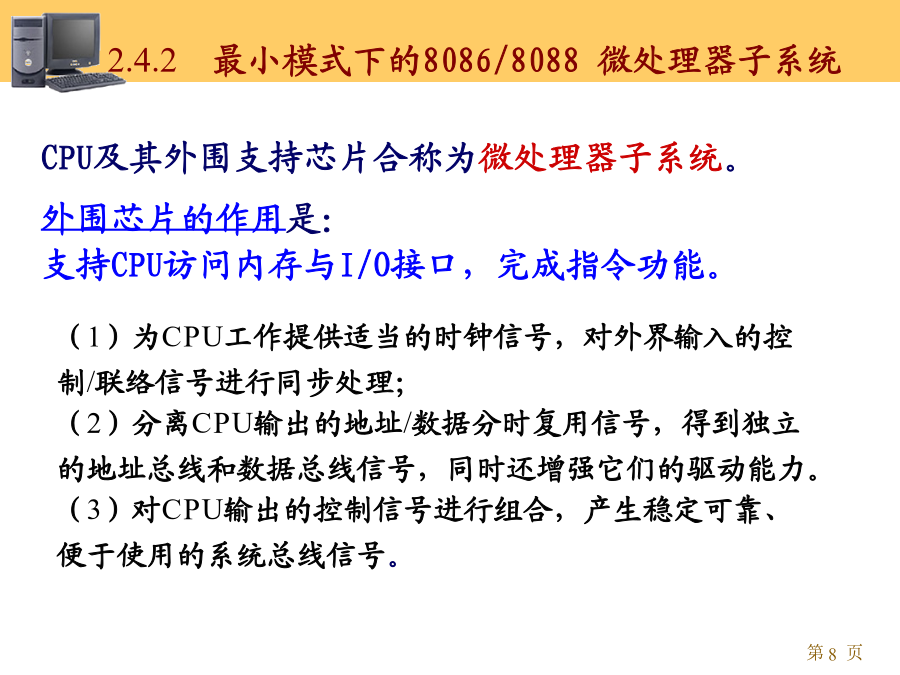

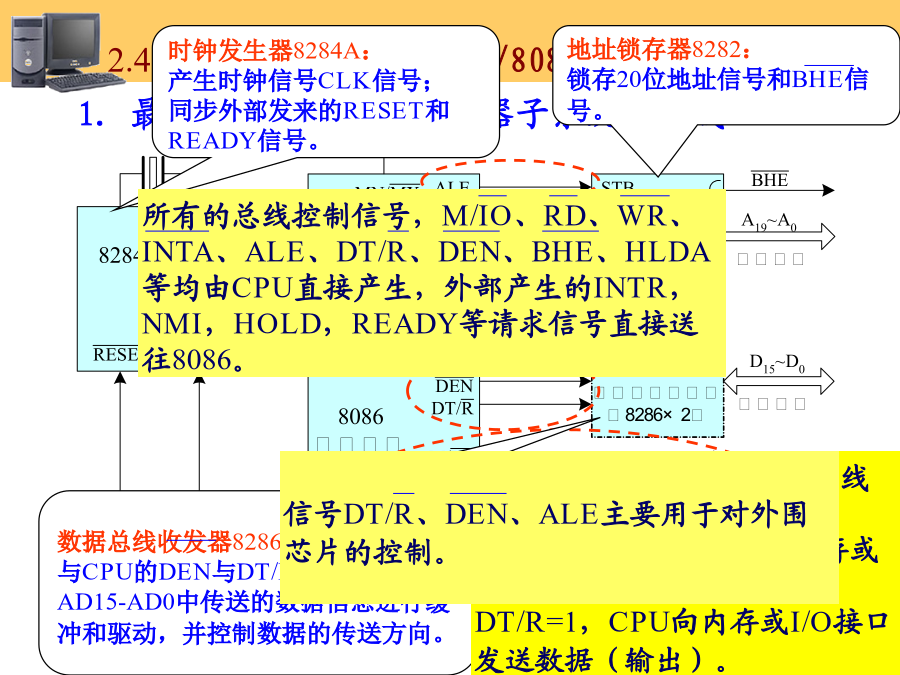

2.48086/8088微处理器子系统2.48086/8088微处理器子系统图1-78086微处理器的封装外形按传输方向划分,CPU引脚信号有以下几种类型:输出:信号从CPU向外部传送;输入:信号从外部送入CPU;双向:信号有时从外部送入CPU,有时从CPU向外部传送;1、地址与数据信号引脚(1)AD15~AD0(AddressDataBus)(2)A19/S6~A16/S3(Address/Status)2、读写控制信号引脚读写控制信号用来控制CPU对存储器和I/O接口的读写过程:数据传输方向(读/写)

Pentium微处理器引脚信号及功能.doc

Pentium微处理器引脚信号及功能Pentium微处理器引脚信号及功能Pentium微处理器引脚信号及功能Pentium微处理器引脚信号及功能Pentium微处理器采用PGA封装形式,共有237个引脚信号,其中包括29个地址引脚信号,64个数据引脚信号,75个控制引脚信号,69个VCC、VSS和NC空脚。Pentium微处理器的引脚信号如图所示.按功能可分为地址总线、数据总线和控制总线三大类。其中控制总线又分为总线周期定义、总线控制、总线仲裁、高速缓存、中断、错误检测和系统管理模式等引脚信号。1.时钟信

Pentium微处理器引脚信号及功能.doc

Pentium微处理器引脚信号及功能Pentium微处理器引脚信号及功能Pentium微处理器引脚信号及功能Pentium微处理器引脚信号及功能Pentium微处理器采用PGA封装形式,共有237个引脚信号,其中包括29个地址引脚信号,64个数据引脚信号,75个控制引脚信号,69个VCC、VSS和NC空脚。Pentium微处理器的引脚信号如图所示.按功能可分为地址总线、数据总线和控制总线三大类。其中控制总线又分为总线周期定义、总线控制、总线仲裁、高速缓存、中断、错误检测和系统管理模式等引脚信号。1.时钟信

x微处理器引脚功能与总线时序.pptx

会计学2345678910111213141516171819202122232425262728293031323334353637作业

x微处理器引脚功能与总线时序.pptx

会计学2345678910111213141516171819202122232425262728293031323334353637作业