systemVerilog快速入门ppt课件.ppt

lj****88

亲,该文档总共125页,到这已经超出免费预览范围,如果喜欢就直接下载吧~

相关资料

systemVerilog快速入门ppt课件.ppt

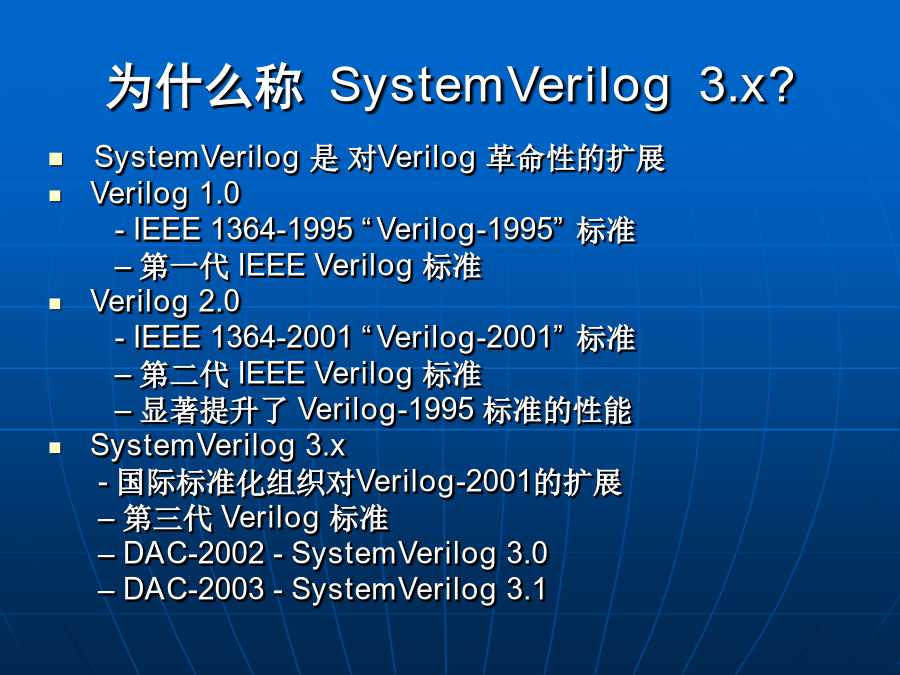

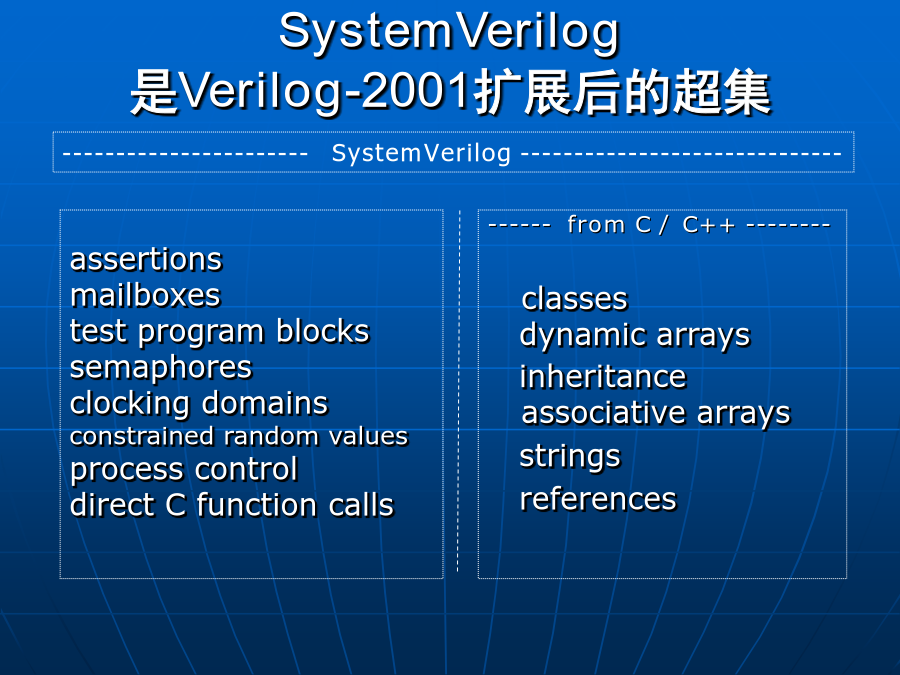

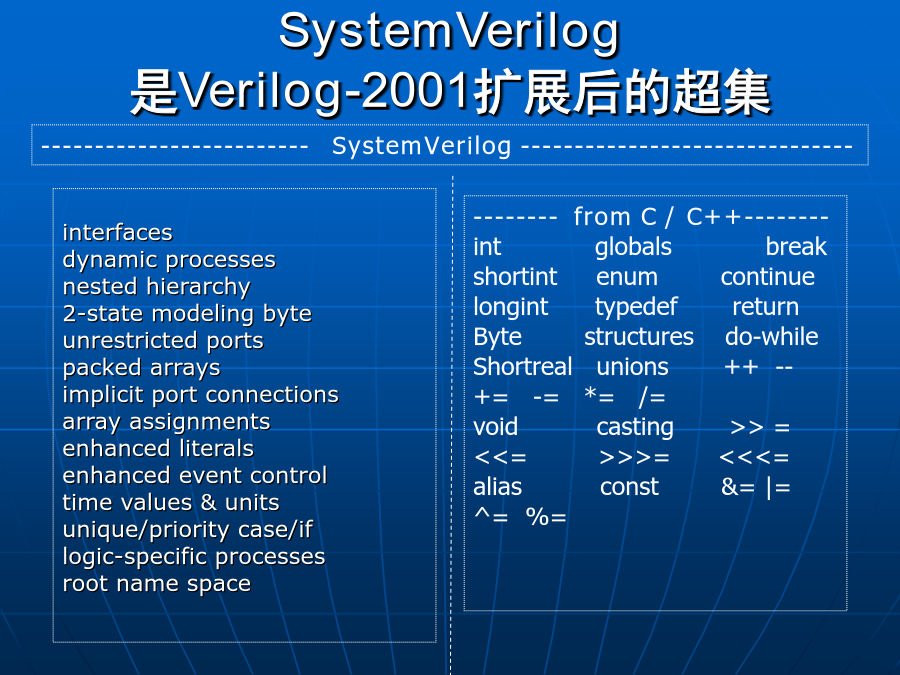

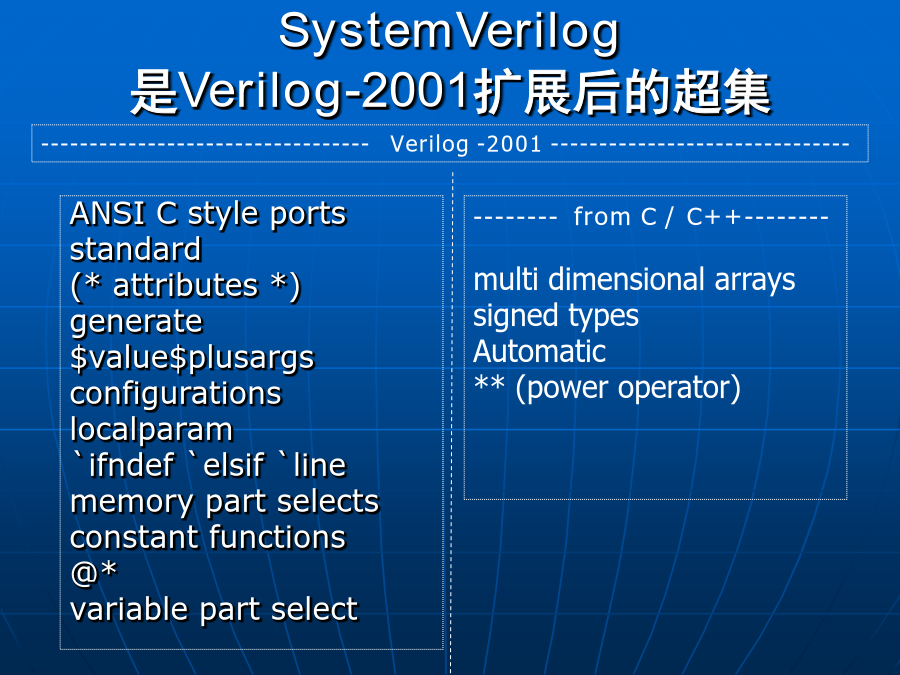

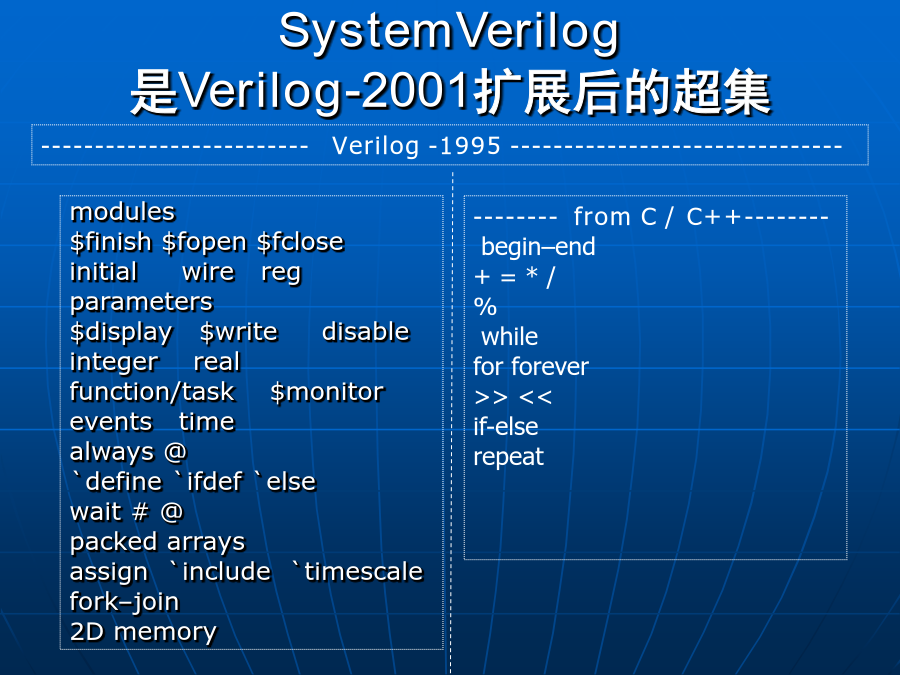

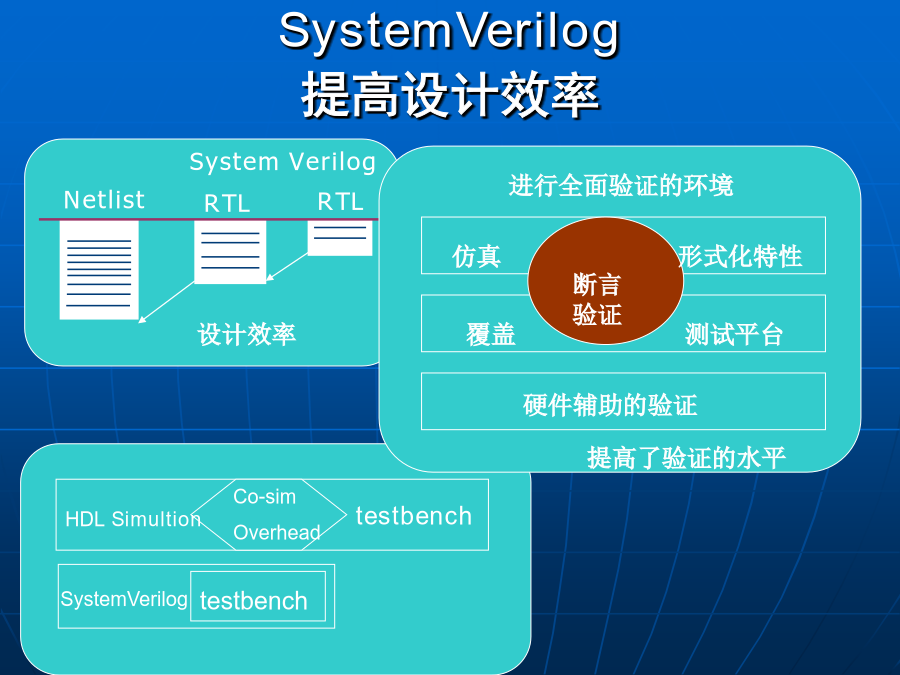

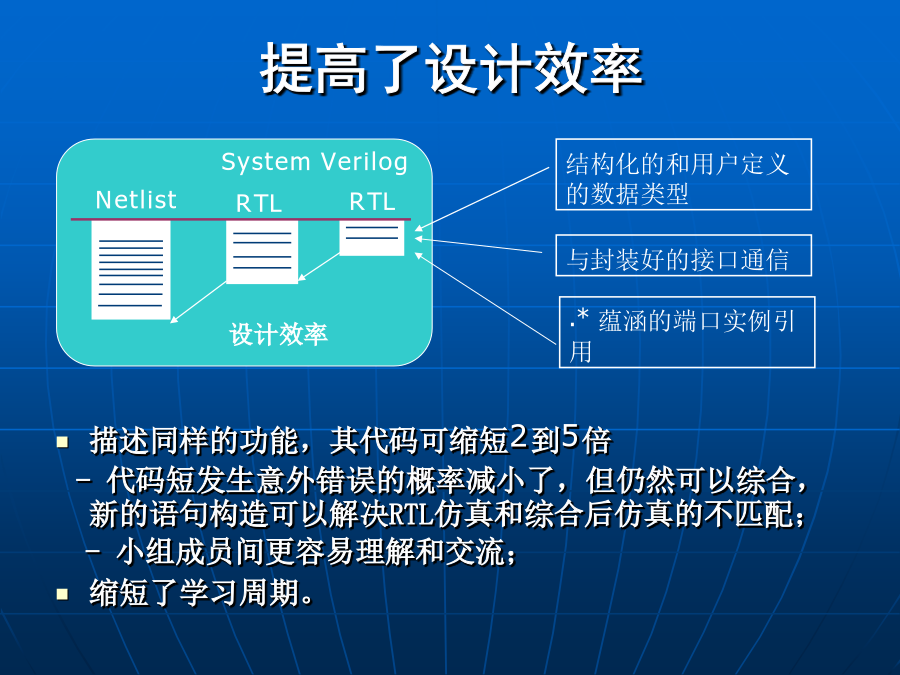

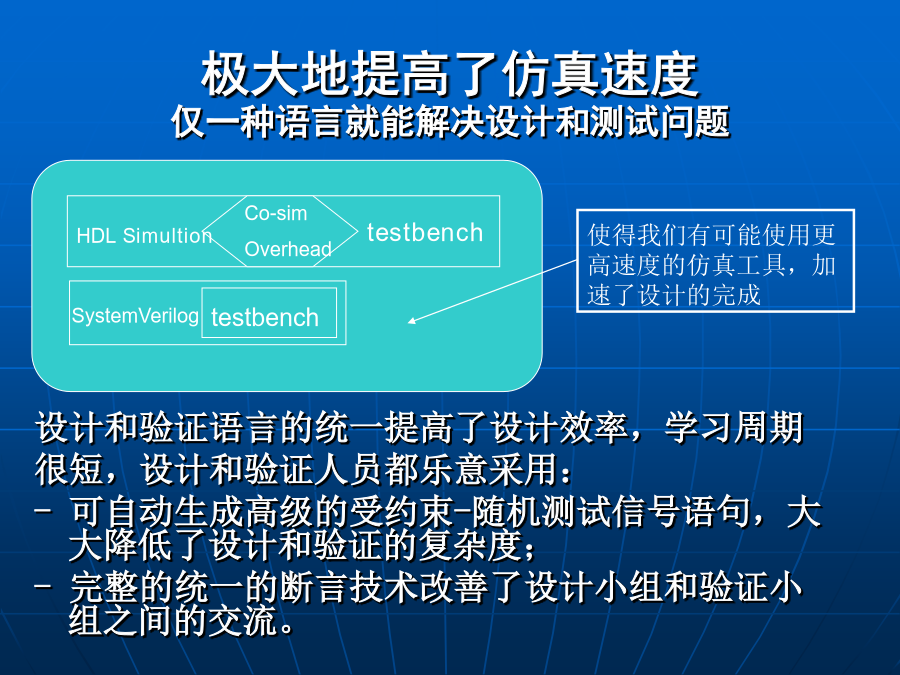

SystemVerilog讲座VerilogHDL的发展历史为什么称SystemVerilog3.x?SystemVerilog是Verilog-2001扩展后的超集SystemVerilog是Verilog-2001扩展后的超集SystemVerilog是Verilog-2001扩展后的超集SystemVerilog是Verilog-2001扩展后的超集SystemVerilog提高设计效率提高了设计效率极大地提高了仿真速度仅一种语言就能解决设计和测试问题SyestemVerilog的全面验证和设计Sy

CANoe快速入门ppt课件.ppt

CANoe快速入门CANoe概述CANoe在总线开发中的作用(1)CANoe在总线开发中的作用(2)CANoe在总线开发中的作用(3)硬件接口卡&“狗”CANcardXLCANcaseXL收发器CANcab(CANpiggy)251,1041,1054…LINcab(LINpiggy)7259CANoe组成CANoe工程环境多总线设置(1)设置(2)灵活=复杂从复杂到简单基本术语——报文(消息)与信号基本术语——环境变量与系统变量欢迎进入CANoe的世界欢迎进入CANoe的世界CANoe窗口介绍(1)蒙太

python快速入门ppt课件.ppt

Python快速入门教程该文档主要讲解内容Python是什么?Python和c++的区别Python的语法基础Python的数据类型:Python具有列表(list)、元组(tuple)和字典(dictionaries)三种基本的数据结构,而集合(sets)则包含在集合库中(但从Python2.5版本开始正式成为Python内建类型)。列表的特点跟一维数组类似(当然你也可以创建类似多维数组的“列表的列表”),字典则是具有关联关系的数组(通常也叫做哈希表),而元组则是不可变的一维数组(Python中“数组”

Flash快速入门PPT课件.ppt

Flash应用快速入门一、Flash工作界面二、Flash要素三、Flash文件名四、Flash动画分类五、Flash使用要点3.如何预演动画4.元件的建立和使用5.如何改变帧频六、Flash制作示例示例1:逐帧动画示例2:(直线)运动补间动画示例3:沿轨迹运动动画示例4:变形补间动画示例5:配有声音的动画示例6:按钮的使用

VHDL快速入门PPT课件.ppt

习题参考答案习题参考答案习题参考答案习题参考答案习题参考答案1-19输入A、B、C、D是一个十进制数X的8421BCD码,当X为奇数时,输出Y为1,否则Y为0。1-19输入A、B、C、D是一个十进制数X的8421BCD码,当X为奇数时,输出Y为1,否则Y为0。数字逻辑硬件描述语言VHDL基础VHDL程序基本结构VHDL程序设计基本结构VHDL主要用于描述设计系统的结构、行为、功能和接口。一、信号(signal)的含义和信号的两种最常用类型:std_logic和std_logic_vector库(libra