SoC芯片中RISC CPU的验证方法研究与实现.docx

快乐****蜜蜂

在线预览结束,喜欢就下载吧,查找使用更方便

相关资料

SoC芯片中RISC CPU的验证方法研究与实现.docx

SoC芯片中RISCCPU的验证方法研究与实现一、概述在现代计算机体系结构中,RISC(ReducedInstructionSetComputing,精简指令集计算机)和CISC(ComplexInstructionSetComputing,复杂指令集计算机)是两种不同的CPU架构方式。与CISC相比,RISC指令集精简、指令短小且功能单一,因此有更高的时钟频率和执行效率,并且更容易设计和验证。SoC(SystemonChip,片上系统)芯片作为集成电路中的一种,其核心是集成了大量数字电路和模拟电路的单芯

金融卡SoC芯片中相关模块的设计实现及验证方法研究.docx

金融卡SoC芯片中相关模块的设计实现及验证方法研究金融卡SoC芯片是在金融领域应用的芯片,具有安全性要求高、处理能力强和功耗低等特点。对于金融卡SoC芯片,其设计实现及验证方法的研究是非常重要的。本文将探讨金融卡SoC芯片中相关模块的设计实现及验证方法。一、设计实现1.安全模块设计安全模块是金融卡SoC芯片中最重要的模块之一,用于保护用户的隐私和数据安全。设计安全模块时需要考虑以下几个方面:(1)安全算法的选择:选择合适的安全算法,如对称加密算法和非对称加密算法。需要根据具体的需求,权衡算法的加密强度和性

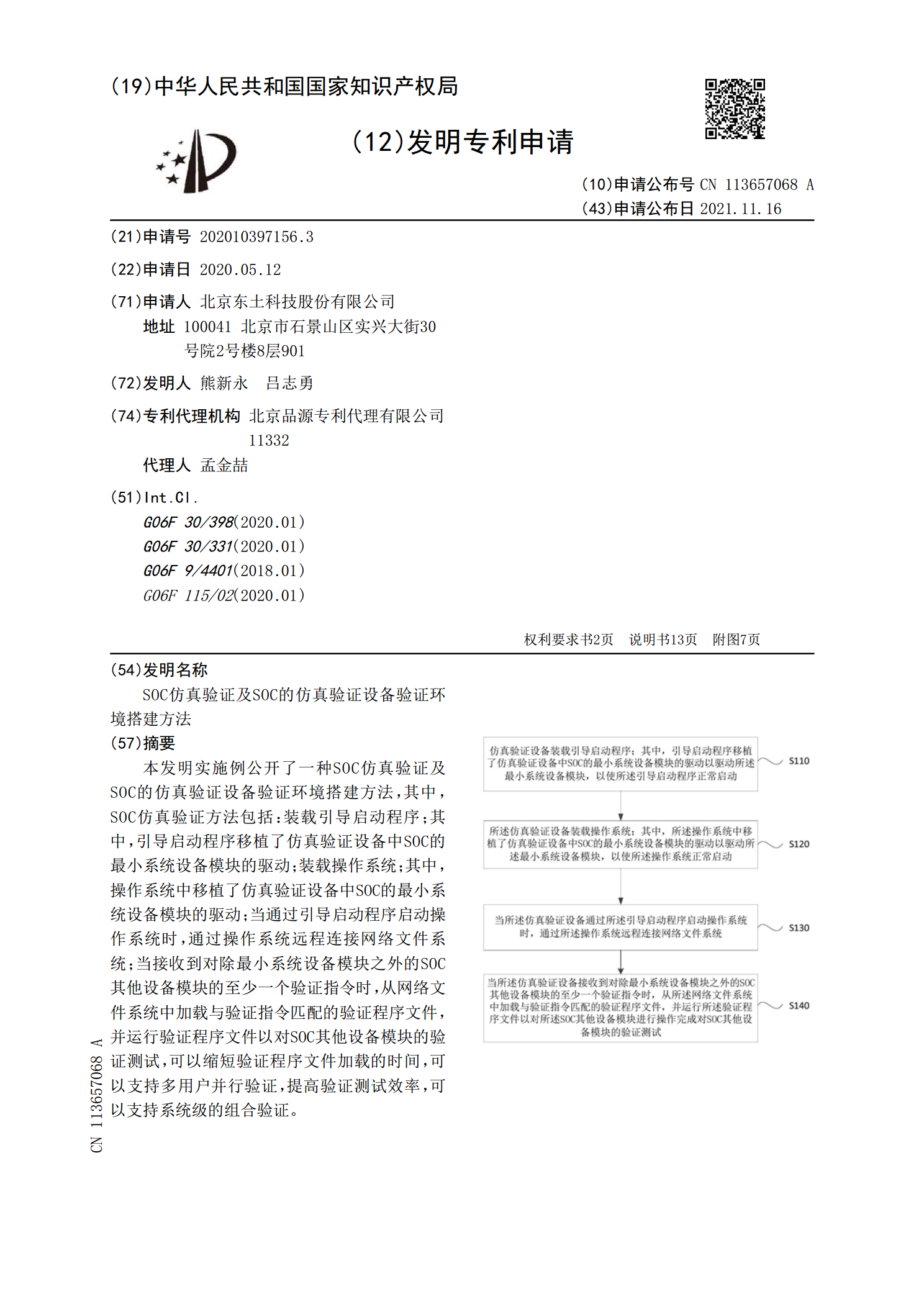

SOC仿真验证及SOC的仿真验证设备验证环境搭建方法.pdf

本发明实施例公开了一种SOC仿真验证及SOC的仿真验证设备验证环境搭建方法,其中,SOC仿真验证方法包括:装载引导启动程序;其中,引导启动程序移植了仿真验证设备中SOC的最小系统设备模块的驱动;装载操作系统;其中,操作系统中移植了仿真验证设备中SOC的最小系统设备模块的驱动;当通过引导启动程序启动操作系统时,通过操作系统远程连接网络文件系统;当接收到对除最小系统设备模块之外的SOC其他设备模块的至少一个验证指令时,从网络文件系统中加载与验证指令匹配的验证程序文件,并运行验证程序文件以对SOC其他设备模块的

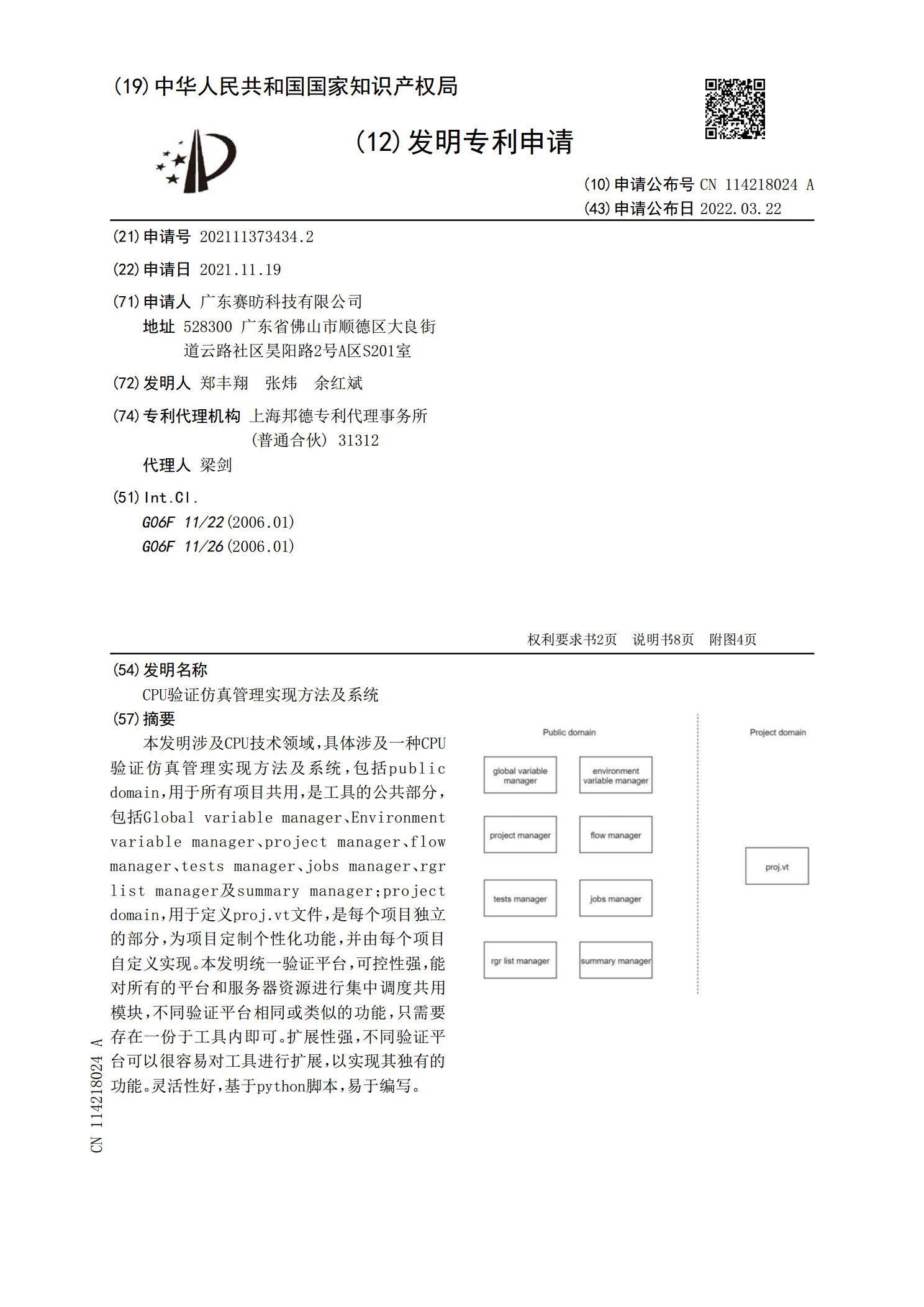

CPU验证仿真管理实现方法及系统.pdf

本发明涉及CPU技术领域,具体涉及一种CPU验证仿真管理实现方法及系统,包括publicdomain,用于所有项目共用,是工具的公共部分,包括Globalvariablemanager、Environmentvariablemanager、projectmanager、flowmanager、testsmanager、jobsmanager、rgrlistmanager及summarymanager;projectdomain,用于定义proj.vt文件,是每个项目独立的部分,为

从CPU到SoC的设计与实现读书随笔.docx

《从CPU到SoC的设计与实现》读书随笔一、关于CPU的设计与实现在阅读《从CPU到SoC的设计与实现》这本书的过程中,我对于CPU的设计与实现有了更深入的了解。CPU,即中央处理器,作为计算机系统的核心部件,其设计与实现的复杂性令人惊叹。CPU可以看作是执行程序指令的“大脑”。它由多个关键部分组成,包括控制器、运算器、寄存器等等。控制器负责协调各个部件的工作,运算器执行算术和逻辑运算,寄存器则存储数据和状态信息。CPU的设计是一个复杂而系统的过程。首先需要确定CPU的架构,这决定了CPU的性能和功能。设