物理时序逻辑电路学习教案.pptx

快乐****蜜蜂

亲,该文档总共118页,到这已经超出免费预览范围,如果喜欢就直接下载吧~

相关资料

物理时序逻辑电路学习教案.pptx

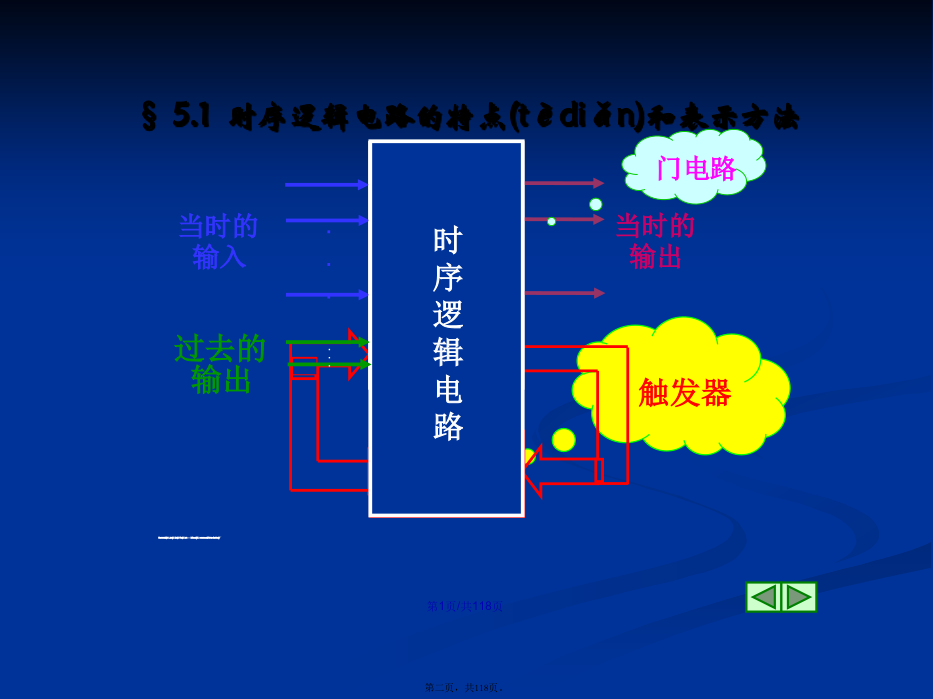

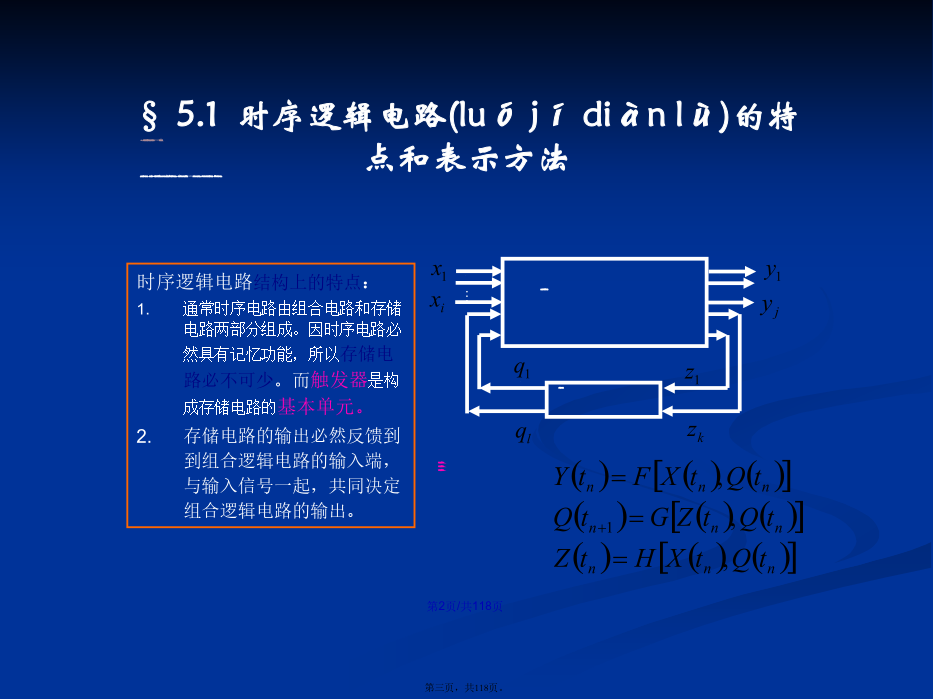

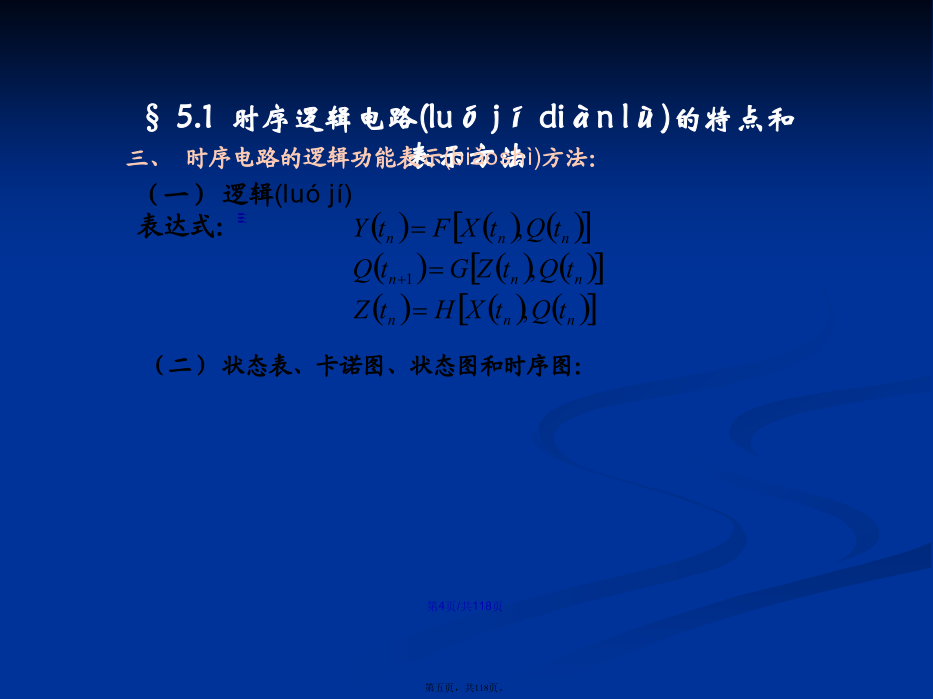

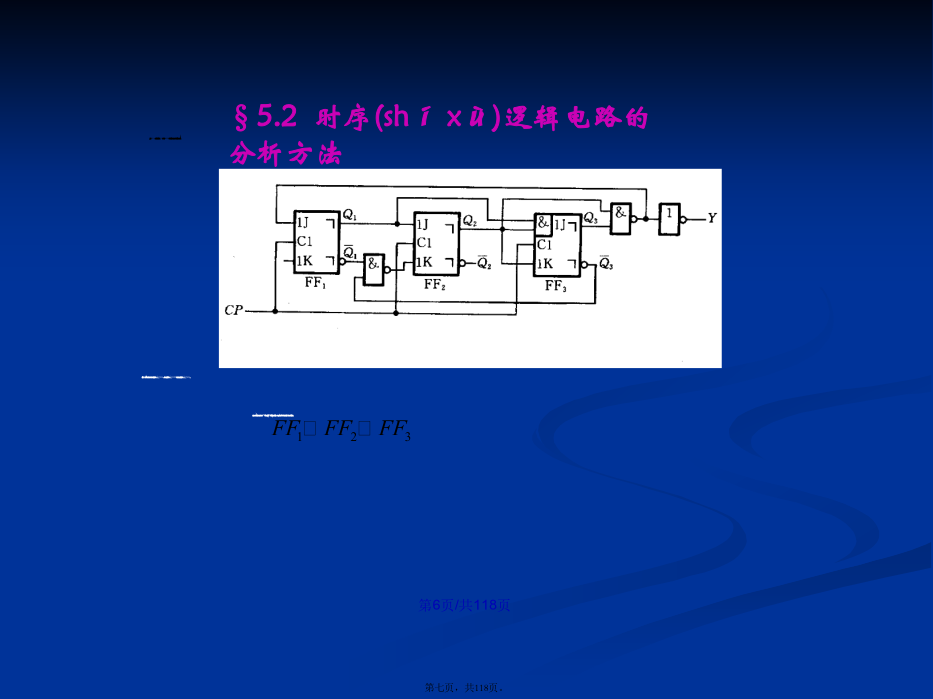

会计学一、时序逻辑电路的特点(tèdiǎn)和框图根据记忆电路中存储(cúnchǔ)单元状态变化的特点将时序电路分为同步时序电路:所有存储(cúnchǔ)电路中存储(cúnchǔ)单元状态的变化都是在同一时钟信号操作下同时发生的。异步时序电路:存储(cúnchǔ)单元状态的变化不是同时发生的。可能有公共的时钟信号,也可能没有公共的时钟信号。按照输出信号的不同,分为:米利(Mealy)型电路:某时刻的输出是该时刻的输入和电路状态的函数莫尔(Moore)型电路:某时刻的输出仅是该时刻电路状态的函数,与该时刻的

物理异步时序逻辑电路学习教案.pptx

物理(wùlǐ)异步时序逻辑电路脉冲(màichōng)异步时序逻辑电路脉冲异步时序逻辑电路(luójídiànlù)的分析例分析图所示脉冲异步时序逻辑电路(luójídiànlù),指出电路功能。脉冲异步时序逻辑电路(luójídiànlù)的设计D触发器激励(jīlì)表J-K触发器激励(jīlì)表T触发器R-S触发器激励(jīlì)表电平异步时序(shíxù)逻辑电路输入(shūrù)信号的约束电平(diànpínɡ)异步时序电路的分析电平(diànpínɡ)异步时序逻辑电路的竞争

时序逻辑电路学习教案.pptx

会计学6.1概述组合逻辑电路:t时刻输出仅与t时刻输入有关,与t以前的状态无关。X——外部输入Y——外部输出Z——触发器的控制输入Q——触发器的状态输出2、从电路结构上看7891011121314151617181920212223242526272829303132333435363738394041424344454647484950515253545556575859606162636465666768697071727374757677787980818283848586

时序逻辑电路57502学习教案.pptx

会计学寄存器及移位(yíwèi)寄存器数字逻辑电路电子教案西北大学(xīběidàxué)信息学院数字逻辑电路(luójídiànlù)电子教案西北大学信息学院数字逻辑电路电子教案西北大学信息(xìnxī)学院数字逻辑电路电子教案(jiàoàn)西北大学信息学院数字逻辑电路(luójídiànlù)电子教案西北大学信息学院数字(shùzì)逻辑电路电子教案西北大学信息学院数字逻辑电路电子教案(jiàoàn)西北大学信息学院数字逻辑电路(luójídiànlù)电子教案西北大学信息学院数字逻辑电路(luój

时序逻辑电路14学习教案.pptx

时序(shíxù)逻辑电路14本章学习(xuéxí)目标14.1时序逻辑电路(luójídiànlù)概述时序逻辑电路(luójídiànlù)的概念14.2寄存器寄存器的功能(gōngnéng):存储数码或信息。并行(bìngxíng)输入、并行(bìngxíng)输出寄存器n位二进制数是同时输入(shūrù)到寄存器的输入(shūrù)端,在输出端同时得到n位二进制输出数据。因此称为并行输入(shūrù)、并行输出寄存器。移位(yíwèi)寄存器工作(gōngzuò)过程:2.左移寄存器4位左移寄存器