超深亚微米工艺下时钟网格的研究与设计任务书.docx

骑着****猪猪

在线预览结束,喜欢就下载吧,查找使用更方便

相关资料

超深亚微米工艺下时钟网格的研究与设计任务书.docx

超深亚微米工艺下时钟网格的研究与设计任务书任务书:超深亚微米工艺下时钟网格的研究与设计一、任务背景随着集成化电路技术的发展,芯片上集成器件的数量越来越多,被集成的电路复杂度也越来越高。由于集成度的提高,芯片的绘制精度也提高了,因此,超深亚微米工艺也逐渐被广泛应用。在超深亚微米工艺下,时钟网格的设计应用成为了一项非常关键的工作,而其中关键的任务之一就包括了时钟信号的分布、延迟控制、噪声防护等,在此情况下,通过研究和设计时钟网格可以进一步优化电路的时序性能和噪声干扰抑制效果。二、任务要求1、了解各类常见工艺下

微米、亚微米及深亚微米CMOS工艺技术研究.docx

微米、亚微米及深亚微米CMOS工艺技术研究微米、亚微米及深亚微米CMOS工艺技术研究摘要:随着集成电路技术的不断发展,微米、亚微米及深亚微米CMOS工艺技术逐渐成为研究的热点。本论文主要对微米、亚微米及深亚微米CMOS工艺技术进行了综述和分析。首先,论文介绍了微米、亚微米及深亚微米CMOS工艺技术的背景和意义。然后,论文重点介绍了微米、亚微米及深亚微米CMOS工艺技术的发展历程和目前的研究进展。最后,论文对微米、亚微米及深亚微米CMOS工艺技术的挑战和前景进行了展望。关键词:微米、亚微米、深亚微米、CMO

超深亚微米工艺下模拟IC仿真的MOSFET模型.pdf

!"#$%&’%()!!)*&+$))-.!!"’$%/*0$"’*."%-123+"()-.超深亚微米工艺下模拟!"仿真的#$%&’(模型段成华柳美莲((((((中国科学院研究生院系统集

超深亚微米工艺下模拟IC仿真的MOSFET模型.pdf

!"#$%&’%()!!)*&+$),)-.!!"’$%/*0$"’*."%-123+"(,)-.超深亚微米工艺下模拟!"仿真的#$%&’(模型段成华,柳美莲(中国科学院研究生院系统集成中心,中国科学院研究生院电子学研究所,北京100049)摘要:对MOSFET器件特性、MOSFET建模方法和建模发展历程进行了回顾,分析了在模拟集成电路低功耗设计中比较流行的模型(BSIM和E./模型),对它们进行了比较,分析其各自的优点和缺点。结果表明获得能够精确地预测高性能模拟系统的模型是很困难的,而E./模型在模拟集

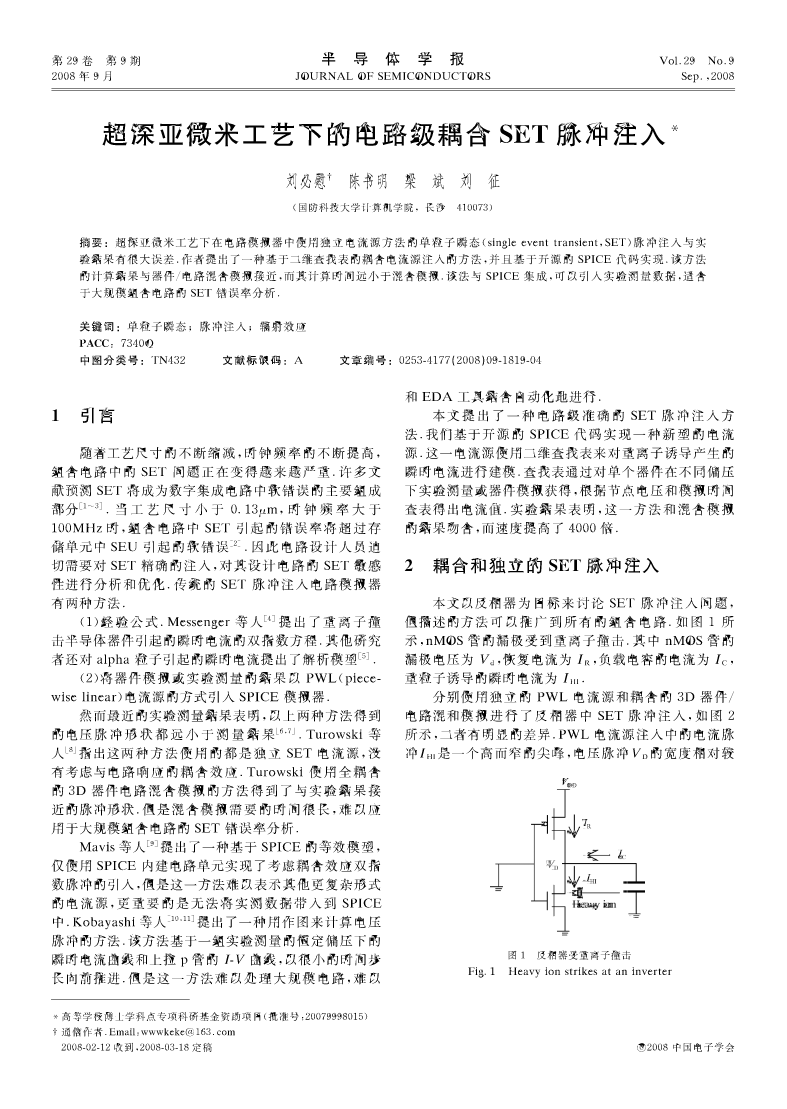

超深亚微米工艺下的电路级耦合SET脉冲注入1.pdf

第29卷第9期半导体学报犞狅犾.29犖狅.92008年9月犑犗犝犚犖犃犔犗犉犛犈犕犐犆犗犖犇犝犆犜犗犚犛犛犲狆.,2008超深亚微米工艺下的电路级耦合犛犈犜脉冲注入刘必慰陈书明梁斌刘征(国防科技大学计算机学院,长沙410073)摘要:超深亚微米工艺下在电路模拟器中使用独立电流源方法的单粒子瞬态(狊犻狀犵犾犲犲狏犲狀狋狋狉犪狀狊犻犲狀狋,犛犈犜)脉冲注入与实验结果有很大误差.作者提出了一种基于二维查找表的耦合电流源注入的方法,并且基于开源的犛犘犐犆犈代码实现.该方法的计算结果与器件/电路混合模拟接近,而