计算机组成原理试题集含答案(5).docx

一只****ng

亲,该文档总共20页,到这已经超出免费预览范围,如果喜欢就直接下载吧~

相关资料

计算机组成原理试题集含答案(5).docx

计算机组成原理试题集含答案第一章计算机系统概论计算机的硬件是由有形的电子器件等构成的,它包括运算器、存储器、控制器、适配器、输入输出设备。早起将运算器和控制器合在一起称为CPU(中央处理器)。目前的CPU包含了存储器,因此称为中央处理器。存储程序并按地址顺序执行,这是冯•诺依曼型计算机的工作原理,也是CPU自动工作的关键。计算机系统是一个有硬件、软件组成的多级层次结构,它通常由微程序级、一般程序级、操作系统级、汇编语言级、高级语言级组成,每一级上都能进行程序设计,且得到下面各级的支持。习题:4冯•诺依曼型

计算机组成原理试题集含答案.docx

《微机原理与接技术》习题答案一、单项选择题1、80486CPU进行算术和逻辑运算时,可处理的信息的长度为(D)。A、32位B、16位C、8位D、都可以2、在下面关于微处理器的叙述中,错误的是(C)。A、微处理器是用超大规模集成电路制成的具有运算和控制功能的芯片B、一台计算机的CPU含有1个或多个微处理器C、寄存器由具有特殊用途的部分内存单元组成,是内存的一部分D、不同型号的CPU可能具有不同的机器指令3、若用MB作为PC机主存容量的计量单位,1MB等于(B)字节。A、210个字节B、220个字节C、230

计算机组成原理试题集(含答案).pdf

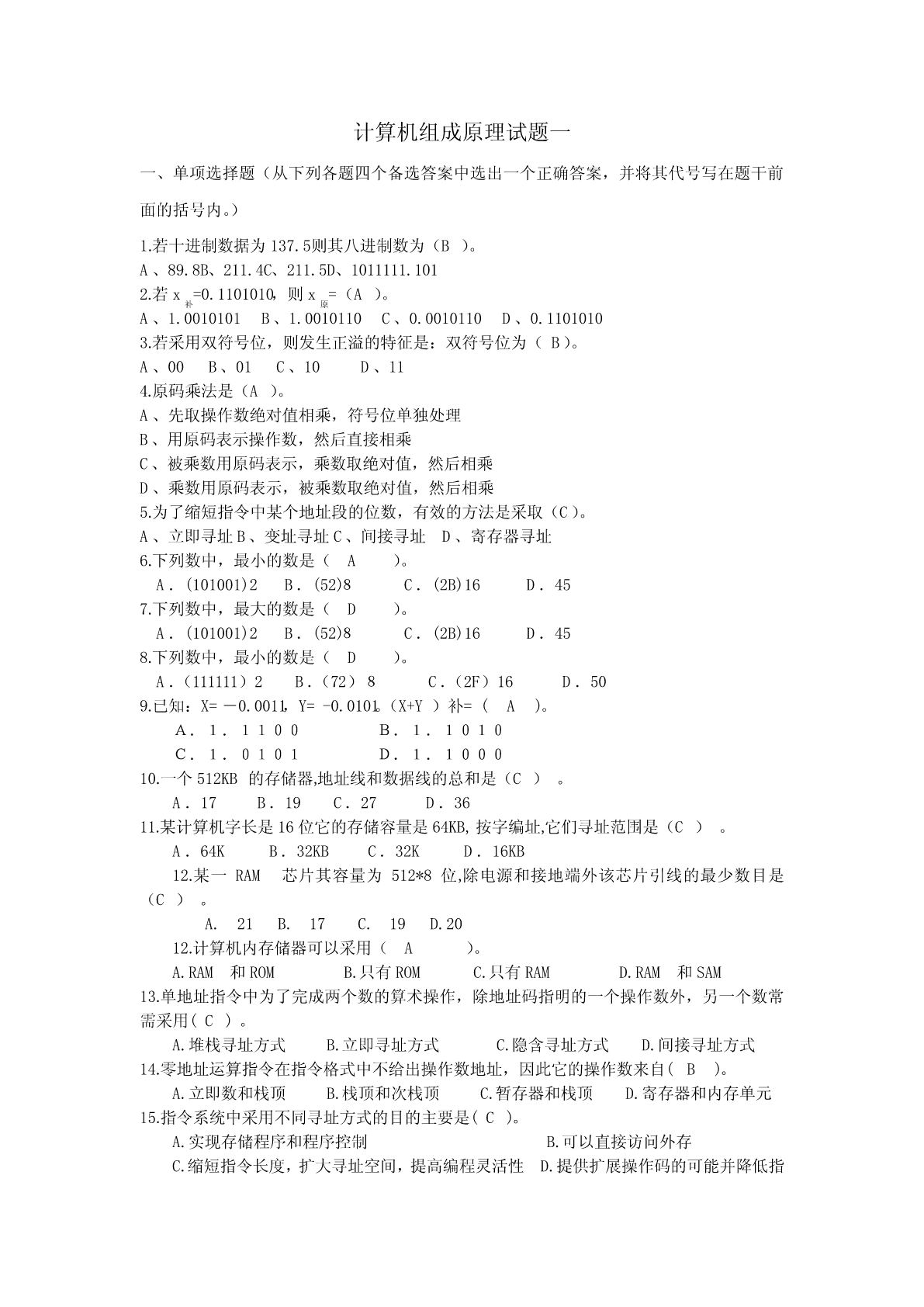

计算机组成原理试题一一、单项选择题(从下列各题四个备选答案中选出一个正确答案,并将其代号写在题干前面的括号内。)1.若十进制数据为137.5则其八进制数为(B)。A、89.8B、211.4C、211.5D、1011111.1012.若x=0.1101010,则x=(A)。补原A、1.0010101B、1.0010110C、0.0010110D、0.11010103.若采用双符号位,则发生正溢的特征是:双符号位为(B)。A、00B、01C、10D、114.原码乘法是(A)。A、先取操作数绝对值相乘,符号位单

计算机组成原理试题集含答案(4).docx

计算机组成原理试题集含答案三、问答题3、CPU中有哪些主要寄存器?简述这些寄存器的功能(至少5个)。3.解:(1)指令寄存器(IR):用来保存当前正在执行的一条指令。(2程序计数器(PC):用来确定下一条指令的地址。(3地址寄存器(AR):用来保存当前CPU所访问的内存单元的地址。(4缓冲寄存器(DR):<1>作为CPU和内存、外部设备之间信息传送的中转站。<2>补偿CPU和内存、外围设备之间在操作速度上的差别<3>在单累加器结构的运算器中,缓冲寄存器还可兼作为操作数寄存器。(5通用寄存器(AC):当运算

计算机组成原理试题集含答案(2).pdf

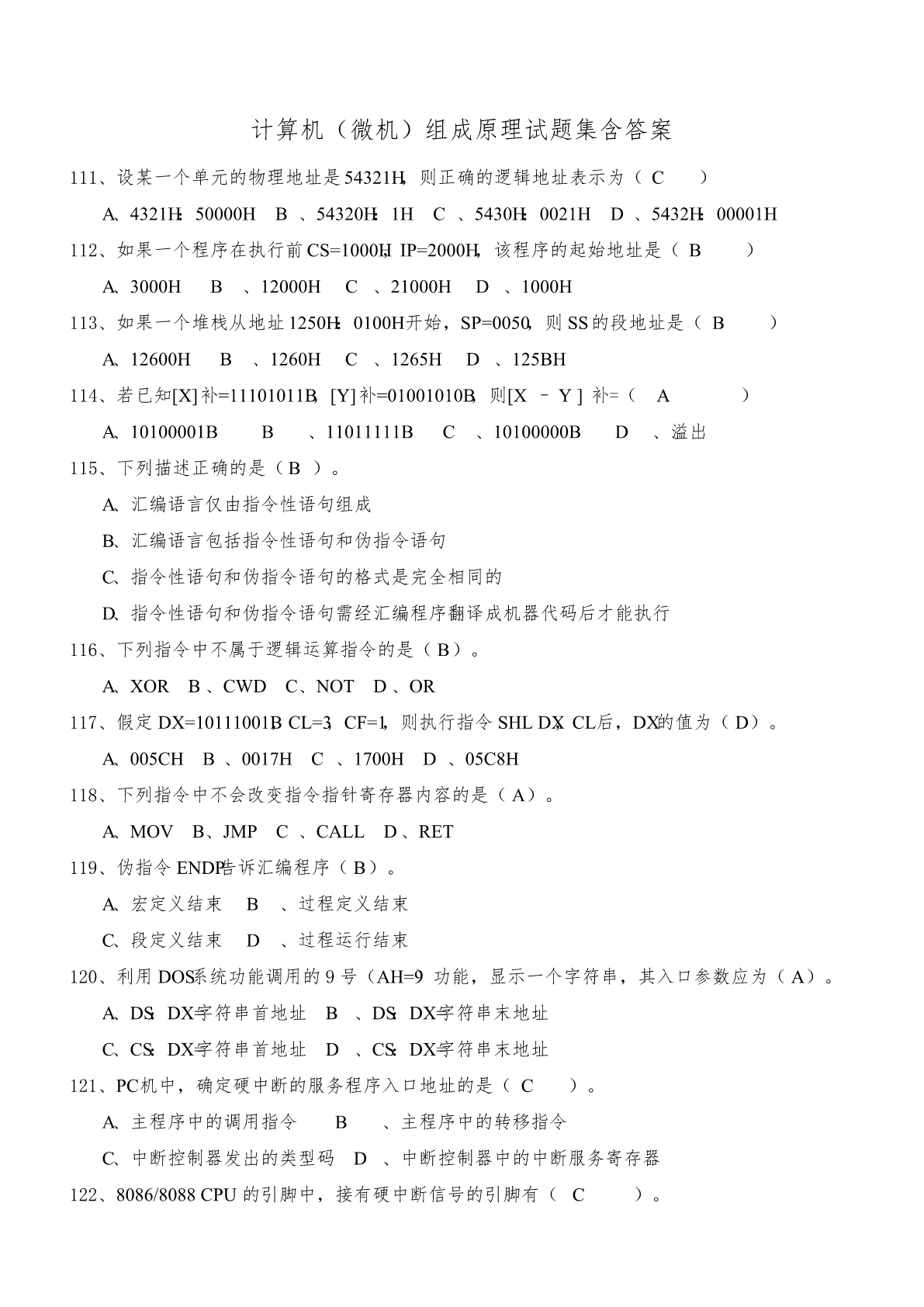

计算机(微机)组成原理试题集含答案111、设某一个单元的物理地址是54321H,则正确的逻辑地址表示为(C)A、4321H:50000HB、54320H:1HC、5430H:0021HD、5432H:00001H112、如果一个程序在执行前CS=1000H,IP=2000H,该程序的起始地址是(B)A、3000HB、12000HC、21000HD、1000H113、如果一个堆栈从地址1250H:0100H开始,SP=0050,则SS的段地址是(B)A、12600HB、1260HC、1265HD、125BH