基于28nm产品的缺陷分析及良率提升的开题报告.docx

骑着****猪猪

在线预览结束,喜欢就下载吧,查找使用更方便

相关资料

基于28nm产品的缺陷分析及良率提升的开题报告.docx

基于28nm产品的缺陷分析及良率提升的开题报告一、题目背景随着半导体工艺的不断提升,集成电路的产品也越来越先进。而在制造过程中,缺陷是难以避免的,对于28nm工艺的产品生产而言,如何对缺陷进行分析和控制是提高产品质量和生产效率的关键所在。二、研究目的本研究的目的主要是针对28nm工艺产品的缺陷进行分析,找出缺陷产生的原因,并提出可行的解决方案,以提高产品的良率。三、研究内容和方法1.对28nm工艺产品的缺陷进行分类和统计分析。通过扫描电镜等微观分析技术,对产品的缺陷进行分类和统计,以确定缺陷的种类、分布与

基于28NM工艺ASIC芯片的静态时序分析与优化的开题报告.docx

基于28NM工艺ASIC芯片的静态时序分析与优化的开题报告一、选题背景ASIC(ApplicationSpecificIntegratedCircuits)是指应用特定集成电路,是定制芯片,用于特定的应用中。ASIC芯片工艺的发展始终是IC技术创新的主线之一。目前,ASIC芯片在工业、军事、航空等领域中得到广泛应用,是电子信息技术领域重要的技术手段。ASIC芯片设计的关键在于时序分析和优化,如何保证电路中信号的传输满足特定的时序限制,是ASIC芯片设计过程中最关键的问题之一。针对这一问题,国内外学者对AS

40nm低功耗产品研发中SRAM的VMIN良率提升的开题报告.docx

40nm低功耗产品研发中SRAM的VMIN良率提升的开题报告一、选题背景和意义近年来,随着低功耗、高性能芯片需求的不断增加,SRAM在芯片中的应用越来越广泛。SRAM是一种存储器件,广泛用于高速缓存、寄存器和其他芯片中,占据了大量的面积和功耗。在SRAM制造过程中,最主要的失效模式是VMIN失效,即在噪声的干扰下,SRAM存储单元的电压会降低到一定程度,使得存储单元失效。因此,在SRAM设计和制造中,如何提高SRAM的VMIN良率,具有重要的意义。以40nm低功耗产品为例,SRAM的VMIN压降范围较大,

半导体产品的良率分析方法及良率分析系统.pdf

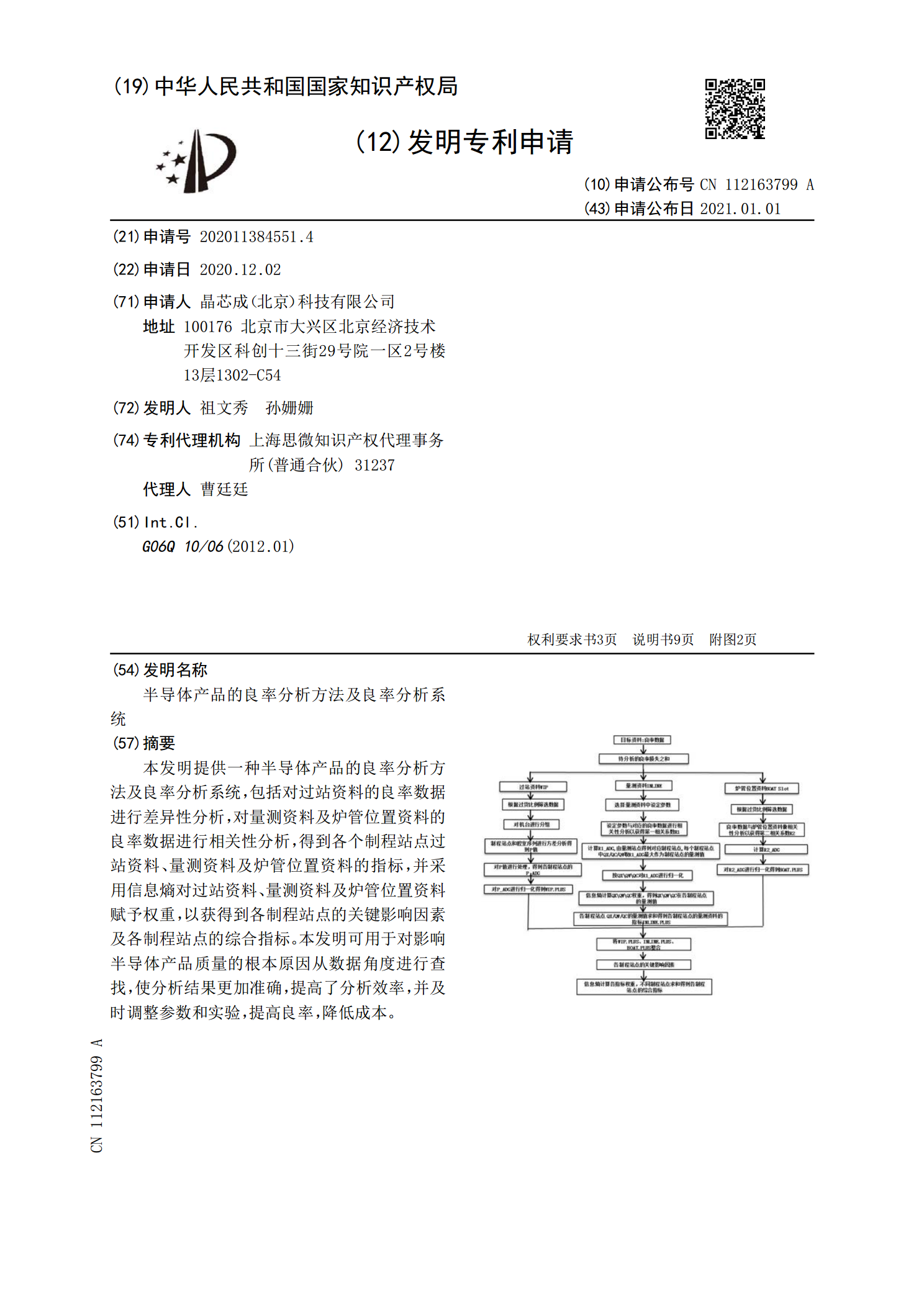

本发明提供一种半导体产品的良率分析方法及良率分析系统,包括对过站资料的良率数据进行差异性分析,对量测资料及炉管位置资料的良率数据进行相关性分析,得到各个制程站点过站资料、量测资料及炉管位置资料的指标,并采用信息熵对过站资料、量测资料及炉管位置资料赋予权重,以获得到各制程站点的关键影响因素及各制程站点的综合指标。本发明可用于对影响半导体产品质量的根本原因从数据角度进行查找,使分析结果更加准确,提高了分析效率,并及时调整参数和实验,提高良率,降低成本。

基于性能和良率提升的IC测试治具优化设计的开题报告.docx

基于性能和良率提升的IC测试治具优化设计的开题报告【摘要】IntegratedCircuit(IC)测试治具在IC制造过程中扮演着至关重要的角色,它可以为IC测试提供稳定的测试环境和高质量的测试数据。因此,测试治具的设计对IC制造的良率和性能提升至关重要。本文将从测试治具的优化设计出发,探讨如何在提高测试治具性能和良率的同时,降低测试治具成本和生产周期。【关键词】IC测试治具;优化设计;性能提升;良率提升;成本降低【正文】1.研究背景随着集成电路领域的不断发展,测试治具的功能要求也越来越高。测试治具不仅需